1.概述

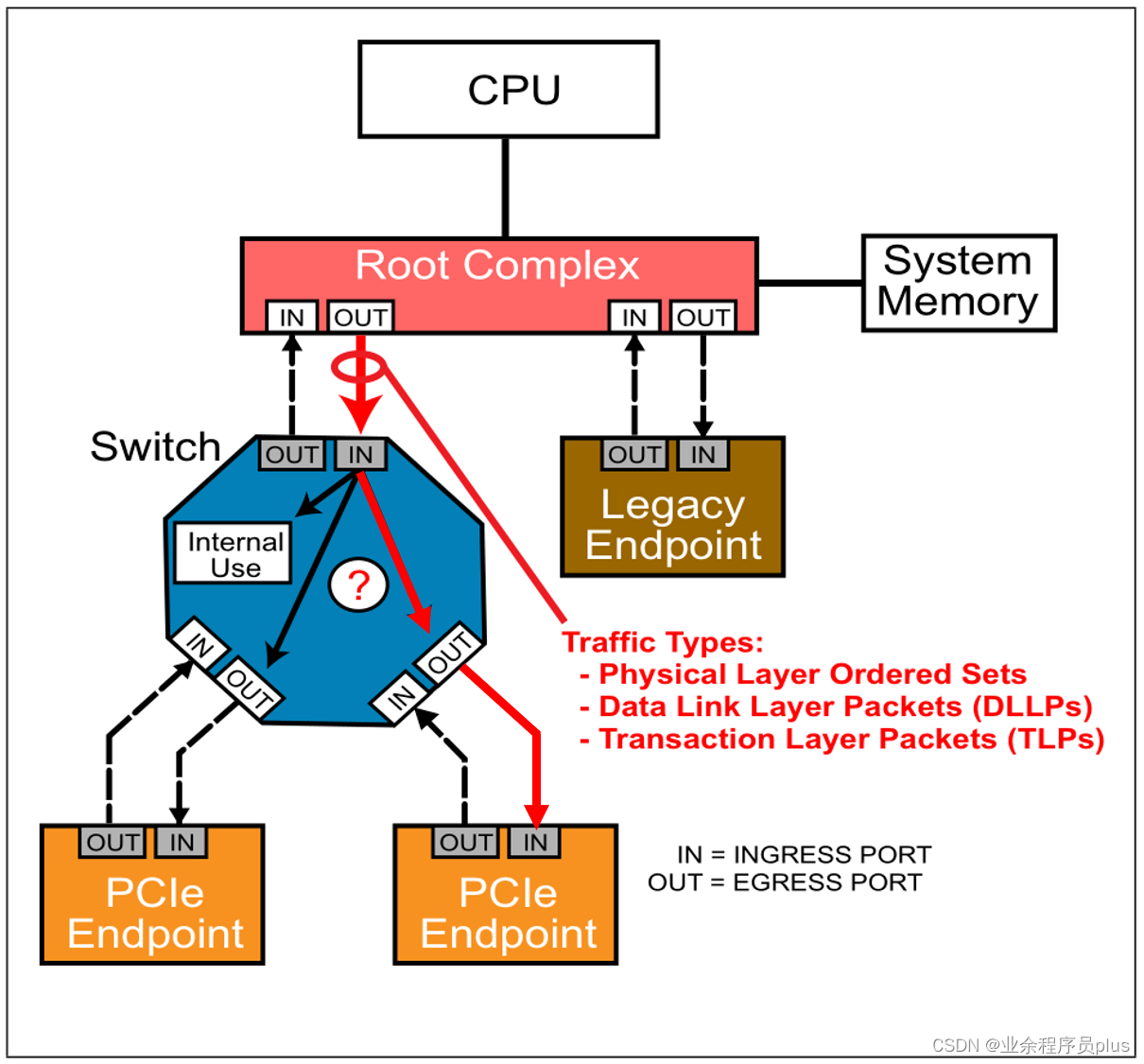

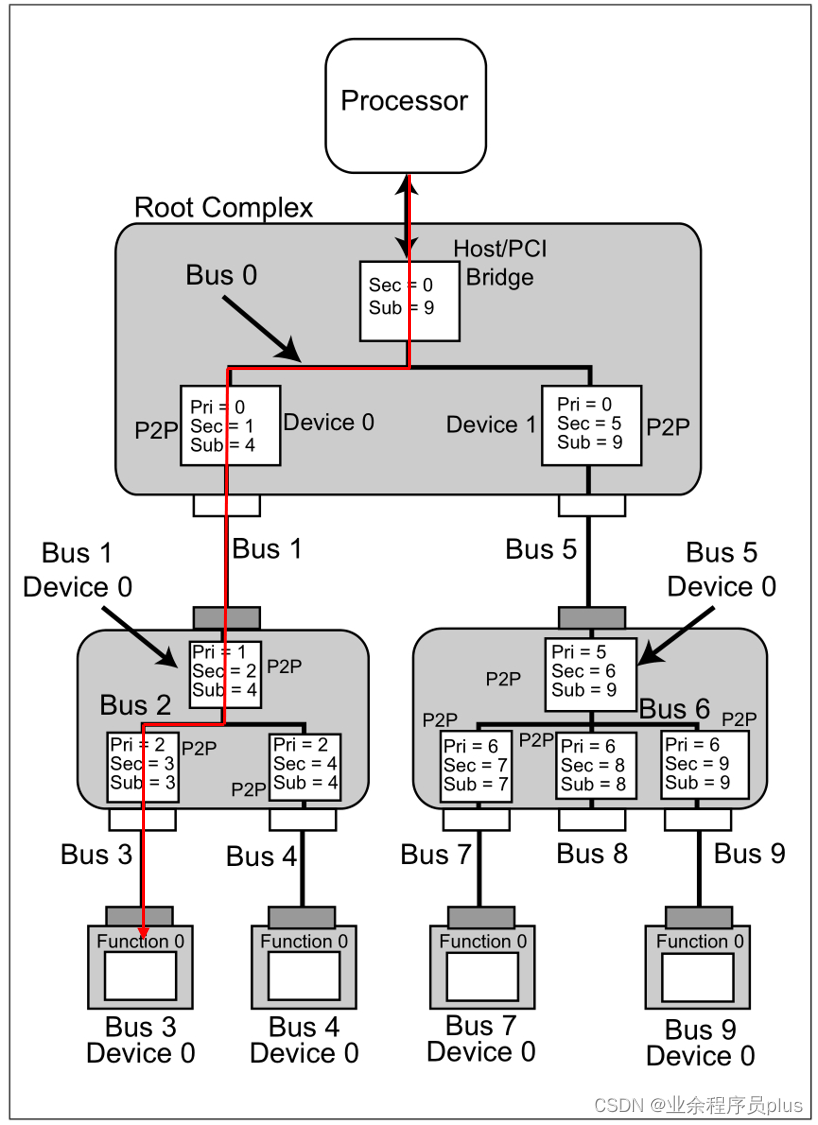

下图是一个PCIe总线系统示意图。此时RC发出一个TLP,经过Switch访问EP,TLP的路径为红色箭头所示。首先TLP从RC的下行OUT端口发出,Switch的上行IN端口接收到该TLP后,根据其路由信息,将其转发到Switch的下行OUT端口,随后TLP达到EP的IN端口,最后TLP到达EP设备。TLP从RC到EP的转发过程被称为TLP的路由过程。PCIe总线总共定义了三种路由方式,分别是基于地址(Address)路由、基于ID(BDF)路由和隐式(Implicit)路由。

TLP使用的路由方式和TLP的类型有关,具体如下表所示,PCIe桥就是根据这些信息转发TLP。

| TLP Type | Routing Method Used |

|---|---|

| Memory Read [Lock], Memory Write, AtomicOp | Address Routing |

| IO Read and Write | Address Routing |

| Configuration Read and Write | ID Routing |

| Message, Message With Data | Address Routing, ID Routing, or Implicit routing |

| Completion, Completion With Data | ID Routing |

2.地址路由(Address Routing)

存储器请求、原子操作、IO请求和某些消息请求使用地址路由。对于桥设备,地址路由和桥中设置的地址范围相关。对于EP设备,地址路由和BAR中保存的地址相关。根据传输方向,地址路由可以分为三种情况。第一种是RC Outbound,即RC访问其下游的桥或者EP设备,此时若访问地址在桥定义的地址范围内时,则桥会将该报文向下行口转发。第二种是RC Inbound,即EP(通常是使用DMA)访问RC,此时是下行口访问上行口,和第一种情况相反,只有访问地址不在桥定义的地址范围内时,桥才会将该报文向上行口转发。第三种是Peer-to-Peer,即EP之间相互访问,此时桥的处理方法综合第一种和第二种情况。

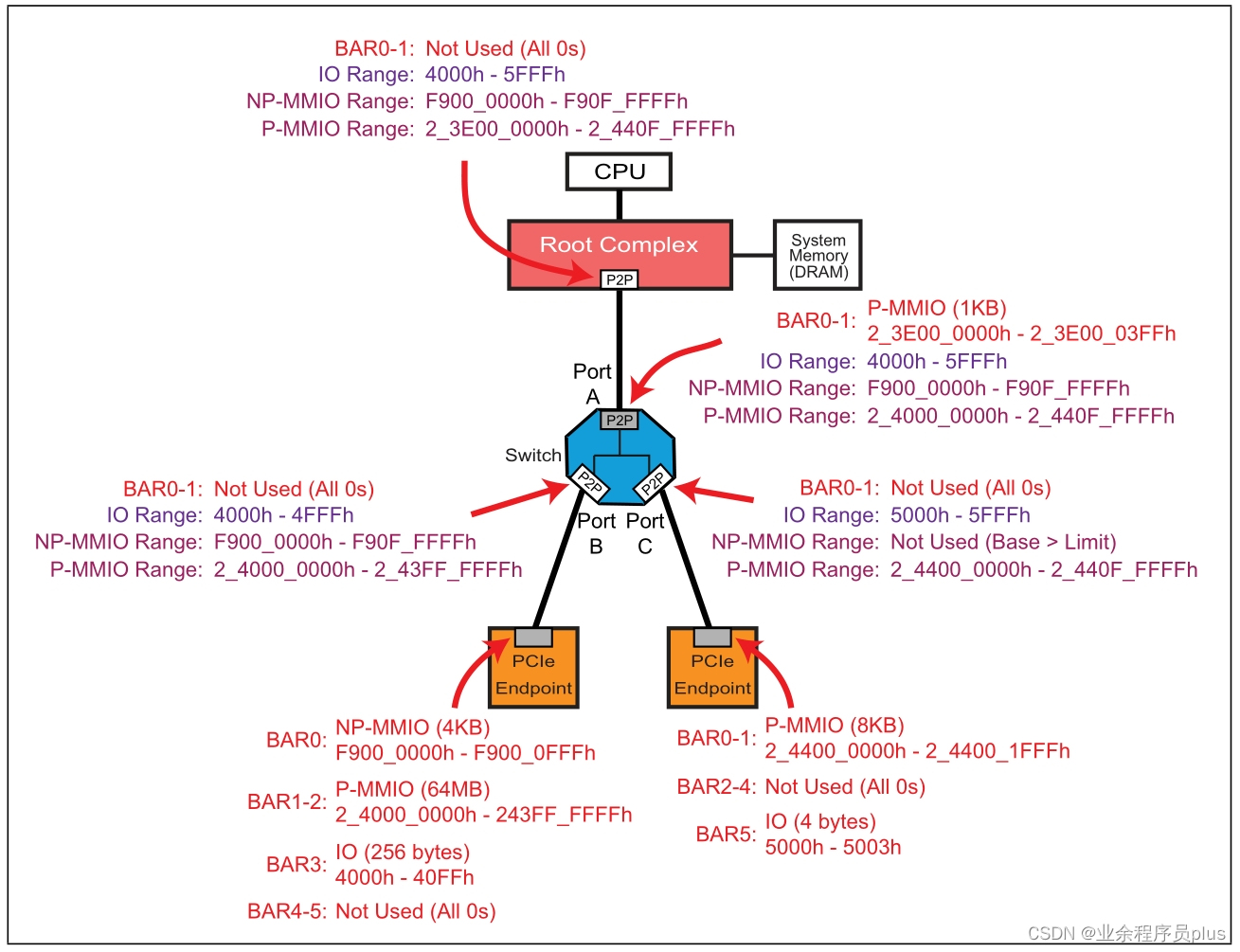

下图是一个PCIe总线,RC下面接了一个Switch,Switch两个下行口各接了一个EP。RC和Switch的每个Port都包含一个虚拟的PCI-toPCI(P2P)桥。该PCIe总线已枚举完成,分配的地址如下图所示。

IO地址、非预取存储器地址和预取存储器地址路由规则都一样,下面以预取存储器地址路由为例,介绍TLP的传输过程。下图包含了一个RC、一个Swtich和2个EP,Swtich有一个上行口和两个下行口。RC中的P2P0桥地址范围为0x240000000 -- 0x243FFFFFF,大小为64MB。Swtich上行口P2P1桥地址范围为0x240000000 -- 0x243FFFFFF,大小为64MB。Swtich下行口P2P2桥地址范围为0x240000000 -- 0x241FFFFFF,大小为32MB。Swtich下行口P2P3桥地址范围为0x242000000 -- 0x243FFFFFF,大小为32MB。EP0的BAR0和BAR1表示的地址范围为0x240000000 -- 0x241FFFFFF,大小为32MB。EP1的BAR0和BAR1表示的地址范围为0x242000000 -- 0x243FFFFFF,大小为32MB。下面将分别介绍TLP0、TLP1和TLP2的路由过程。

RC Outbound:TLP0由RC发出,访问EP0。流程如下:

- Host Bridge生成TLP0,目的地址为0x240008000,然后通过Bus0发送到RC内部的P2P0。

- P2P0解析TLP0的目的地址为0x240008000,在其0x240000000 -- 0x243FFFFFF地址范围内,则会接收这个TLP,然后将TLP0转发到Swtich的上行口。

- TLP0通过Swtich的上行口到达P2P1,P2P1解析TLP0的目的地址为0x240008000,在其0x240000000 -- 0x243FFFFFF地址范围内,则会将TLP0转发到Bus2上。若TLP0的目的地址不在P2P1的地址范围内时,则TLP0会被作为不支持的请求(Unsupported Request)处理,如果需要完成报文,则Swtich会发送完成状态为UR(Unsupported Request)的完成报文给RC。

- P2P2和P2P3都会收到TLP0,由于TLP0的目的地址在P2P2的地址范围内,因此P2P2会接收TLP0,然后将其转发到Bus3上,P2P3不会接收TLP0。

- EP0发现TLP0目的地址在BAR0和BAR1表示的地址范围内,则会接收该TLP0,反之则不会接收。

RC Inbound:TLP1由EP1发出,访问RC。流程如下:

- EP1生成TLP1,目的地址为0x24600C000,然后通过Bus4发送给Swtich的下行口。

- P2P3解析TLP1的目的地址为0x24600C000,不在其0x240000000 -- 0x243FFFFFF地址范围内,则P2P3会接收TLP1并将其向Bus2上转发。

- 当TLP1到达Bus2时,P2P2发现TLP1的目的地址不在其地址范围内,此时不会接收TLP1,随后TLP1会被P2P1转发到Bus1。

- P2P0发现TLP1的目的地址也不在其地址范围内,则会继续向Bus0上转发,此时Host Bridge会接收这个TLP,从而完成RC的访问。

Peer-to-Peer:TLP2由EP1发出,访问EP0。流程如下:

- EP1生成TLP2,目的地址为0x240004000,然后通过Bus4发送给Swtich的下行口。

- P2P3解析TLP1的目的地址为0x240004000,不在其0x240000000 -- 0x243FFFFFF地址范围内,则P2P3会接收TLP2并将其向Bus2上转发。

- 当TLP2到达Bus2时,P2P2发现TLP2的目的地址在其地址范围内,则会接收TLP2,然后将TLP2转发到Bus3上。当P2P1发现TLP2已被P2P2接收了,则不会再转发TLP2。

- EP0发现TLP2目的地址在BAR0和BAR1表示的地址范围内,则会接收该TLP2,反之则不会接收。

3.ID路由(ID Routing)

配置请求、完成报文和Vendor Defined消息报文使用ID路由。与地址路由不同,ID路由使用Bus Number、Device Number和Function Number组成的16位BDF进行寻址。

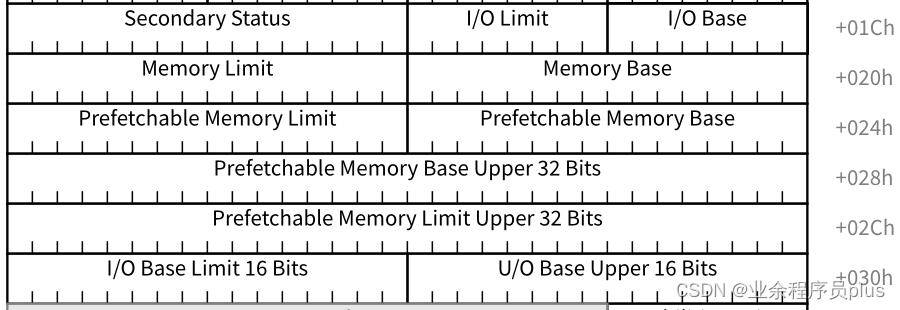

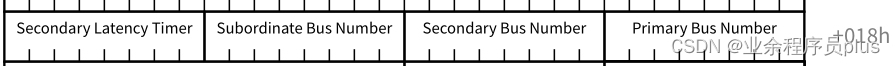

如下图所示,桥的配置空间中有三个和总线编号相关的寄存器。Primary Bus Number表示与桥相连的上游总线编号,Secondary Bus Number表示桥下游第一个总线编号,即桥下游最小的总线编号,Subordinate Bus Number表示桥下游最后一个总线编号,即桥下游最大的总线编号。这三个寄存器定义了桥的上游总线和下游总线编号范围,桥就是根据这些信息,进行ID路由。

下图是一个已经枚举完成的PCIe总线。Pri表示Primary Bus Number,Sec表示Secondary Bus Number,Sub表示Subordinate Bus Number,Device x表示Device Number,Function x表示Function Number。实质上,Device Number和Function Number已经由硬件确定。比如下图中3个Port的Swtich,上行口为Device 0,下行口从左到右依次为Device 1和Device 2,对于EP,由于只有一个设备,因此Device Number固定为0。设备有几个Function,则Function Number从0开始依次递增。

如下图所示,CPU通过RC访问Bus Number=3,Device Number=0,Function Number=0的设备。TLP通过Host Bridge被转发Bus0上,此时RC的两个下行口都会收到TLP,左边的P2P发现目的设备的总线号3在其下游总线编号1-4的范围内,因此会接收,并将其向下游总线转发,右边的P2P发现目的设备的总线号3不在其下游总线编号5-9的范围内,因此不会接收该TLP。与之类似,TLP最终会穿越左边的Swtich,到达要访问的设备。

4.隐式路由(Implicit routing)

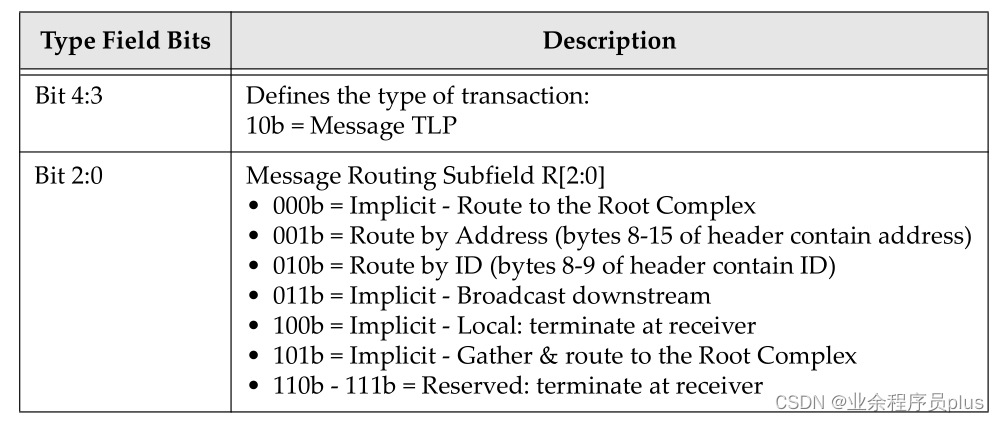

某些消息请求使用隐式路由,如INTx中断消息、电源管理消息和错误消息等。这些消息要么直接发向RC,要么是来自RC的广播报文,要么是Local: terminate at receiver。这些报文不使用地址或ID路由,而是使用Msg或MsgD报文中的Routing(Type[2:0])字段进行路由,这种路由方式称为隐式路由。如果桥收到一条使用隐式路由的TLP时,将根据Routing(Type[2:0])字段的不同而分别处理。若是收到了一条来自RC的广播消息,则会向下游转发,若是收到了一条发向RC的消息报文,则会向上游转发,若式收到了一条Local: terminate at receiver消息报文,则会接收并终结此消息报文,不会向上游或下游转发。

参考资料

- PCIEXPRESS体系结构导读

- PCI Express technology 3.0

- PCI Express® Base Specification Revision 5.0 Version 1.0