一、实验目的

-

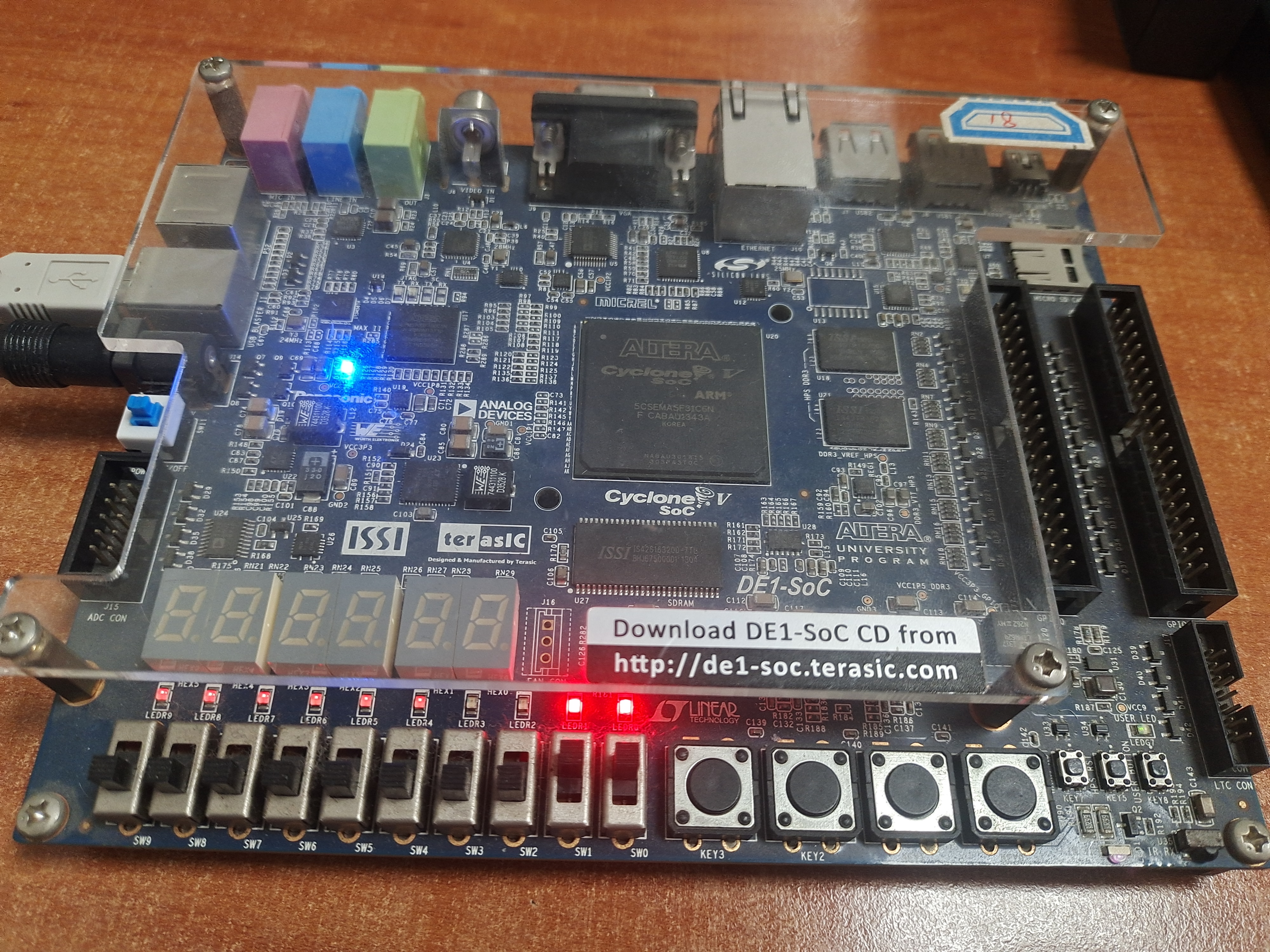

了解DE1-SOC开发板一些外设。

-

掌握常用组合逻辑门电路的基本原理。

-

学习Verilog HDL的基本语法。

-

学习使用ModelSim工具对设计的电路进行仿真,包括编写Testbench仿真代码,以及ModelSim工具的使用。

-

熟悉使用Quartus软件从创建Quartus工程到最终配置FPGA并观察实验现象的流程。

二、逻辑门电路介绍

逻辑门电路是数字电路中最基本的单元电路,是构成各种逻辑功能电路的基本电路。常用的逻辑门电路在逻辑功能上有与门、或门、非门、与非门、或非门、异或门。本实验主要介绍其中的与门、或门、非门和异或门。

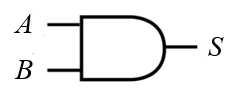

1. 与门

与门又称逻辑与电路,是执行与运算的基本逻辑门电路,有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

如下表1.1所示为二输入与门的真值表。

表1.1 二输入与门真值表

| 输入A | 输入B | 输出S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

下图所示为二输入与门逻辑符号。

以上二输入与门用逻辑运算表达式可表示为S = A&B,用Verilog HDL描述该与门的代码语句为:

assign S = A & B;2. 或门

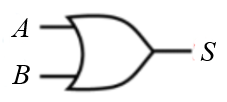

或门又称逻辑或电路。如果几个条件中,只要有一个条件得到满足,某事件就会发生,这种关系叫做或逻辑关系。或门有多个输入端,一个输出端,只要输入中有一个为高电平时(逻辑1),输出就为高电平(逻辑1);只有当所有的输入全为低电平(逻辑0)时,输出才为低电平(逻辑0)。

如下表1.2所示为二输入或门的真值表。

表1.2 二输入或门真值表

| 输入A | 输入B | 输出S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

下图所示为二输入或门逻辑符号。

以上二输入或门用逻辑运算表达式可表示为S = A + B,用Verilog HDL描述该或门的代码语句为:

assign S = A | B;3. 非门

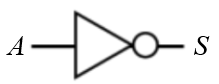

非门实现逻辑代数非的功能,即输出始终和输入保持相反。当输入端为高电平(逻辑1)时,输出端为低电平(逻辑0);反之,当输入端为低电平(逻辑0)时,输出端则为高电平(逻辑1)。

如下表1.3所示为非门的真值表。

表1.3 非门真值表

| 输入A | 输出S |

|---|---|

| 0 | 1 |

| 1 | 0 |

下图所示为非门逻辑符号。

非门用逻辑运算表达式可表示为S= ~A,用Verilog HDL描述该非门的代码语句为:

assign S = ~ A;4. 异或门

异或门是数字逻辑中实现逻辑异或的逻辑门,有多个输入端、一个输出端。若输入端的电平不同,则输出为高电平1;若输入端的电平都相同,则输出为低电平0。

如下表1.4所示为二输入异或门的真值表。

表1.4 异或门真值表

| 输入A | 输入B | 输出S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

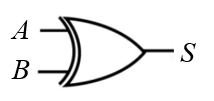

下图所示为二输入异或门逻辑符号。

以上二输入异或门用逻辑运算表达式可表示为S = A xor B ,用Verilog HDL描述该异或门的代码语句为:

assign S = A ^ B;也可以用以下代码语句表示:

assign S = (~A & B) | (A & ~B);三、逻辑门实验任务

设计并实现二输入与门、或门、异或门以及非门电路,两个操作数用DE1-SOC的滑动开关控制,并将该四个门电路的输出结果显示在DE1-SOC开发板的4个LED上,通过操作SW滑动开关观察LED相应的变化来验证所设计电路的正确性。

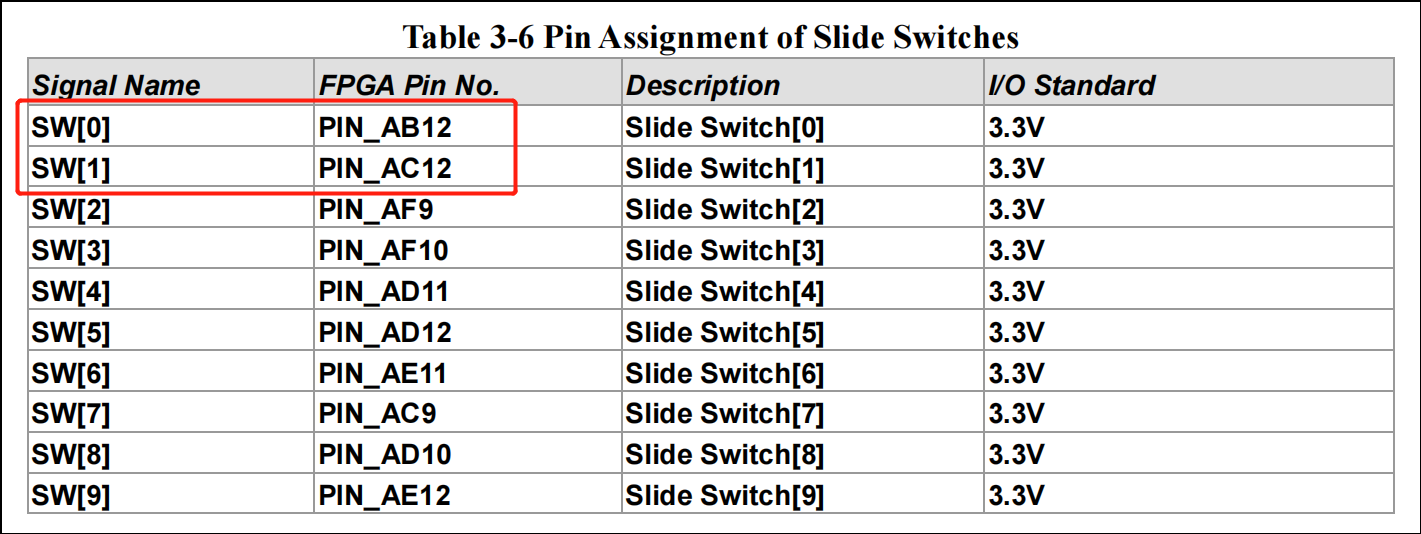

1. 硬件介绍

滑动开关

如下图所示,DE1-SOC开发板上有10个滑动开关,可在电路中用作电平触发的数据输入。每个滑动开关都连接到Cyclone V FPGA对应的一个引脚,当某个滑动开关拨到向上(up)的位置时,会产生一个高电平到FPGA;当拨到向下(down)的位置时,会产生一个低电平到FPGA。

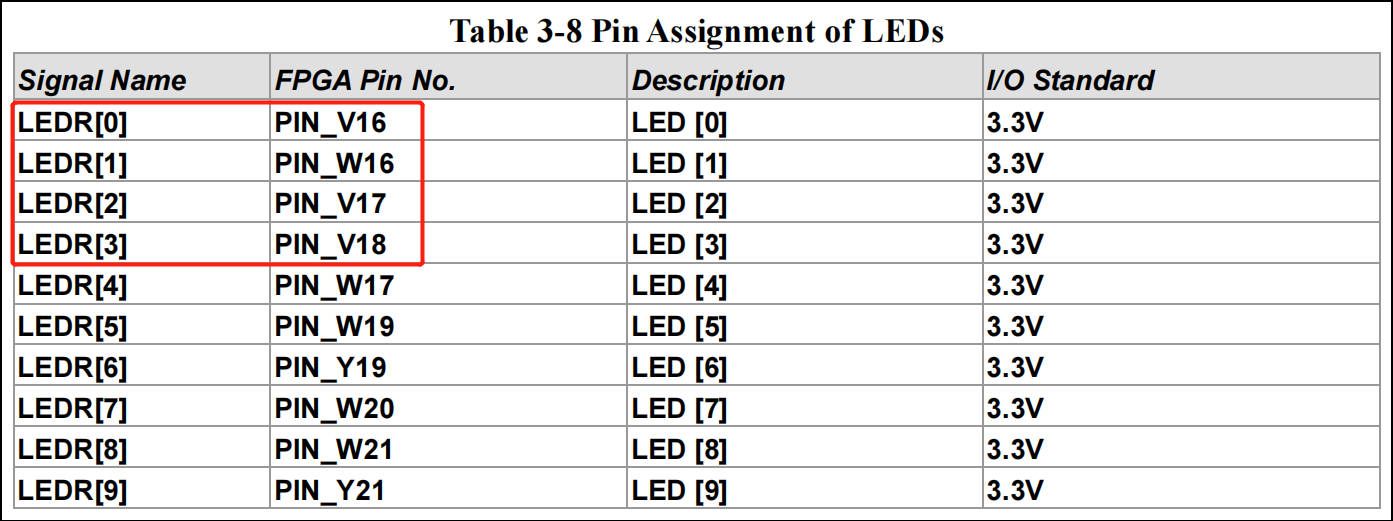

LED

如下图所示,DE1-SOC开发板上有10个红色LED。每个LED连接到Cyclone V FPGA对应的一个引脚,将这些引脚输出设置为高电平1即可点亮对应的LED,反之设置低电平0$即可使对应的LED熄灭。

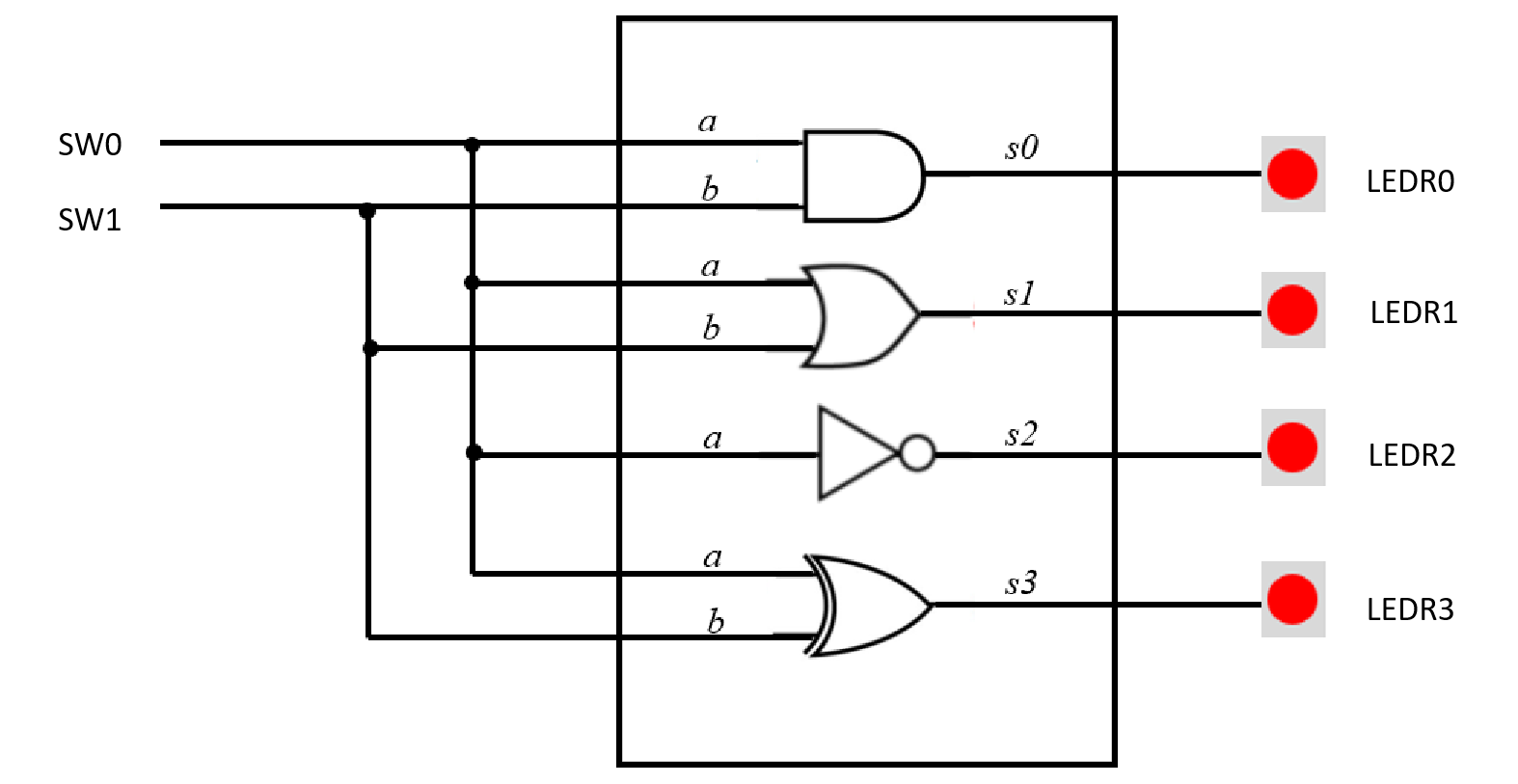

2. 设计思路

本实验所实现的电路,包含了与门、或门、非门以及异或门。与门、或门以及异或门的输入为a 和b ,而输出分别为s0 ,s1 和s2 。非门的输入为a ,输出为s3 。在DE1-SOC实现该电路时,将SW[0] 和SW[1] 作为输入a 和b ,将LEDR[3]~LEDR[0] 作为输出s3~s0。

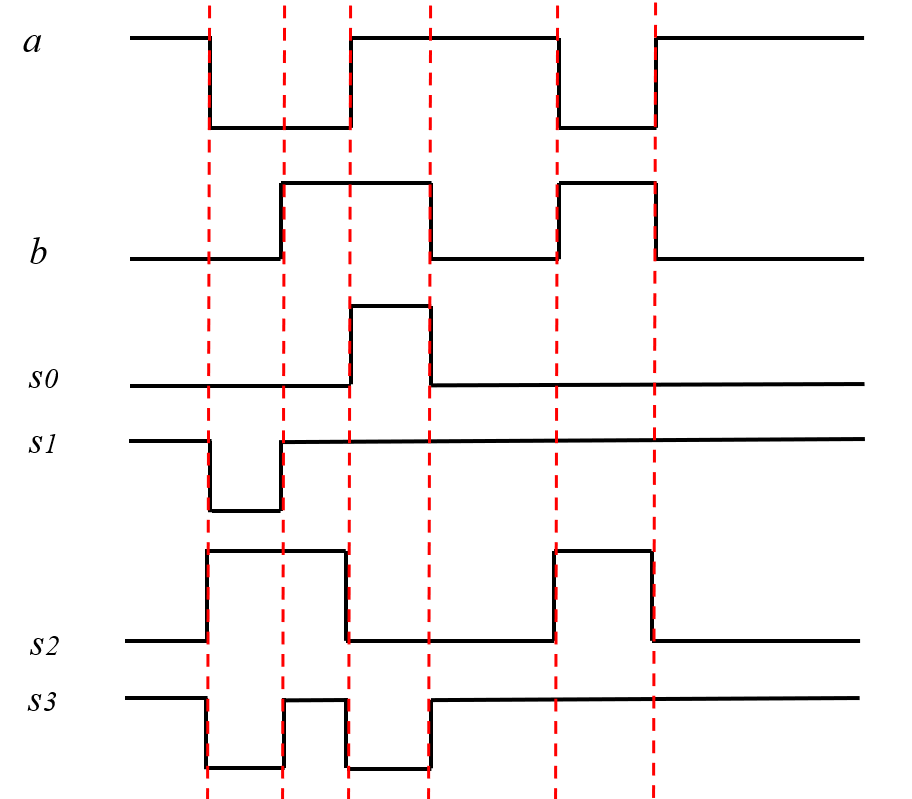

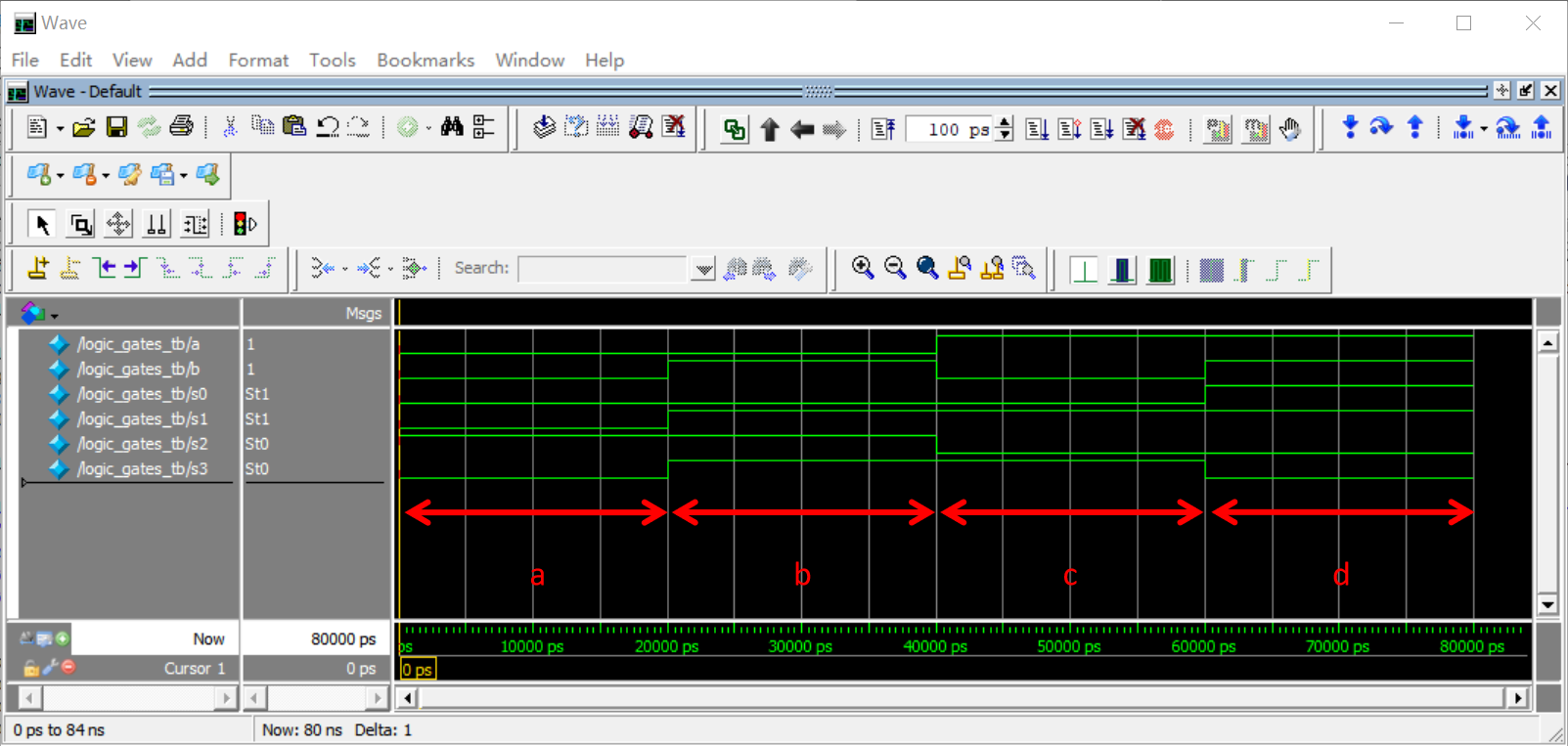

如下图举例显示了该逻辑门电路的波形图。

四、逻辑门电路设计

1. 创建一个新Quartus工程

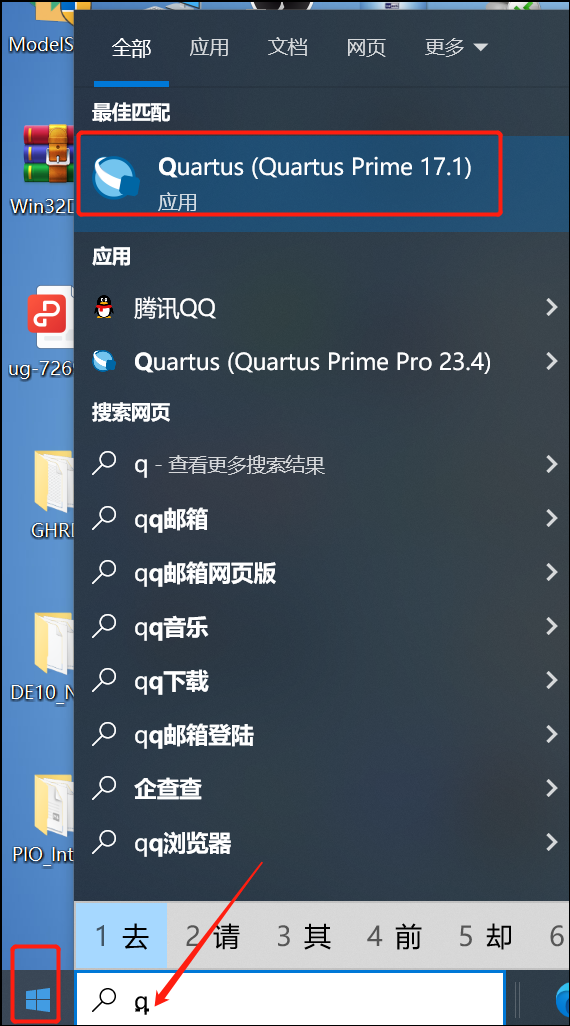

(1) 点击电脑右下角的开始菜单找到Quartus软件,双击Quartus (Quartus Prime 17.1)打开Quartus Prime软件。

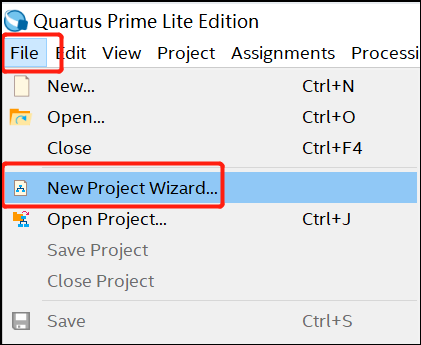

点击菜单File-->New Project Wizard弹出工程创建的对话框。

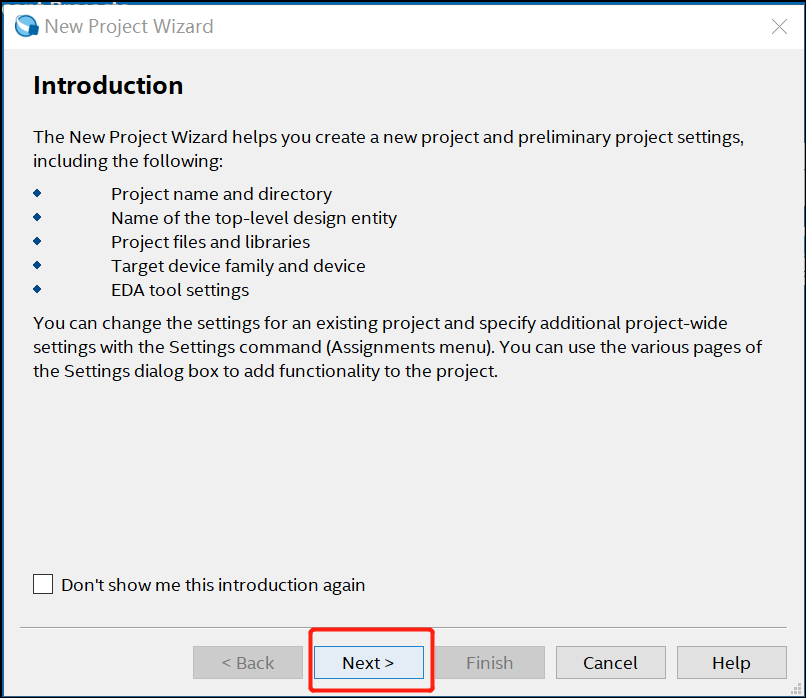

(2)在弹出的对话框中点击Next。

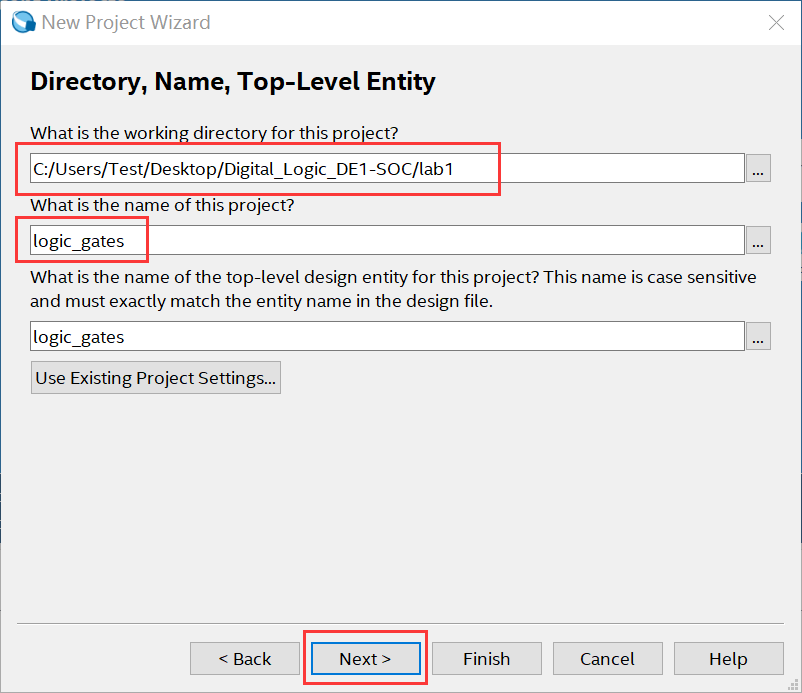

(3)在您的DE1-SOC 工作文件夹下创建一个lab1的文件夹,并将工程路径指向该文件夹,且工程的名称也命名lab1。

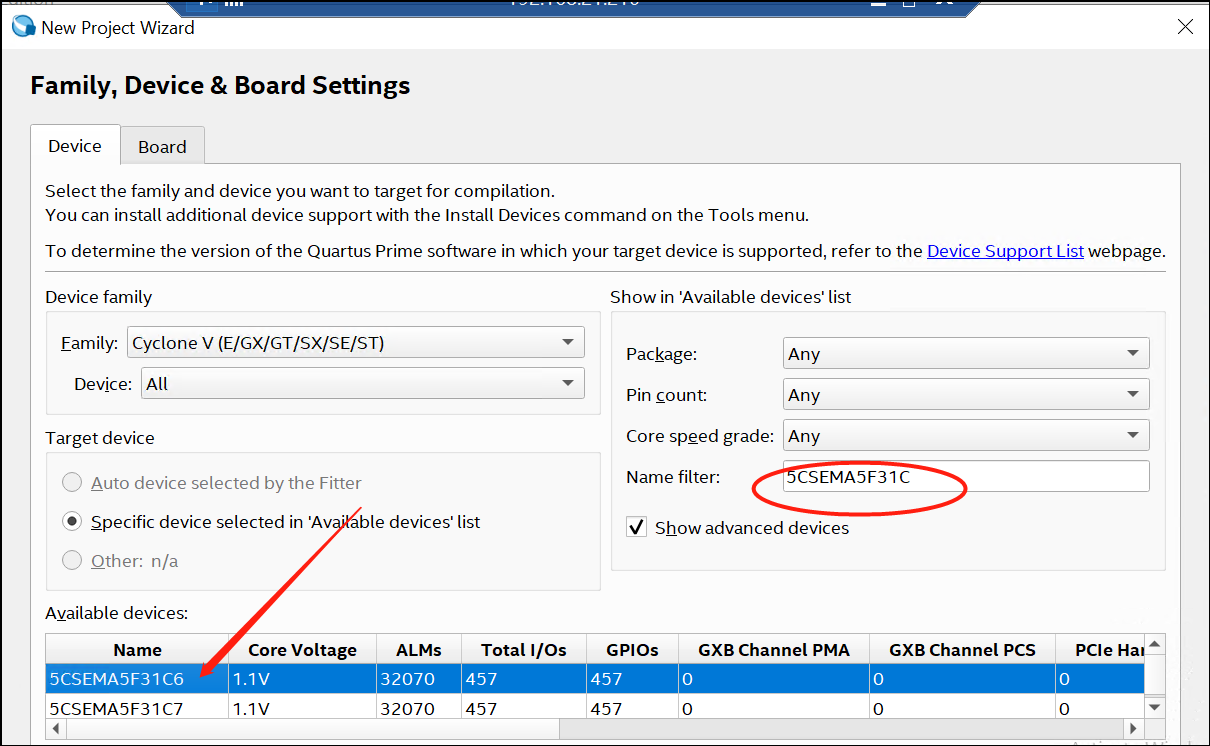

(4)连续点击3次Next得到如下界面,通过器件过滤器筛选选中DE1-SoC的Cyclone V 5CSEMA5F31C6器件。

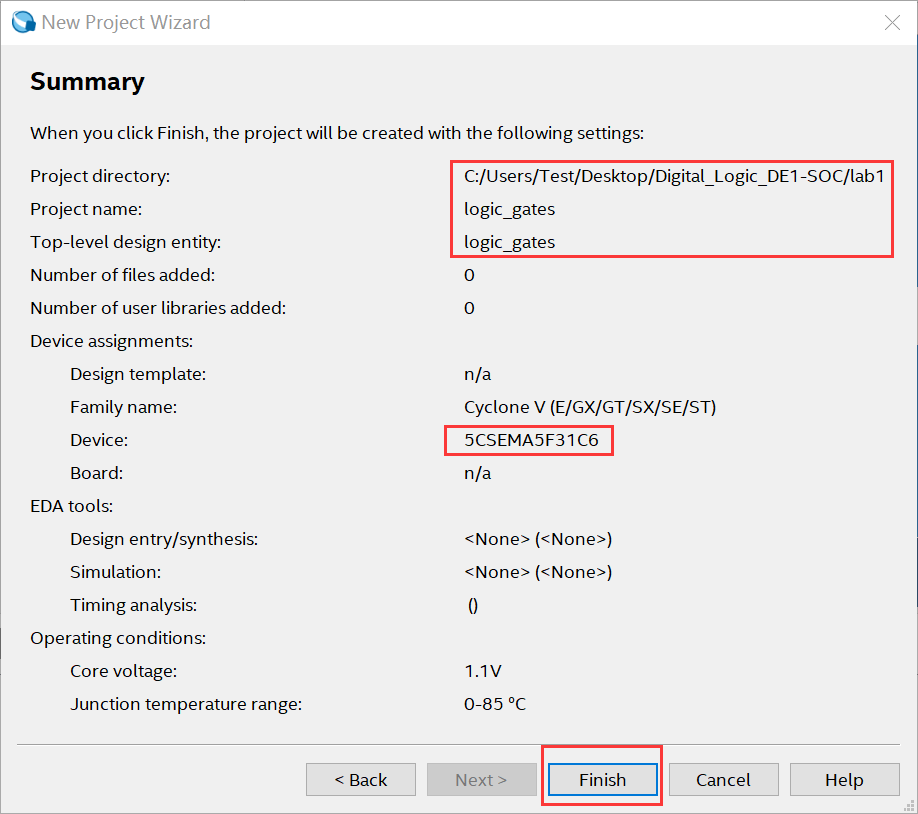

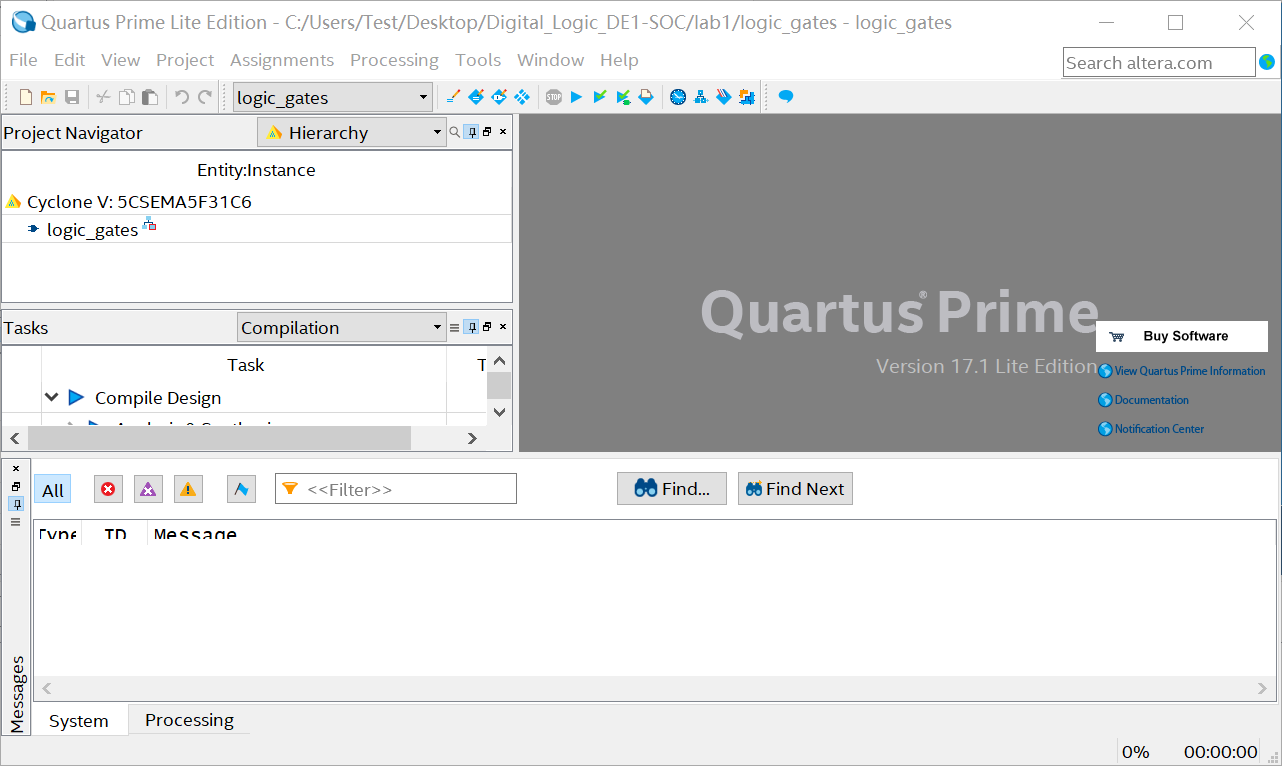

(5)点击Next两次后得到工程的生成报告窗口,检查无误后点击Finish完成工程创建。

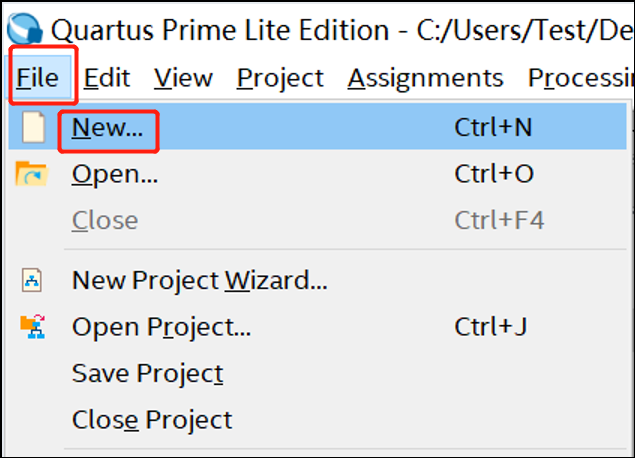

(6)点击Quartus菜单File------New新建一个.v文件。

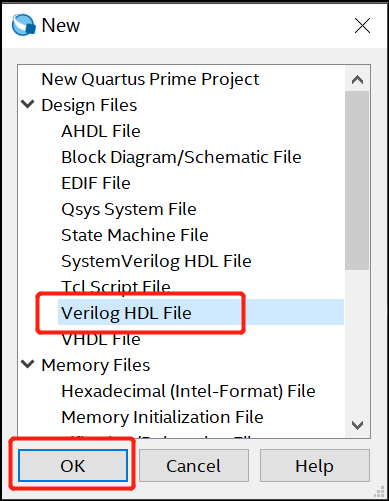

(7)选择Verilog HDL File,然后点击OK完成top文件.v文件的创建。

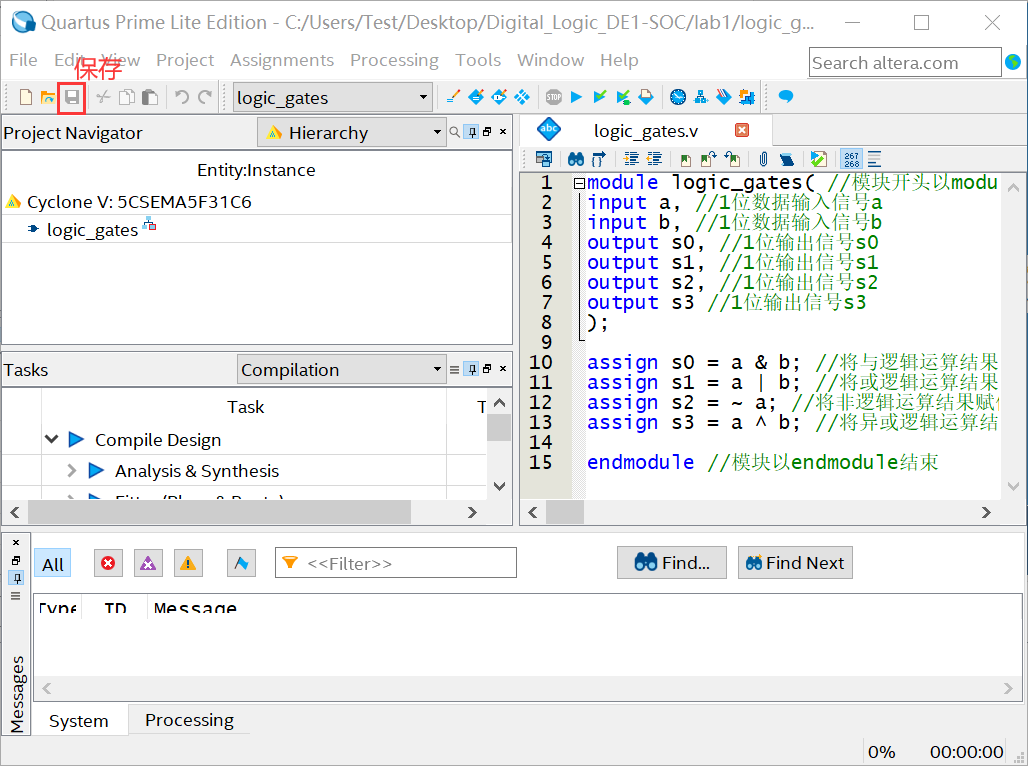

(8)在新建的空白.v文件敲入如下Verilog代码,然后点击保存,文件名保持默认的logic_gates.v即可。

module logic_gates( //模块开头以module开始,模块命名为logic_gates

input a, //1位数据输入信号a

input b, //1位数据输入信号b

output s0, //1位输出信号s0

output s1, //1位输出信号s1

output s2, //1位输出信号s2

output s3 //1位输出信号s3

);

assign s0 = a & b; //将与逻辑运算结果赋值给输出信号s0

assign s1 = a | b; //将或逻辑运算结果赋值给输出信号s1

assign s2 = ~ a; //将非逻辑运算结果赋值给输出信号s2

assign s3 = a ^ b; //将异或逻辑运算结果赋值给输出信号s3

endmodule //模块以endmodule结束

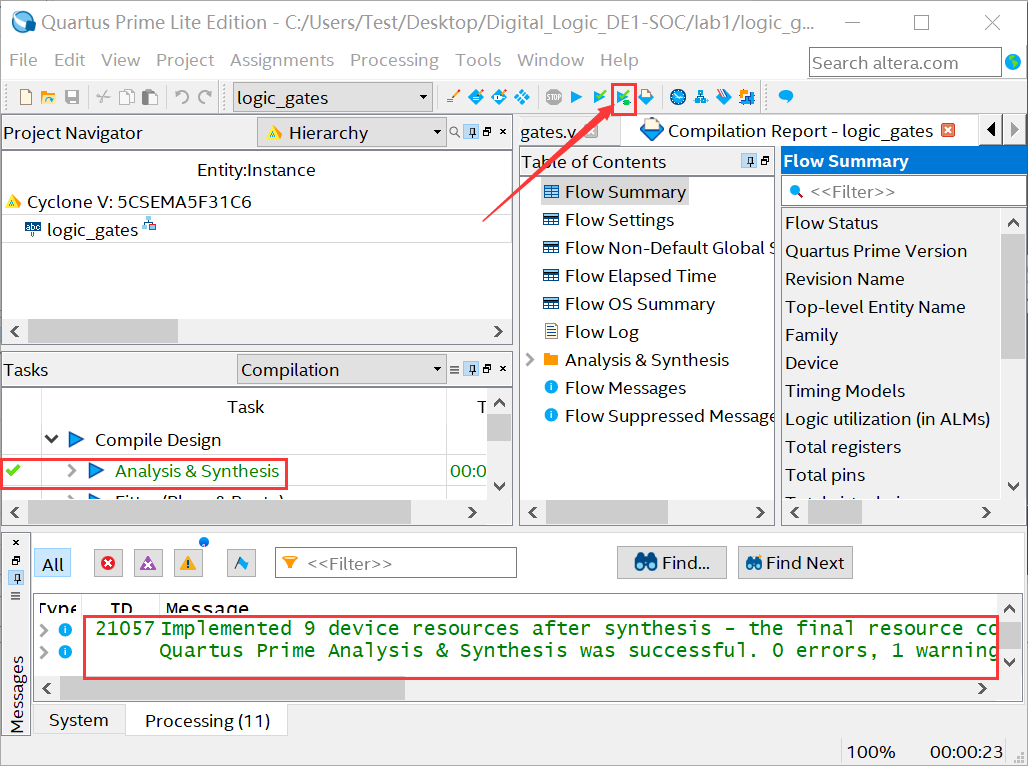

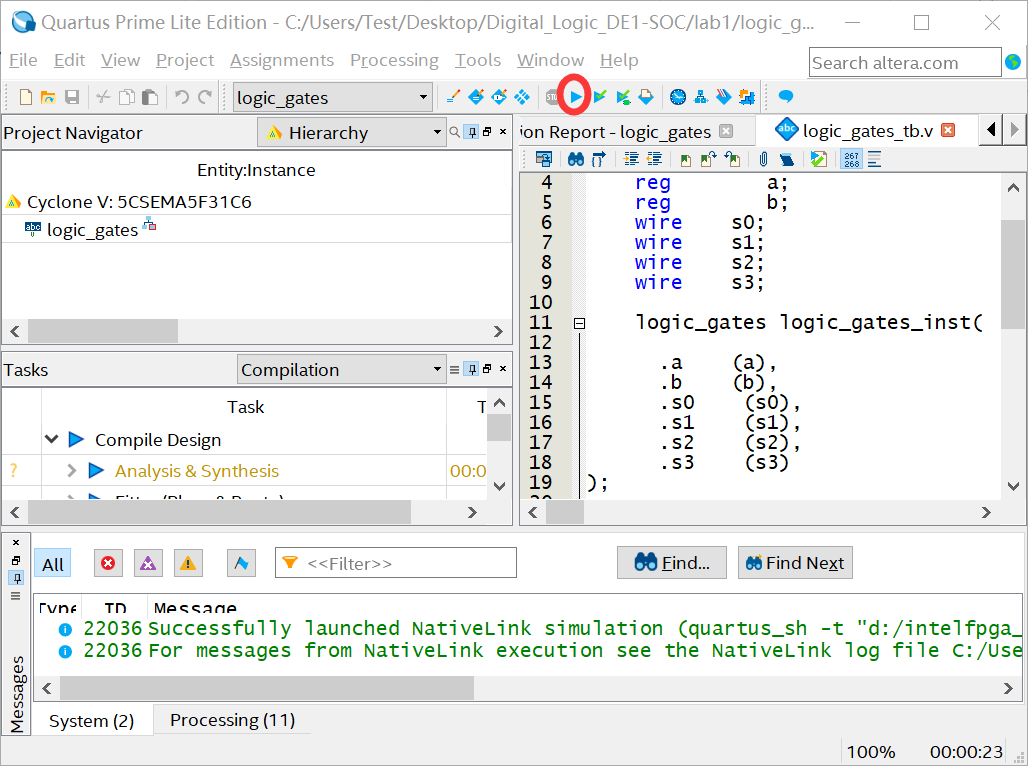

(9)点击Quartus软件工具栏的Processing --> Start --> Start Analysis & Synthesis或点击

按钮对Verilog HDL代码执行语法检查和综合,该过程成功完成之后在Quartus软件窗口的Tasks页面中,Analysis & Synthesis旁边将显示一个绿色勾型标记,如下图所示。如果在该过程中提示有错误,请检查Verilog HDL代码语法,确保与上述代码块完全一致。

2. 对电路进行仿真

对Verilog HDL代码进行语法分析与综合确认无误之后,就可以对设计进行功能仿真(也称之为前仿真)了,这个操作是为了验证电路逻辑功能是否符合设计要求。通过功能仿真可以及时发现设计中的错误,在系统设计前期即可完成修改,提高设计可靠性。

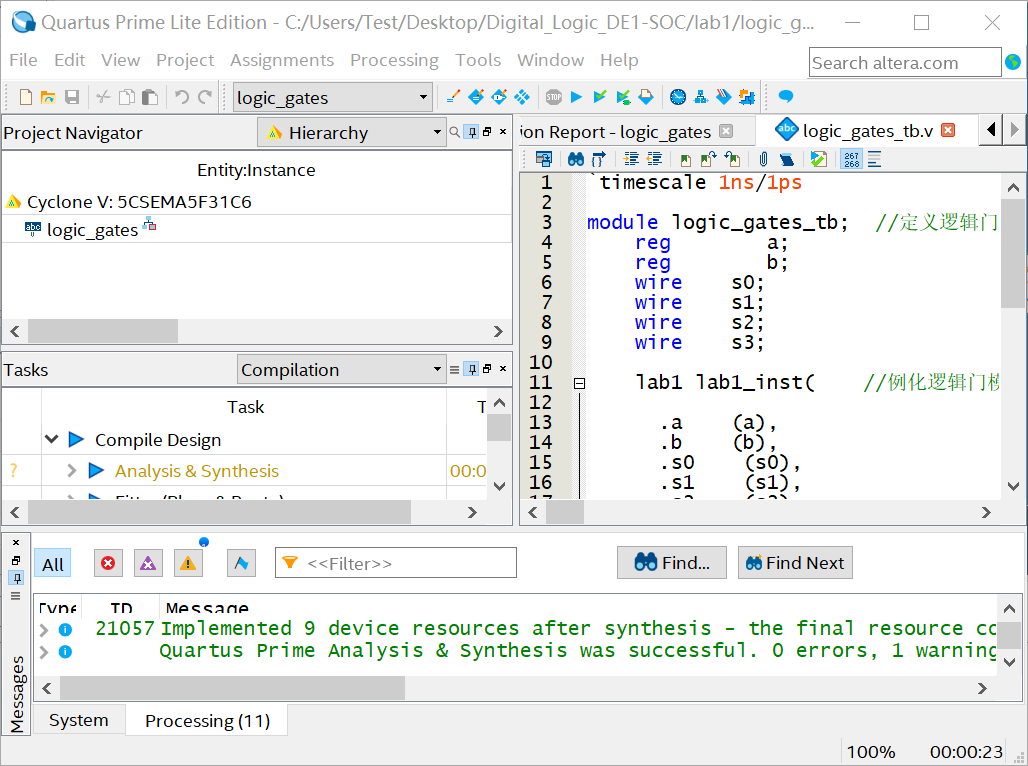

(1) 点击Quartus软件工具栏的File --> New --> Verilog HDL File,点击OK,这样就新建了一个空白Verilog HDL文件,再点击File --> Save As ...保存,命名为logic_gates_tb.v。然后将如下仿真代码保存到logic_gates_tb.v文件中。

`timescale 1ns/1ps

module logic_gates_tb; //定义逻辑门测试仿真模块,包含输入信号a,b以及输出信号s0,s1,s2,s3

reg a;

reg b;

wire s0;

wire s1;

wire s2;

wire s3;

logic_gates logic_gates_inst( //例化逻辑门模块

.a (a),

.b (b),

.s0 (s0),

.s1 (s1),

.s2 (s2),

.s3 (s3)

);

initial begin //设置输入信号a,b的四种不同输入组合

//

a = 1'b0;

b = 1'b0;

# 20;

//

a = 1'b0;

b = 1'b1;

# 20;

//

a = 1'b1;

b = 1'b0;

# 20;

//

a = 1'b1;

b = 1'b1;

# 20;

end

endmodule

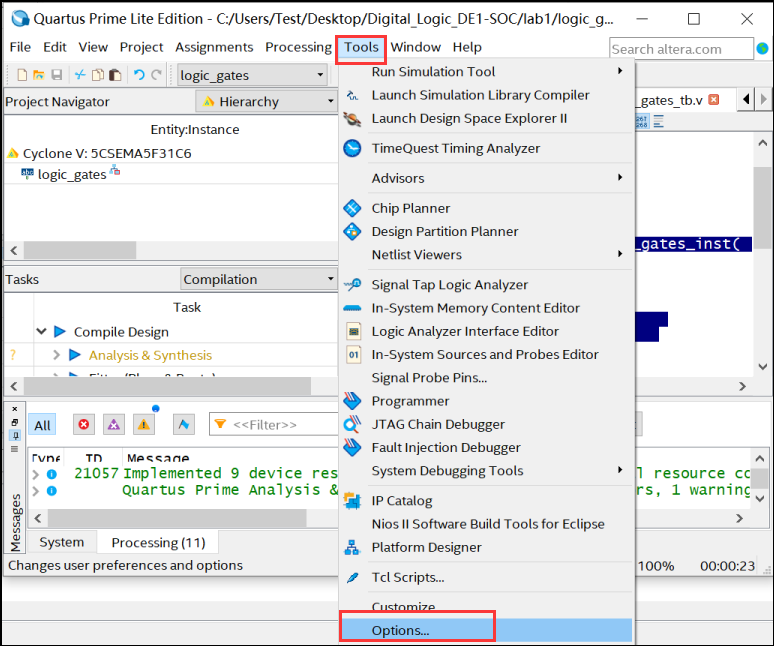

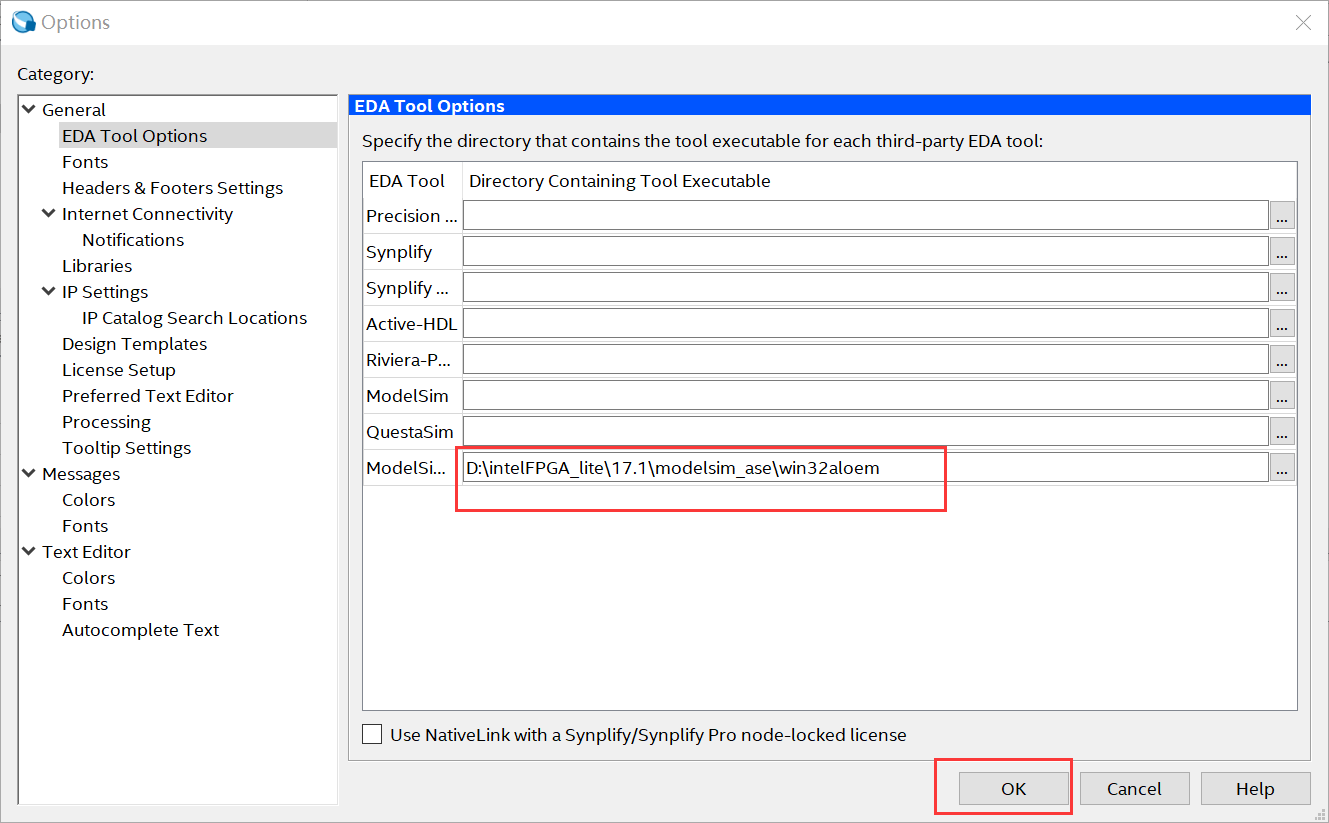

(2)要先将Modelsim 的安装路径设置一下,然后Quartus系统才可以自动调用指定的仿真工具。依次点击Quartus菜单Tools------Options...

将仿真工具路径指定到...intelFPGA_lite\17.1\modelsim_ase\win32aloem。

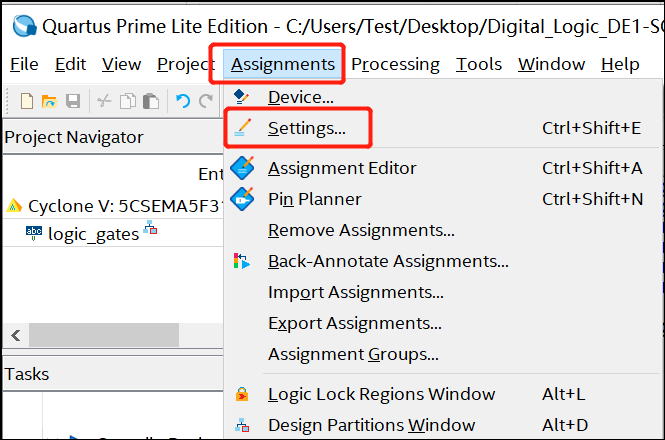

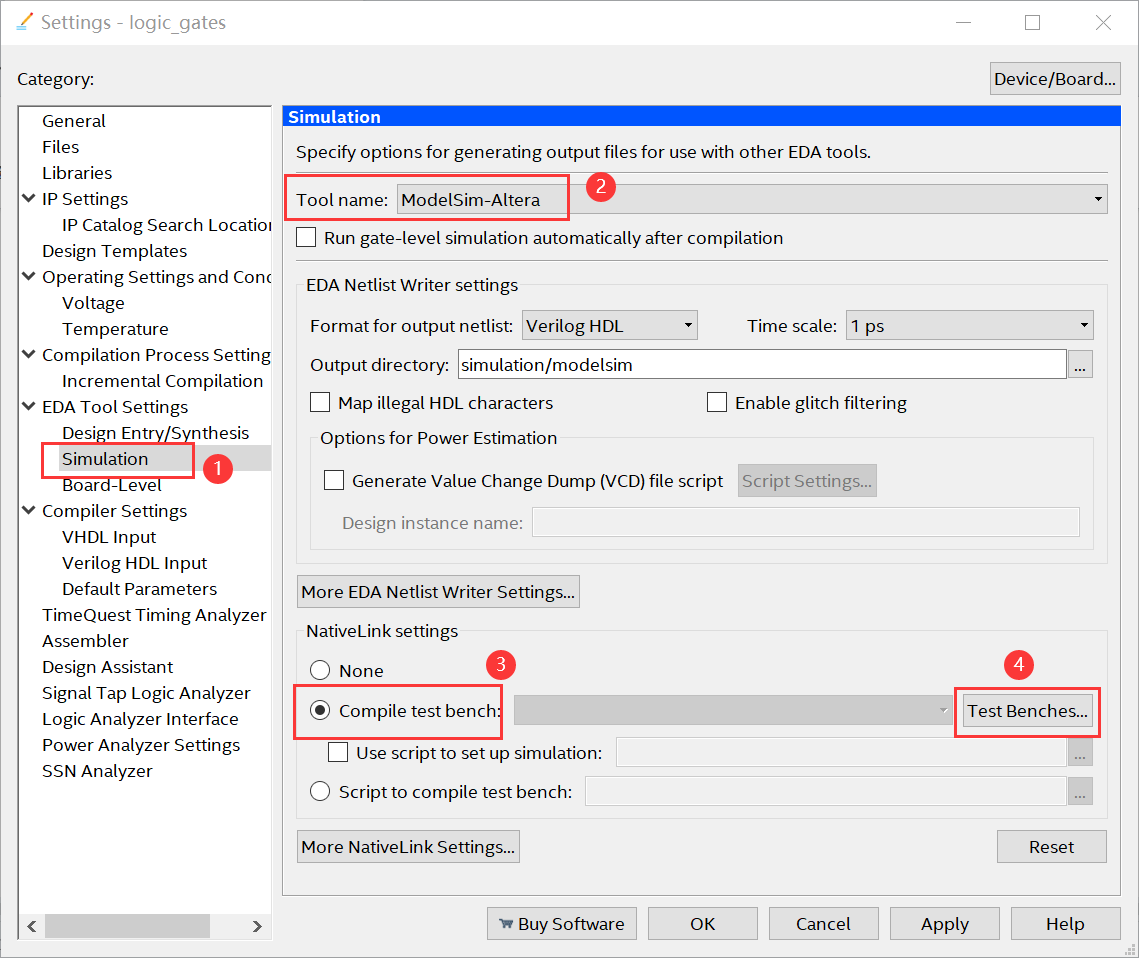

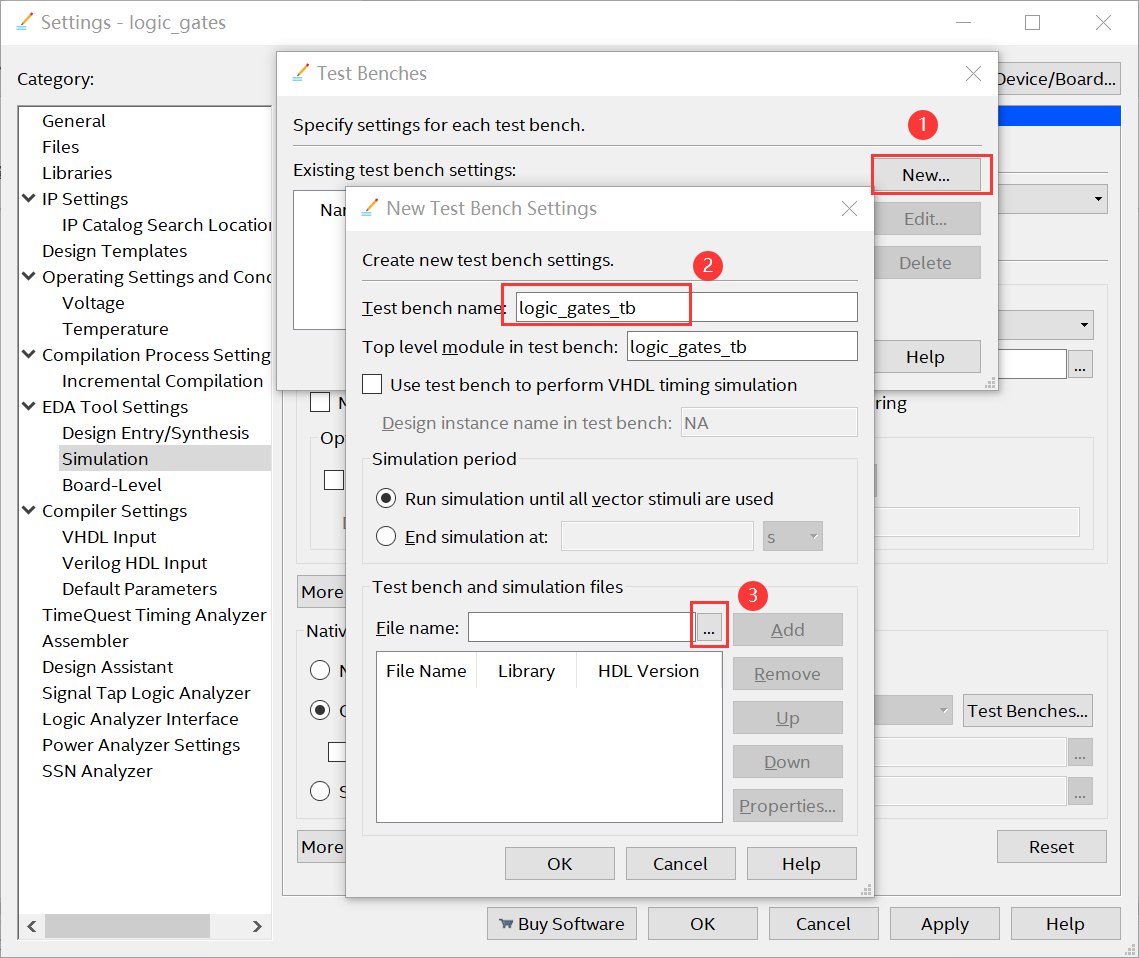

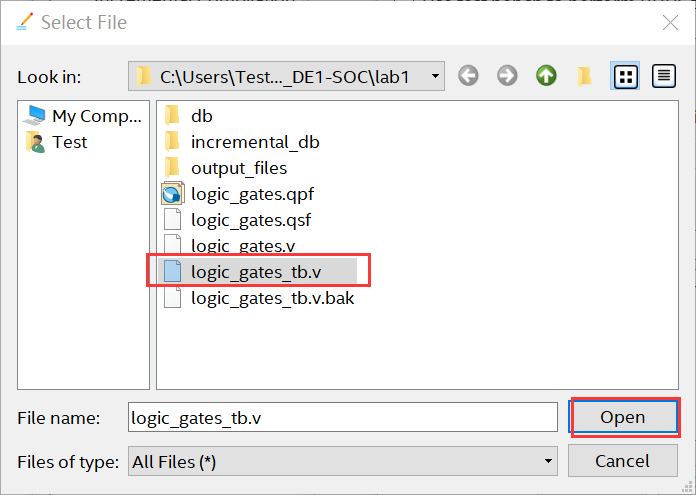

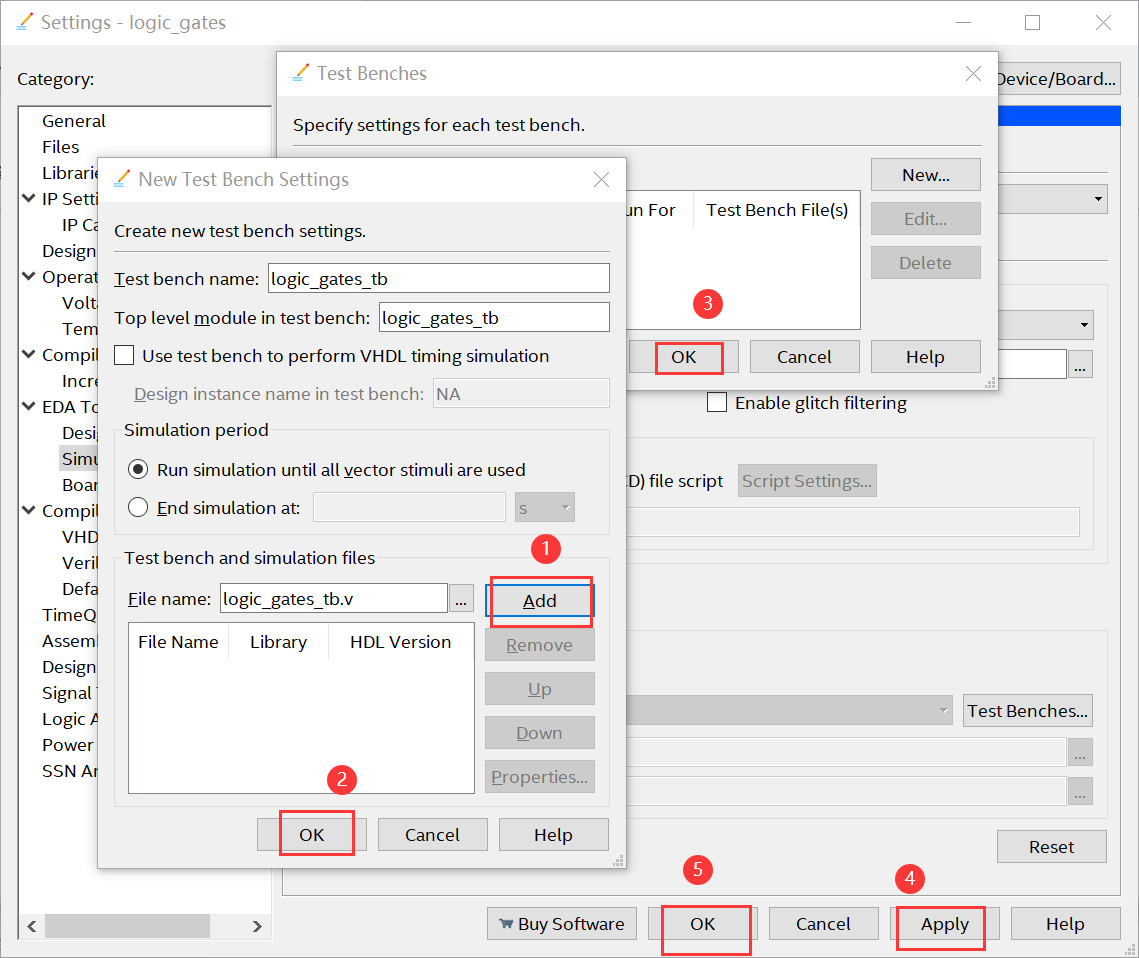

(3)点击Quartus软件工具栏的Assignments --> Settings,在弹出的Settings窗口中,选中Simulation栏,Tool name选择ModelSim-Altera,设置Quartus自动调用ModelSim。然后选择添加Test Bench文件。

点击Add和OK后,再点击OK、Aplly和OK完成仿真工具和仿真文件的设置。

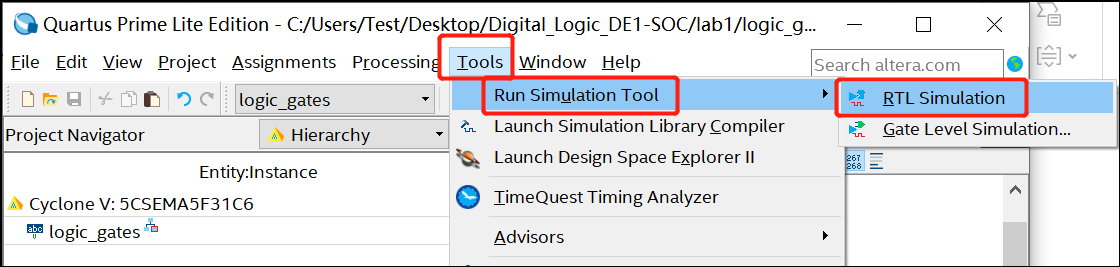

(4)击Quartus软件工具栏的Tools --> Run Simulation Tool --> RTL Simulation启动ModelSim仿真。

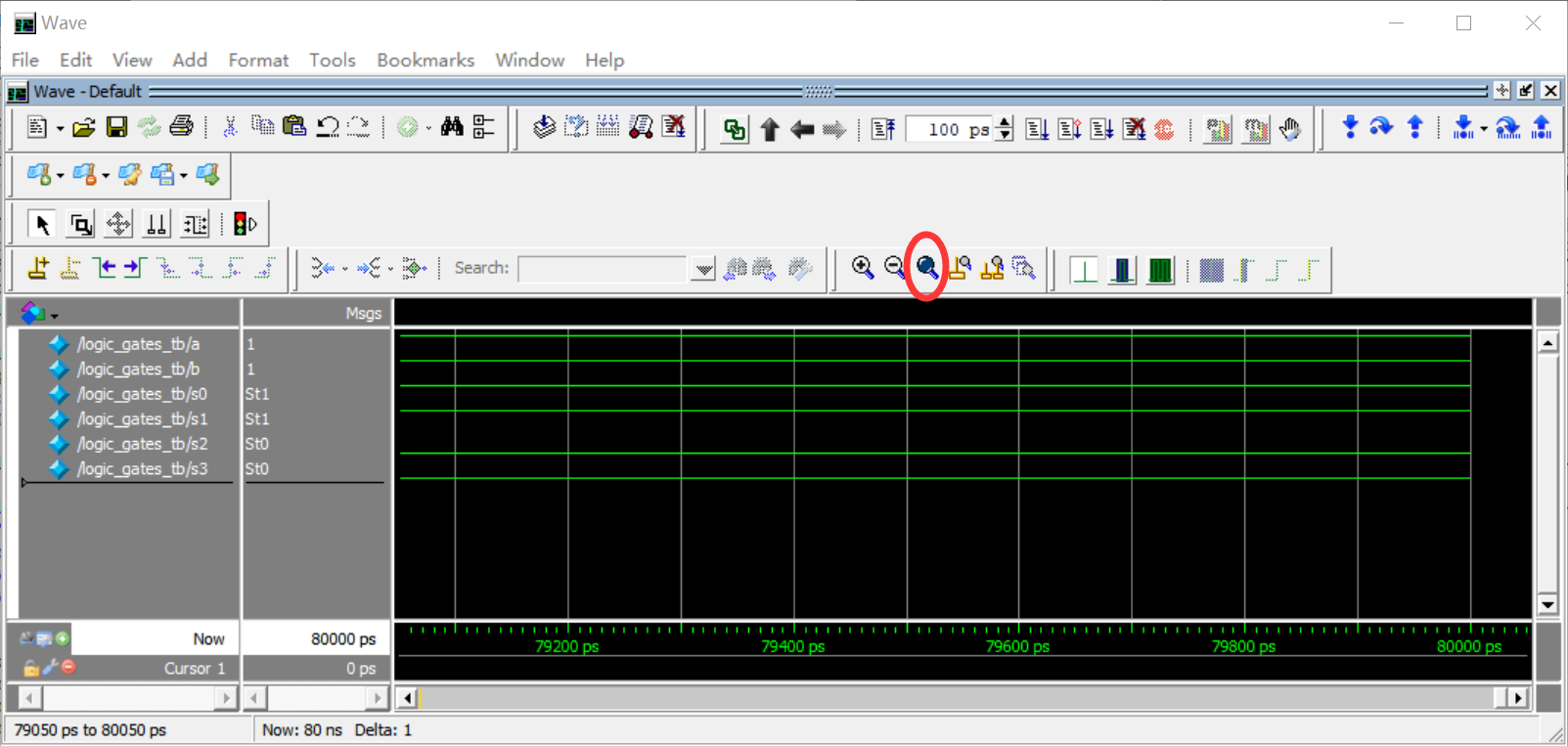

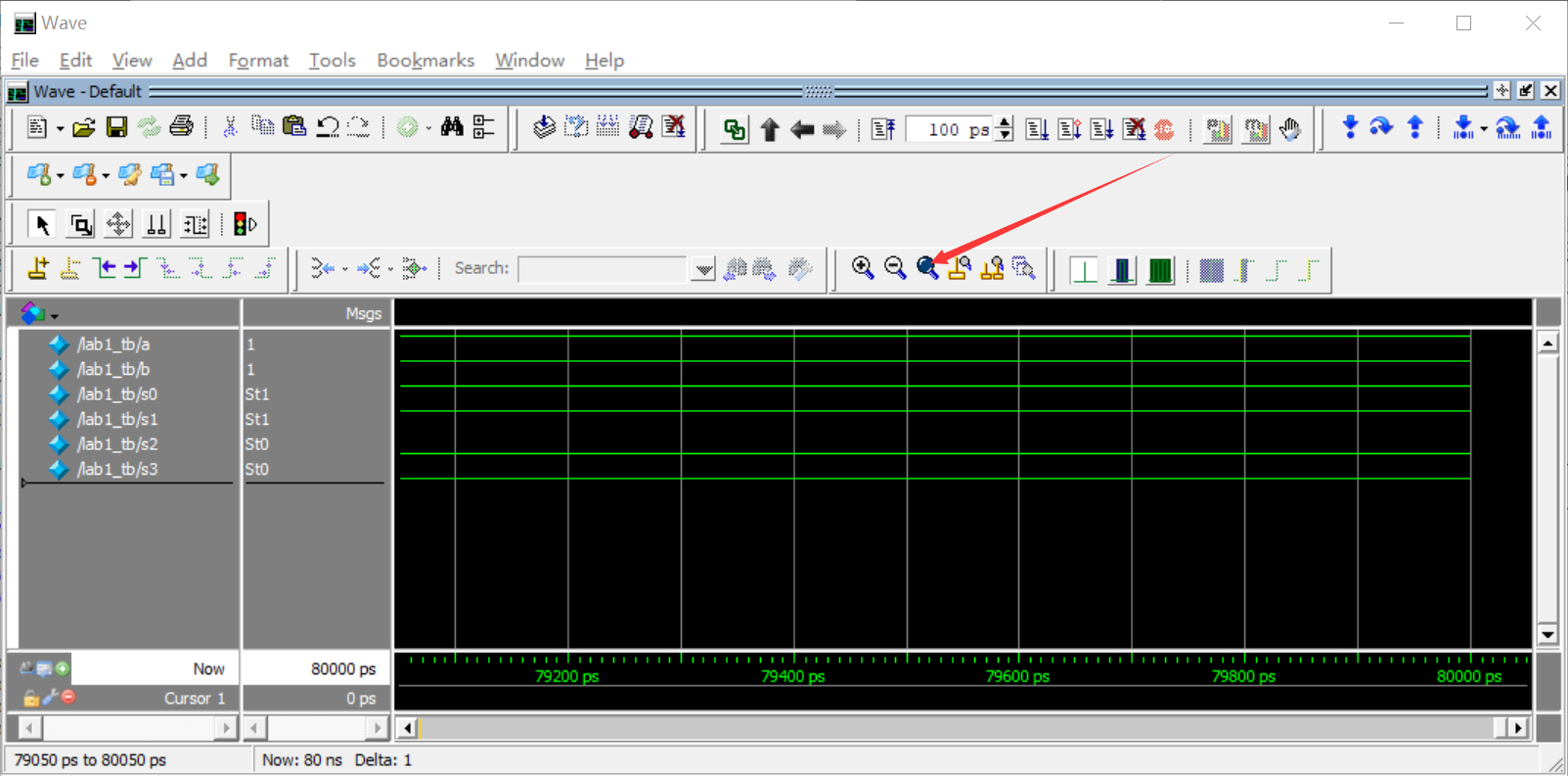

(5)点击Wave选项卡切换到仿真波形窗口此时还看不到完整的仿真波形,可以通过点击下图所示的Zoom Full按钮来显示完整的波形。

从上面波形图可以看出:

a. 当输入a =0,b =0时,四个输出分别为s0 =0,s1 =0,s2 =1,s3=0;

b. 当输入a =0,b =1时,四个输出分别为s0 =0,s1 =1,s2 =1,s3=1;

c. 当输入a =1,b =0时,四个输出分别为s0 =0,s1 =1,s2 =0,s3=1;

d. 当输入a =1,b =1时,四个输出分别为s0 =1,s1 =1,s2 =0,s3=0。

结果与预期一致,说明本实验要求的逻辑门电路已实现。

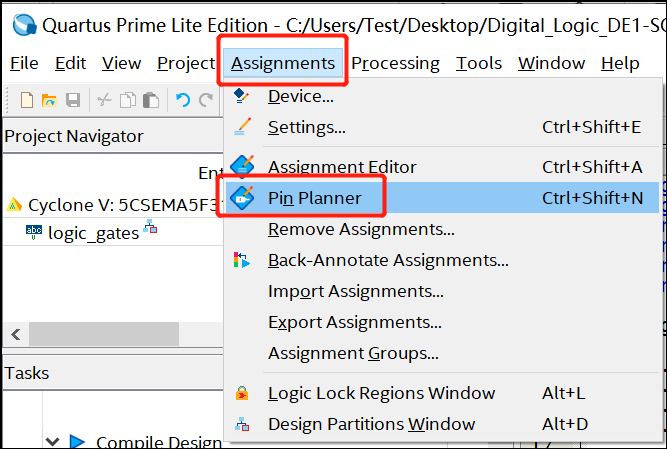

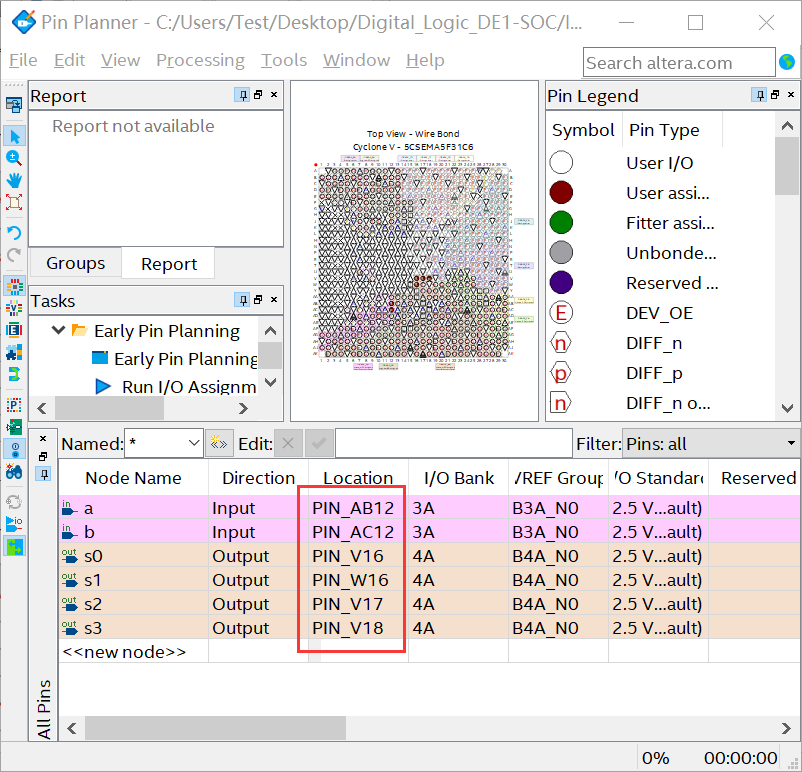

3. 引脚分配和全编译

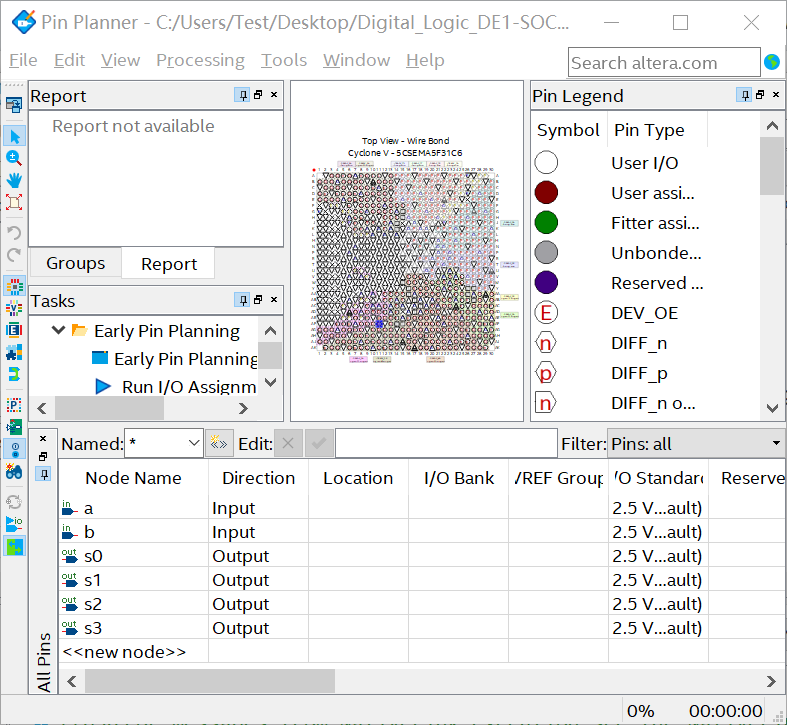

一般功能仿真也可以跳过不做,在分析和综合的步骤完成以后,就可以进行FPGA引脚分配了。点击Assignments------Pin Planner弹出引脚分配窗口,按照DE1-SOC 用户手册或者电路图进行引脚分配。

关于引脚分配信息可以查看DE1-SoC_v.5.1.3_HWrevF.revG_SystemCD\UserManual\DE1-SoC_User_manual.pdf第 25、26页或者E:\CD_Package\01-DE1-SoC\DE1-SoC_v.5.1.3_HWrevF.revG_SystemCD\Schematic\DE1-SoC.pdf的第3页。

这里,a和b两个操作数可以通过拨码开关SW0、SW1来控制,s0到s3信号分别输出到LEDR0到LEDR3。

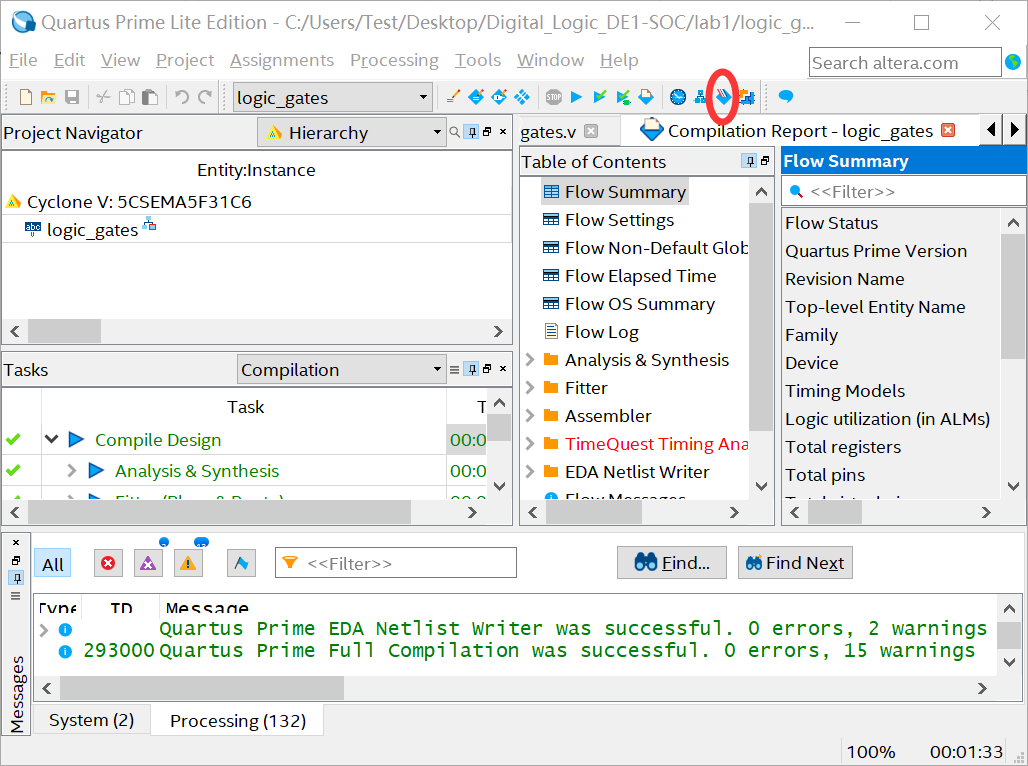

关闭Pin Planner窗口,点击如下按钮进行工程的全编译。

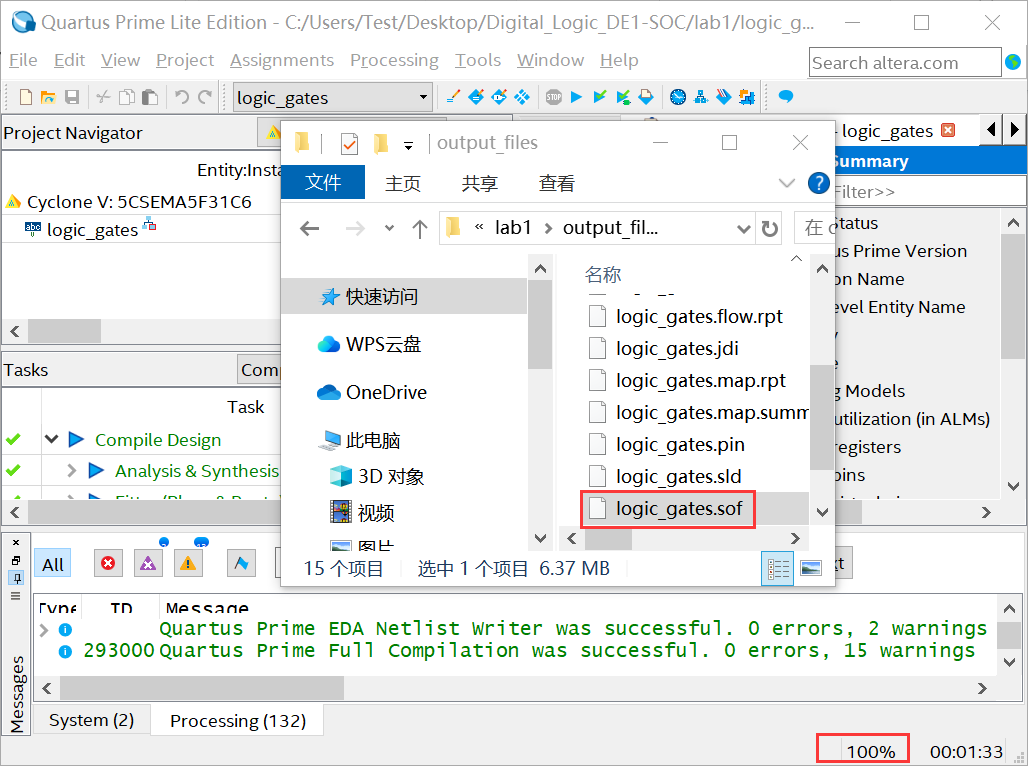

如果编译成功,Quartus窗口右下角会显示100%,同时会在...lab1\output_files文件夹下生成一个logic_gates.sof文件。

4. 下板测试

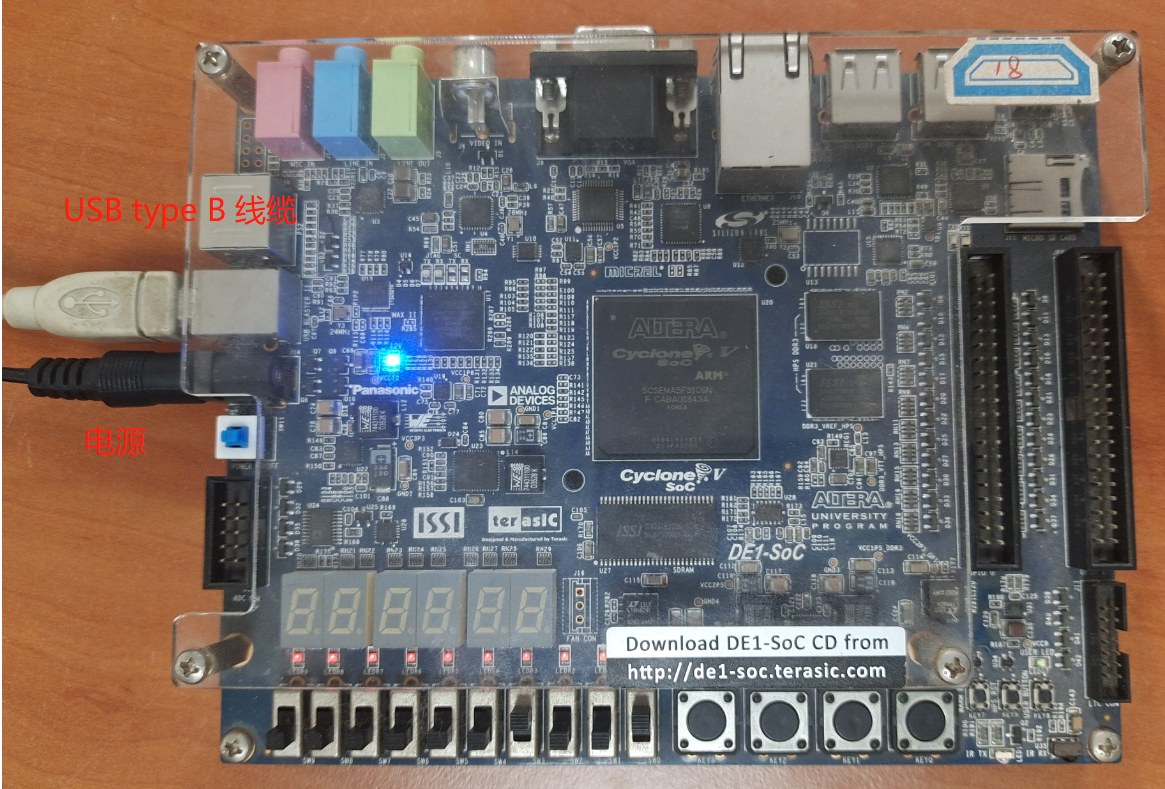

(1)将DE1-SOC开发板和电脑用板子自带的白色USB type B 线缆连接起来。给DE1-SOC插上电源并按SW11按键进行开机。

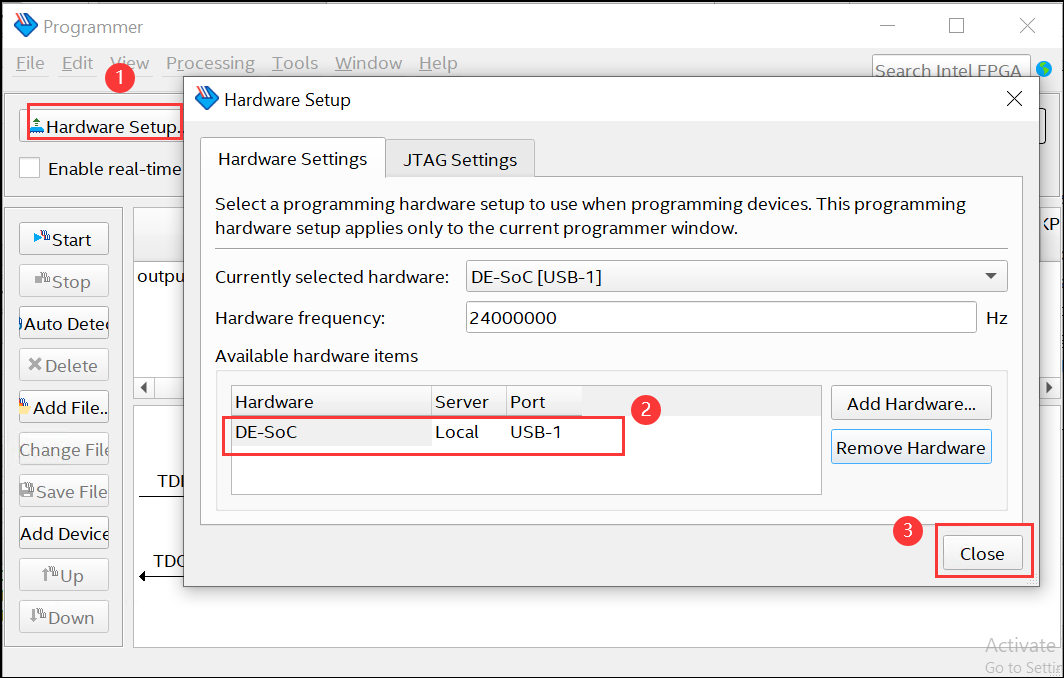

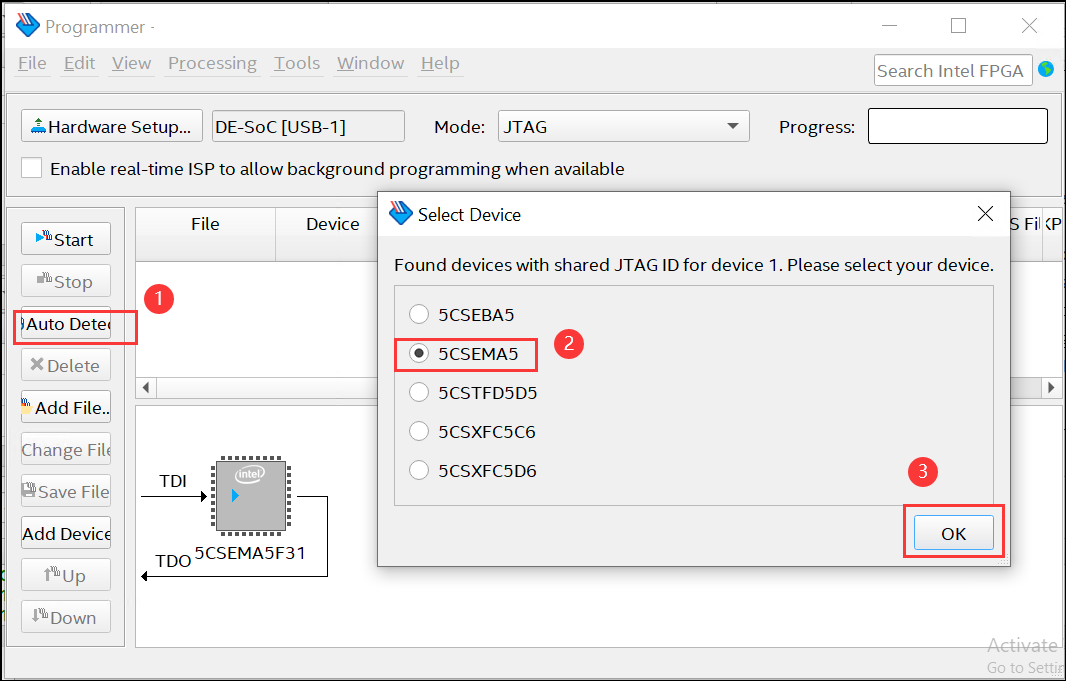

(2)打开Quartus的Programmer工具,点击Hardware Setup,选择DE-SOC[USB-1]端口。

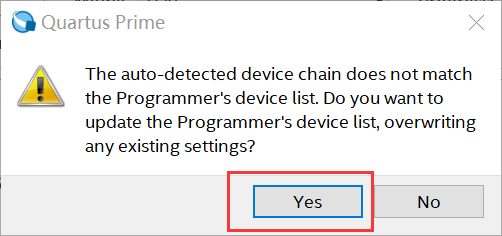

(3)点击Auto Detect,选择DE1-SOC对应的FPGA器件5CSEMA5。

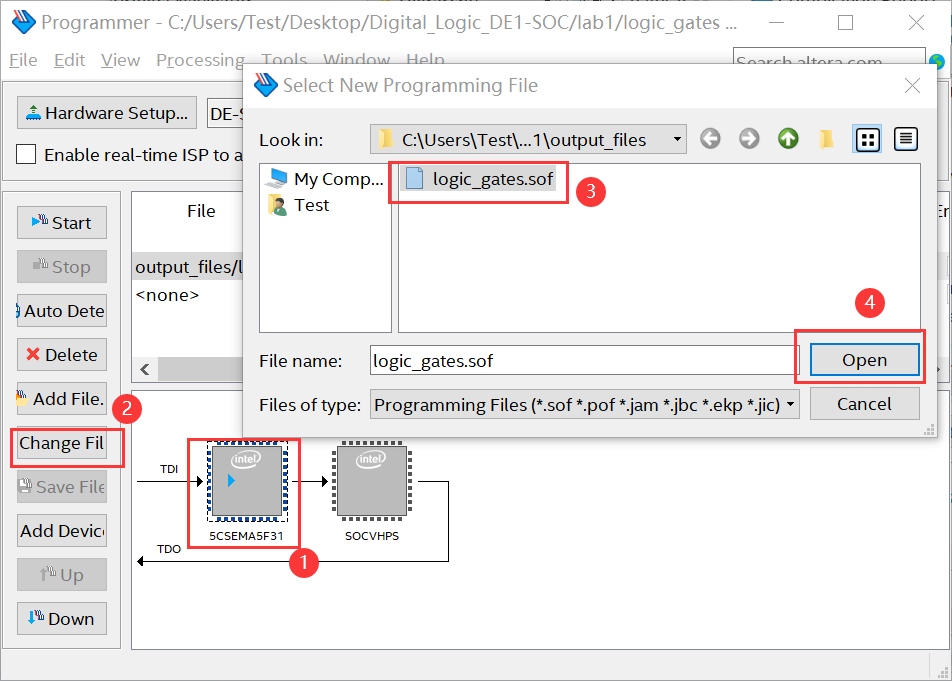

(4)这时会出现两个器件(5CSEMA5和SOCHPS),右击器件5CSEMA5,选择Change File...,然后选择...\lab1\output_files路径下的logic_gates.sof文件。

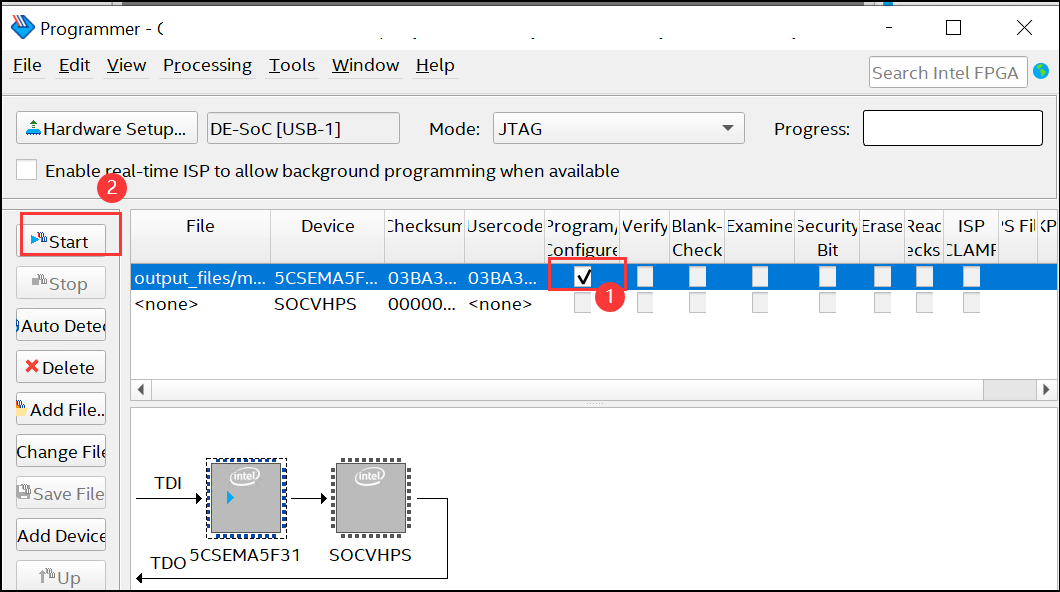

(5) 然后勾选Program/Configure复选框,点击Start按钮开始配置FPGA。

进度条显示100%代表FPGA 配置成功。

(6)拨动SW0和SW1观察LEDR0-3的现象。

SW1、SW0分别为00:

SW1、SW0分别为01:

SW1、SW0分别为10:

SW1、SW0分别为11: