参考视频:FPGA IP之CORDIC_哔哩哔哩_bilibili

FPGA IP之CORDIC使用与仿真_哔哩哔哩_bilibili

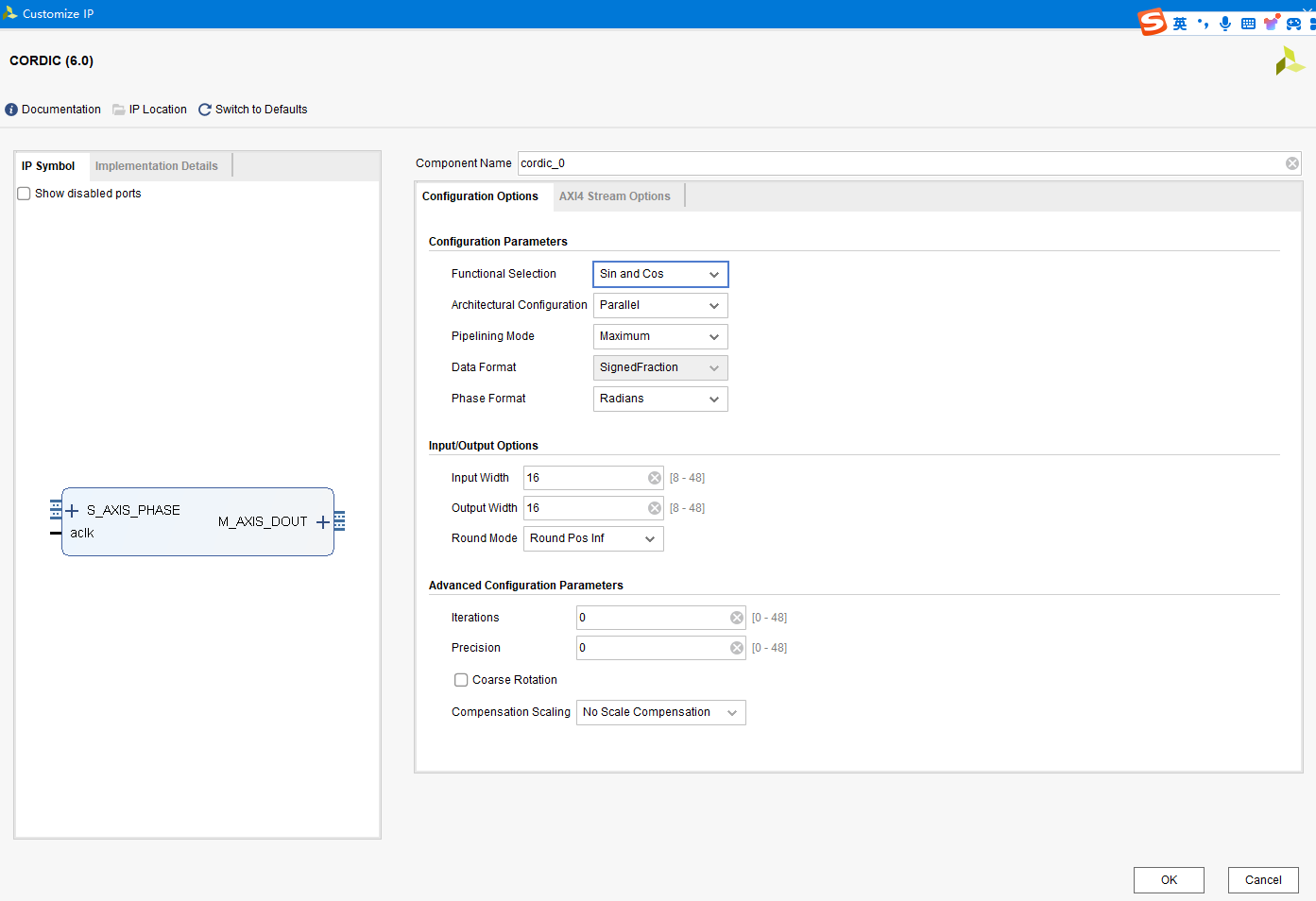

一、参数说明

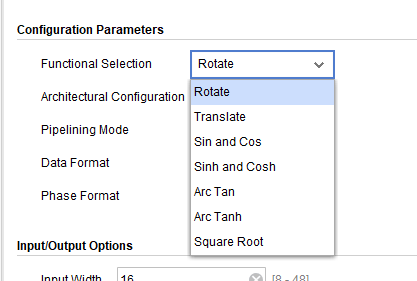

functional selection

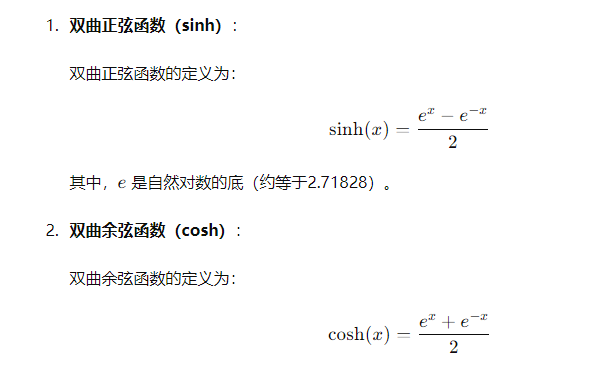

rotate是旋转,sin and cos是计算这两个三角函数,sinh和cosh是计算双曲正弦和双曲余弦

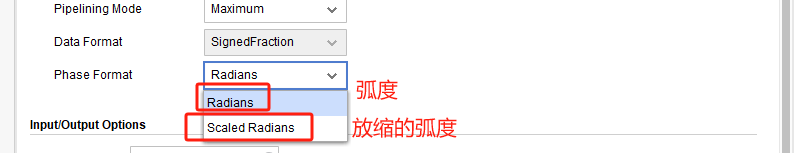

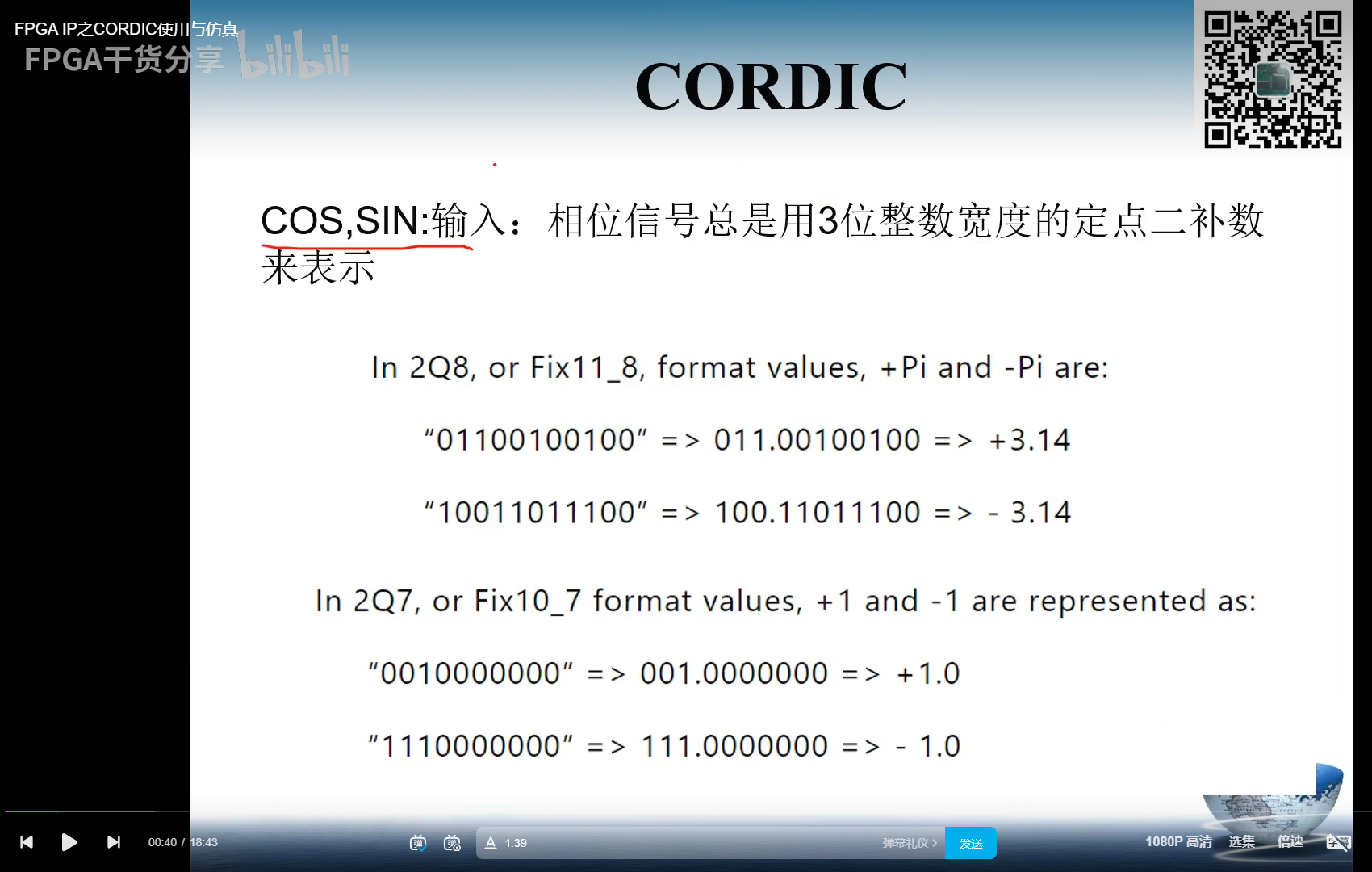

phase format

对于相位格式有两种表示方法,分别是

前者放缩到-π到+π,后者放缩到-1到+1,另外由于π实际上是一个无限不循环小数,所以使用前者可能会造成一些精度上的误差,建议使用后者,即scaled radians

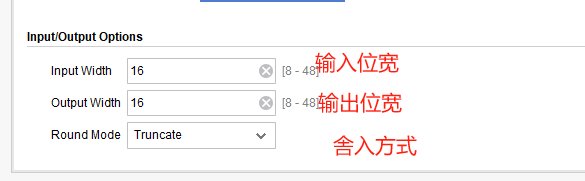

输入输出选项

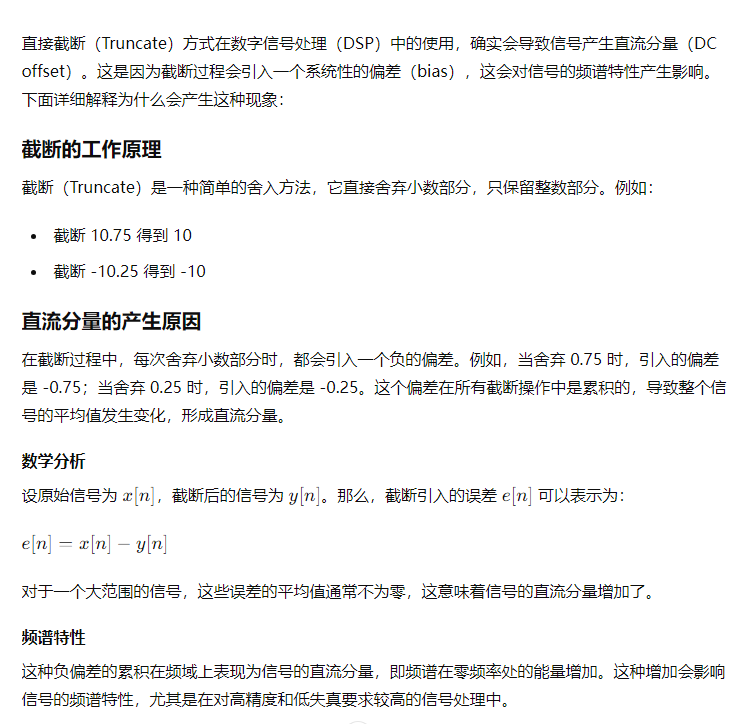

如果直接采用截断(truncate),可能会产生频率上的直流分量

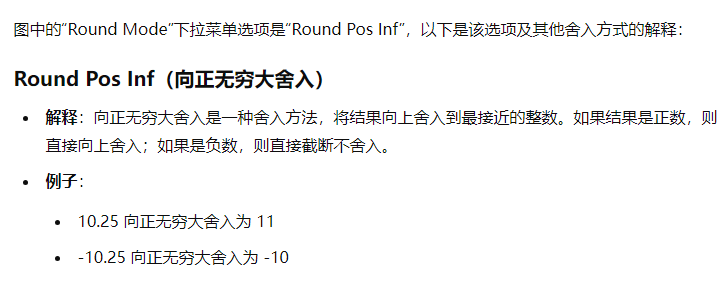

故在这里我们选用的舎入方式是round pos inf,向正无穷大舎入

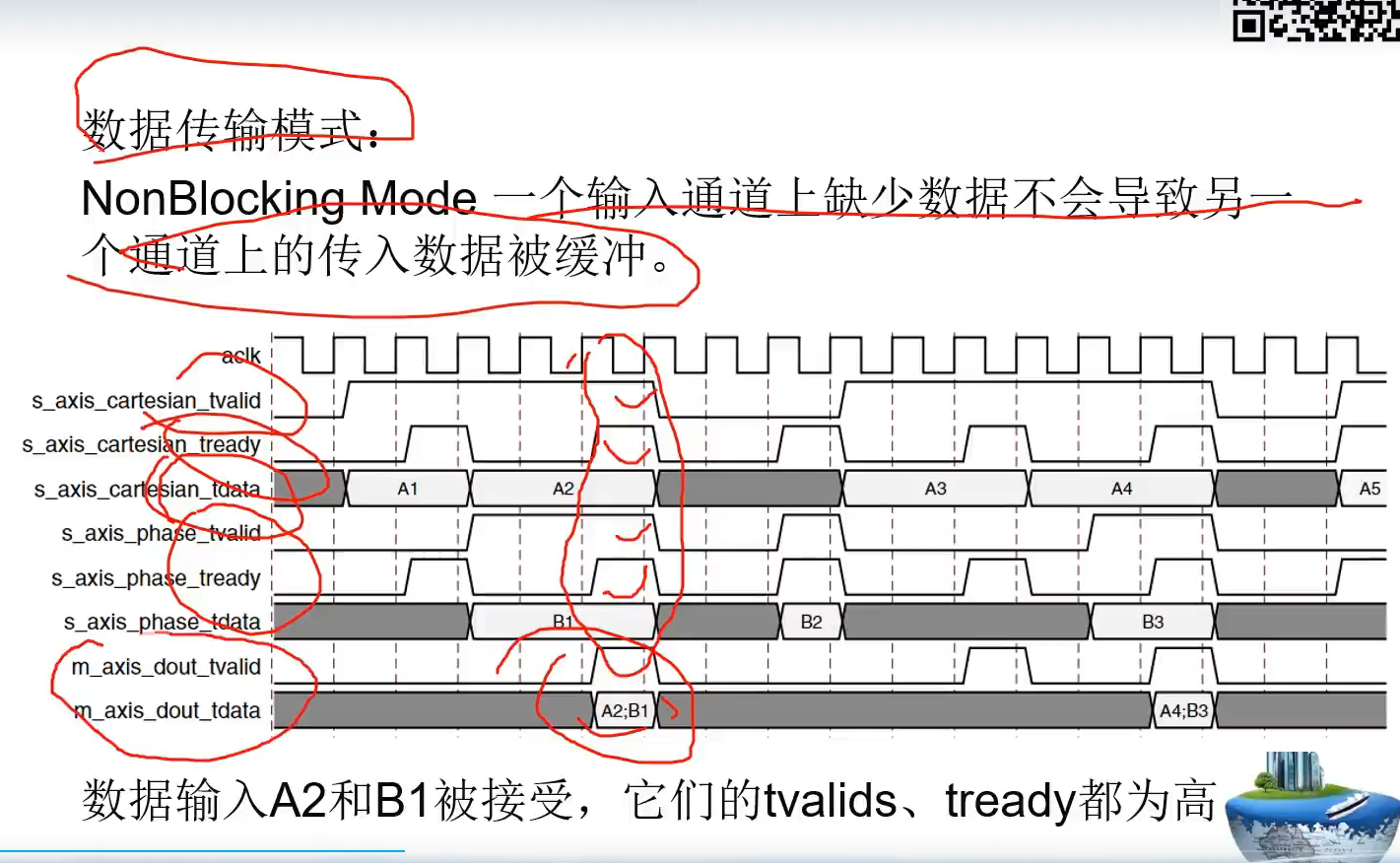

nonblocking mode的时序

只有两组数据的valid和ready同时拉高,才会计算他们的乘积。

其余保持默认

最终用于仿真的IP核配置

计算指数结果需要注意的

参考csdn: Vivado使用Cordic IP计算e^ix(复e指数函数)_vivado cordic指数-CSDN博客

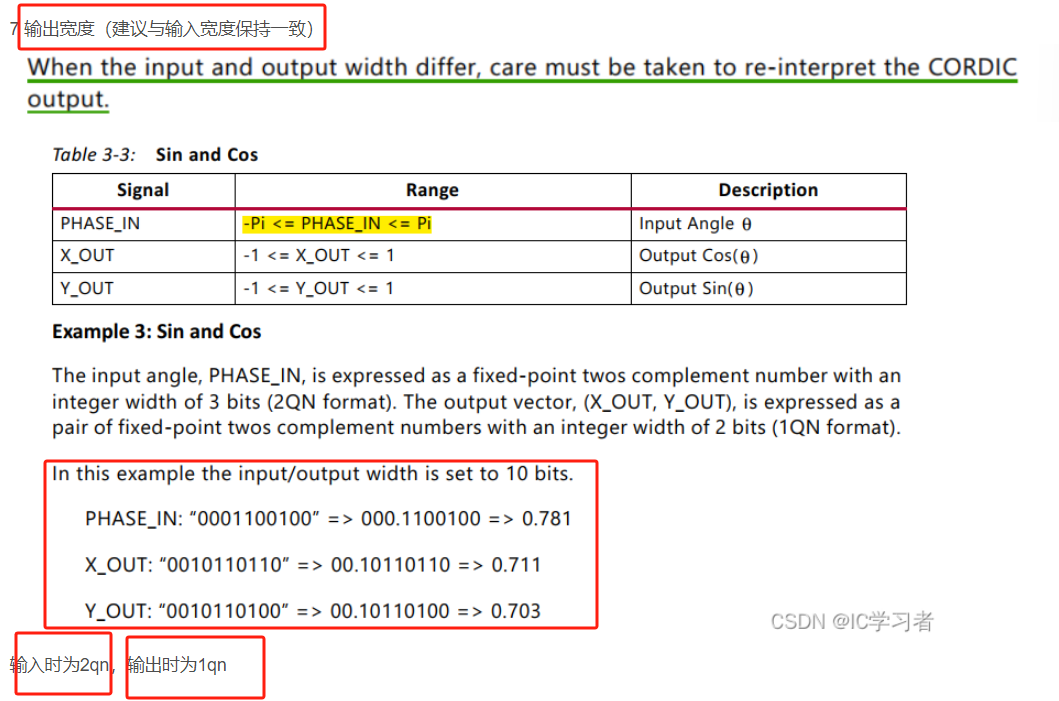

输入输出位宽不一样

,输入位宽是2qn,因为输入的时候还有可能大于一,但是计算sin和cos的话,值在-1到1之间,那么就只需要1qn