基于TSMC 12nm ARM A55 upf flow后端设计实现训练营将于6月中旬正式开班!小班教学!目前还有3个名额,招满为止!有需要可以私信小编 ic-backend2018报名。吾爱IC社区所有训练营课程均为直播课!

这个课程支持升级成双核A55 Top后端训练营!

T12 A55后端训练营简介:

主时钟频率:>= 2.5GHz tt1v85c +rcworst85c

设计规模:140万instance

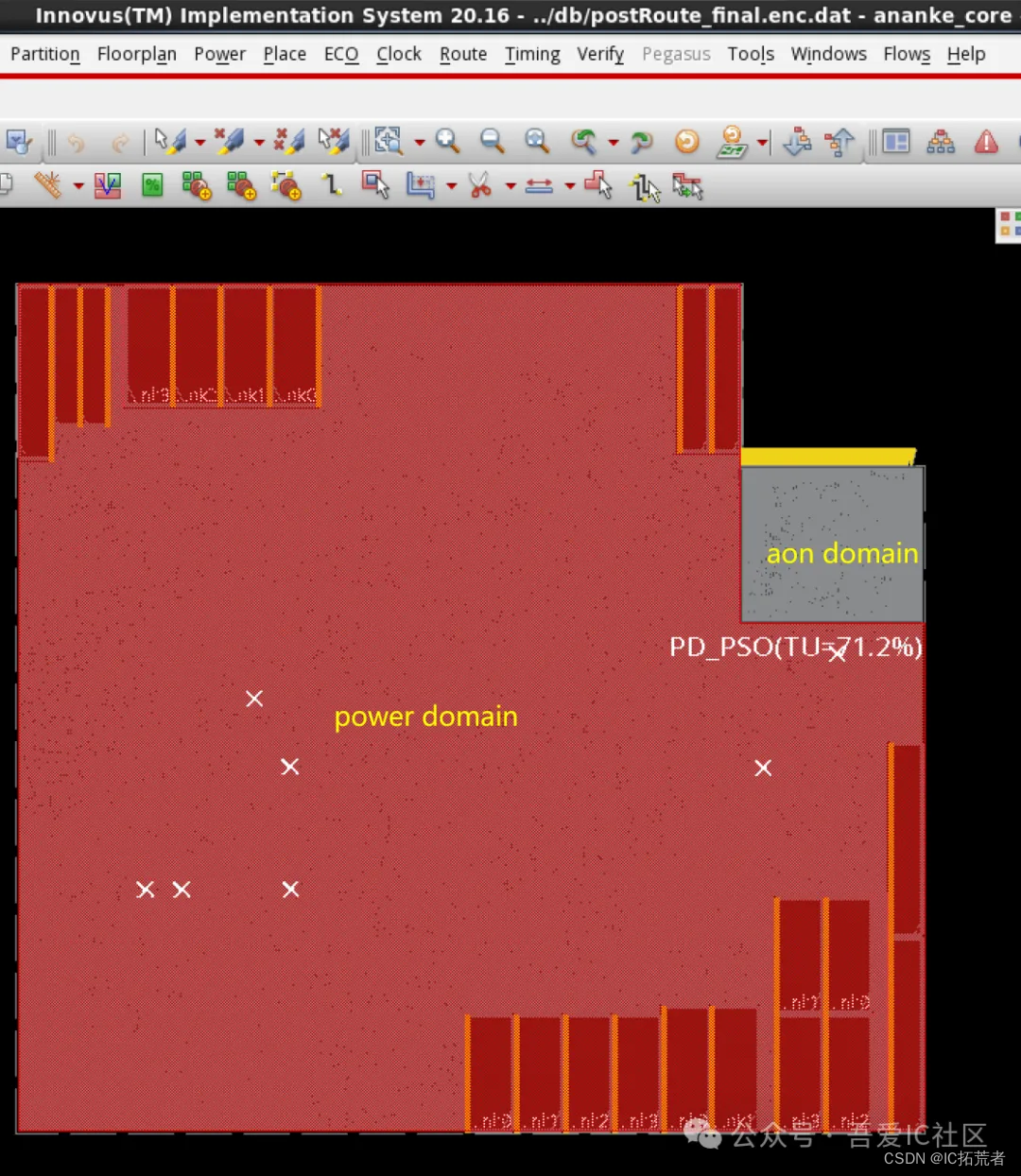

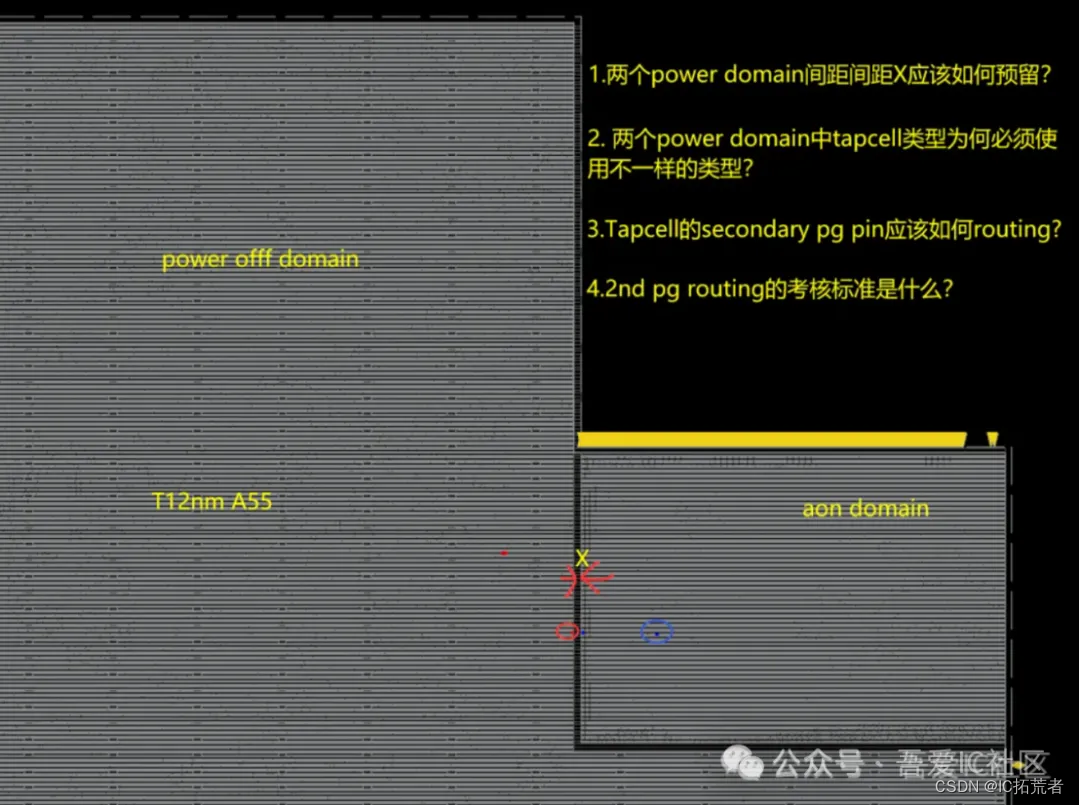

Power Domain数量:2个

实现方式:低功耗模块级UPF Flatten实现 (UPF Flow)

项目成果:Timing Signoff Timing Clean,DRC,Antenna,LVS clean

涉及EDA工具:Innovus,Starrc,PrimeTime,Calibre

授课形式:直播课+每日问题解答+远程协助。每周直播2次,每次近2小时。

课程费用:原价7900元(现价6900元)

今天给大家分享TSMC 12nm高频遇到的几个base layer drc violation及其解决方法。这些DRC Violation均来自训练营学员做项目遇到的问题。

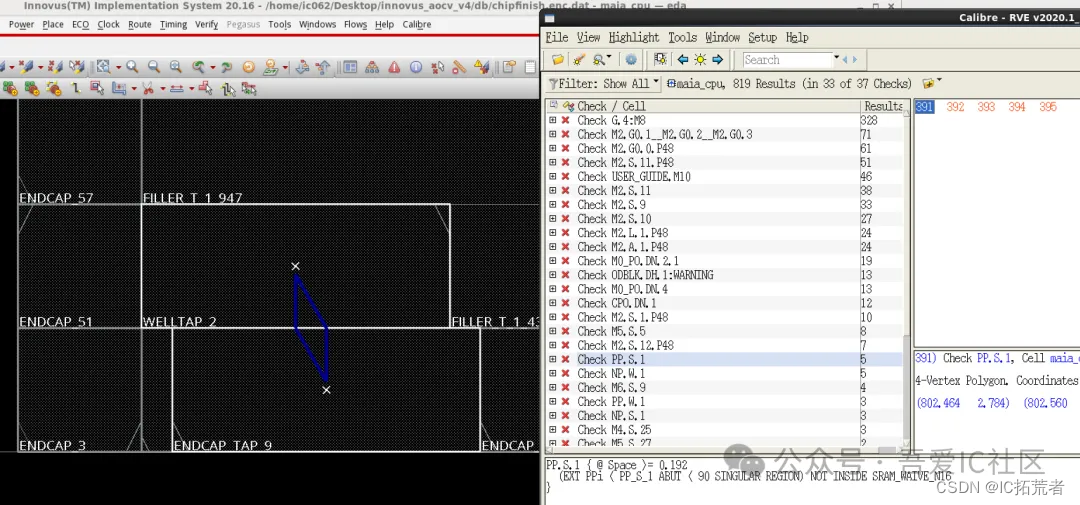

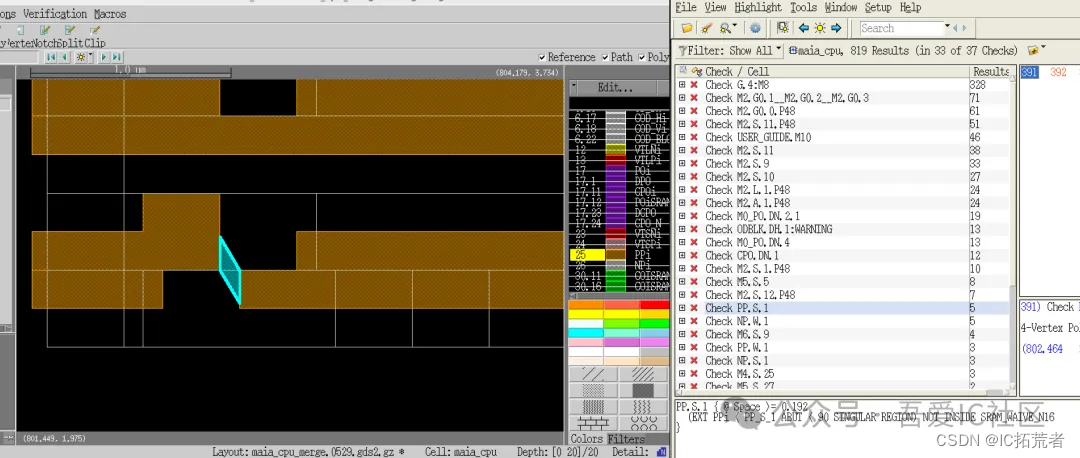

1)PP.S.1/NP.S.1

在传统28nm工艺实现中,两个tapcell或endcap 贴在一起并不会引起drc violation。但在这个12nm先进工艺中,tapcell是不允许出现abutment的情况。

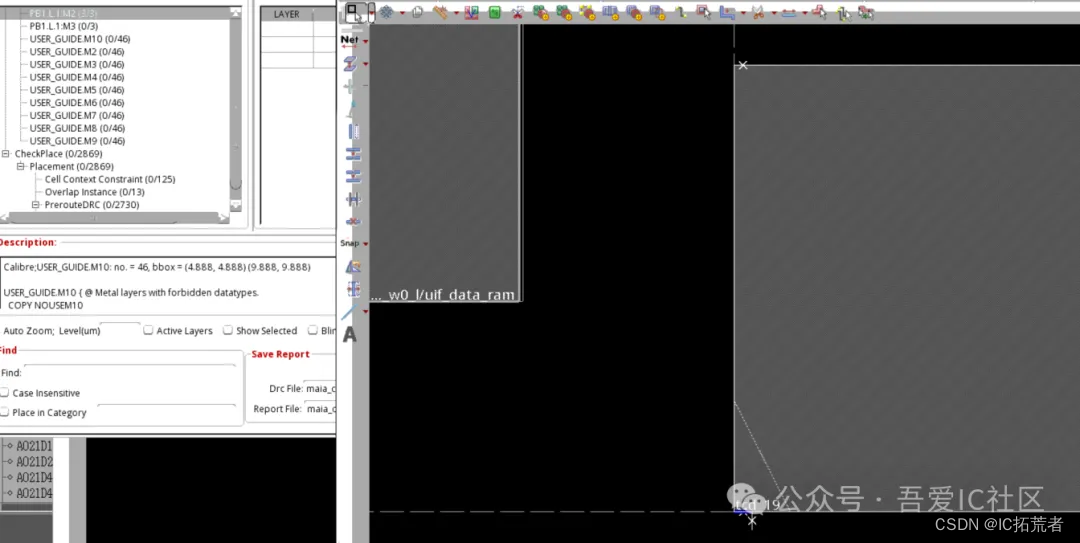

由于PR工具Innovus中看不到base layer的层次,所以我们通过calibre查看gds可以看到如下所示的PP layer间距不满足设计规则要求。

解决这类Calibre DRC Violation主要有两种方法:

- 在PR Flow的floorplan阶段添加tapcell添加avoidAbutment即可自动解决这类drc violation

addWellTap -cell TAPCELLBWP6T16P96CPD -cellInterval 48 -checkerBoard -check_channel -prefix WELLTAP -avoidAbutment

- 手工挪tapcell

这种适用于DRC Violation数量不多的场景,比如这个案例就可以使用这种方法。

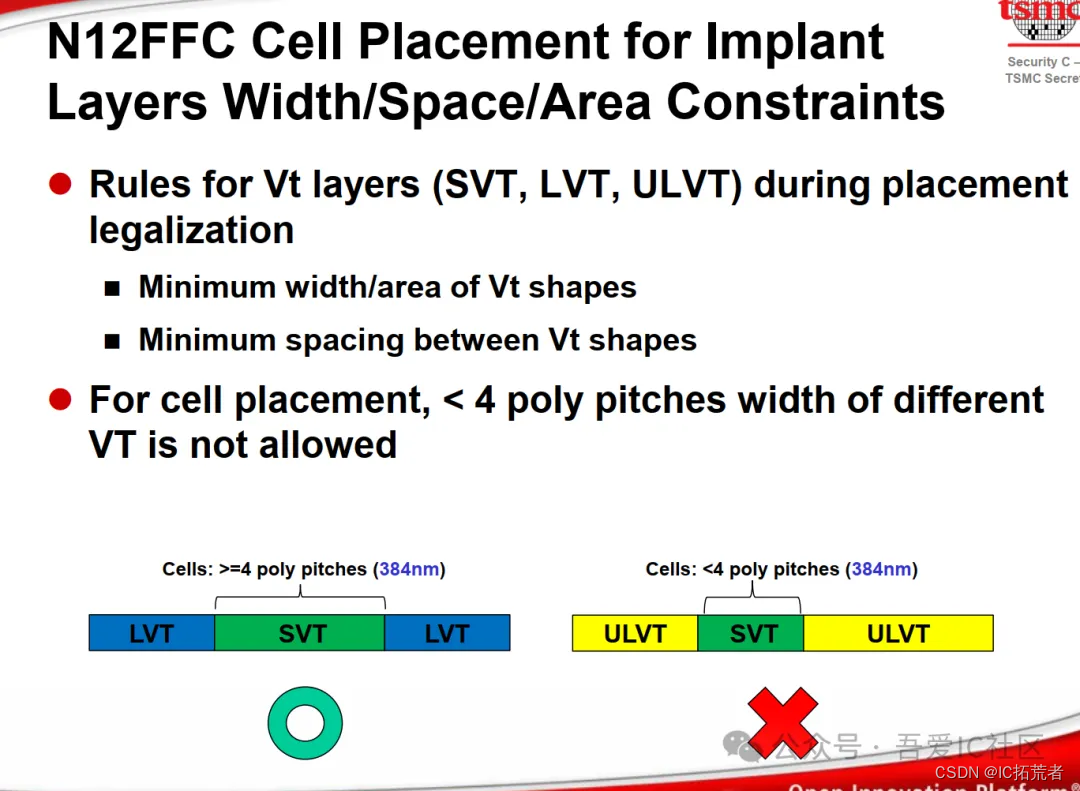

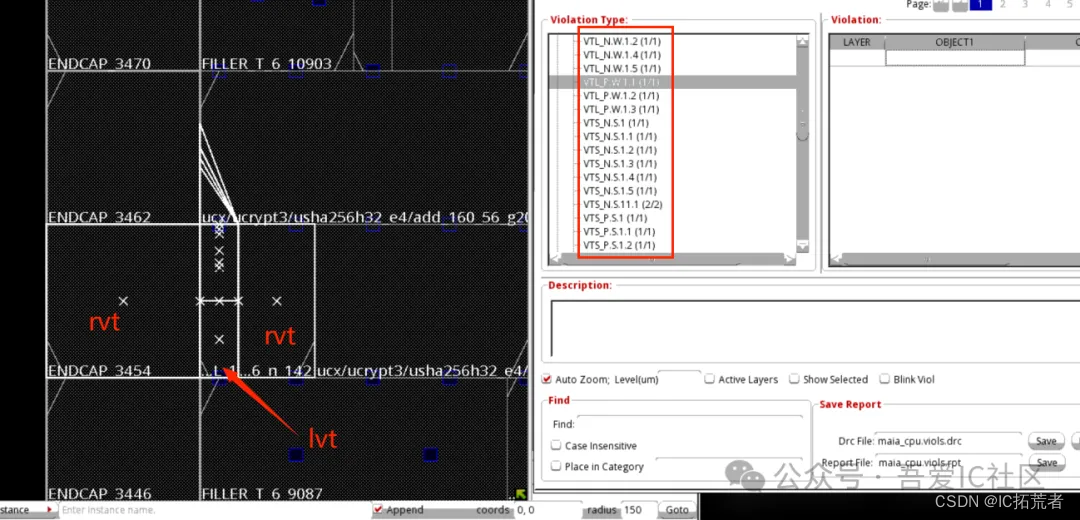

2)VTL_N_W.1.1/VTL_P_W.1.1

在 TSMC12nm 实现中,当相同VT cell 之间间距小于 4 个 site 的时候,这个时候中间位置就只能加相同阈值的 stdcell 进去,比如下图所说的,ULVT 和 ULVT 之间的间距如果小于 4 个 site 的宽度,也就是 4 个 poly pitch 间距,这个时候中间就必须插 ulvt,不能插其他阈值的 standard cell,否则就会有VT的间距问题。当间距大于 4 个 site 宽度,这个时候就没有限制了。

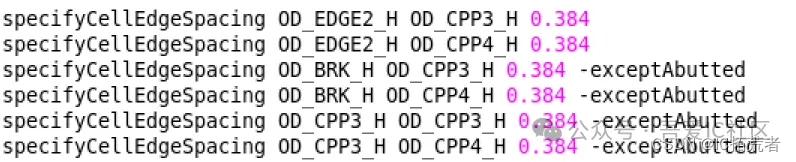

这个在咱们12nm A72后端训练营直播课也是反复强调过这点。我们需要在placement阶段加入对应的cell edge spacing约束。

我们把Calibre DRC结果导入Innovus后,可以看到的确有两颗RVT之间存在一个较小的LVT Filler Cell。

所以,这个DRC Violation出现的原因有两个。第一个是工具能力有限,最后会残留几个filler vt插错的情况,这个类似DRC无法完全修干净一样。第二个是placemnet阶段没有加好placeMode导致大规模这类drc violation的情况。

3)PO.S.22.6

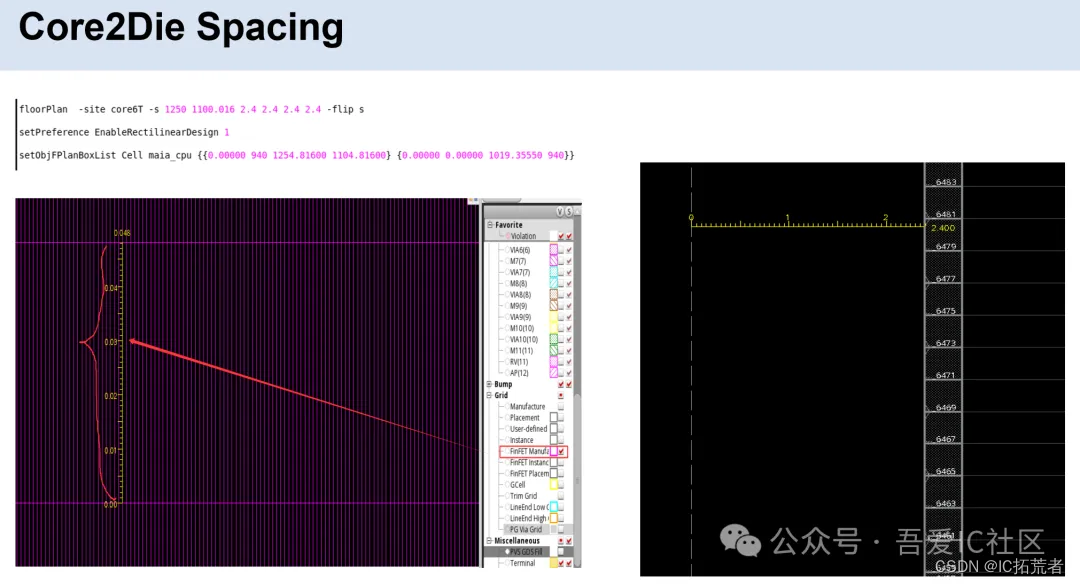

这类DRC Violation是因为在floorplan阶段没有指定好一个合理的core2die值。core2die和memory 的 halo 宽度都需要设置为 0.048 的整数倍。这样做之后,我们就可以从源头上解决这类floorplan带来的base layer drc。

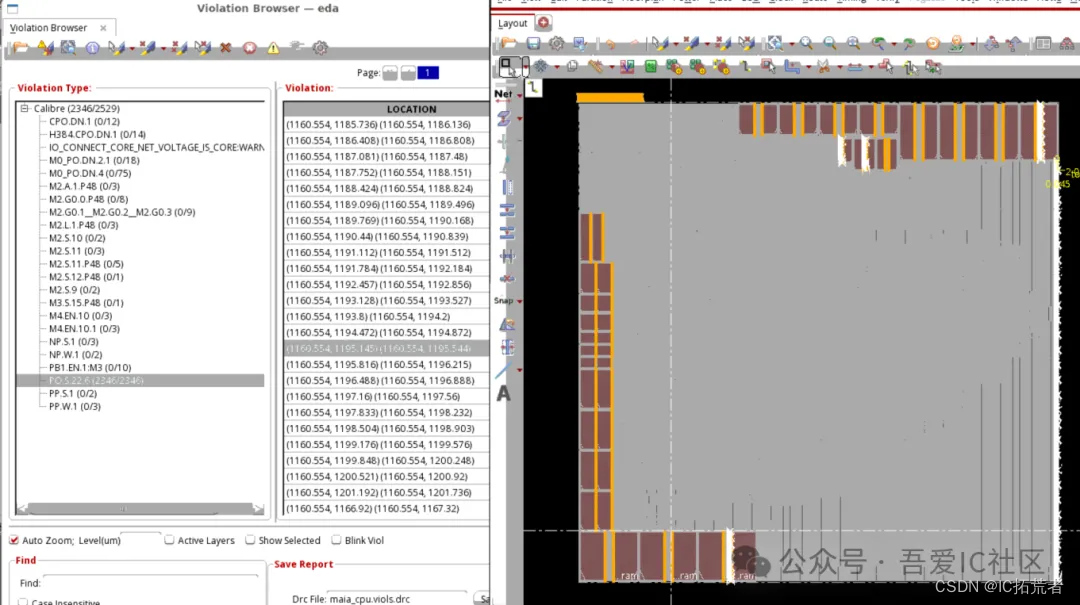

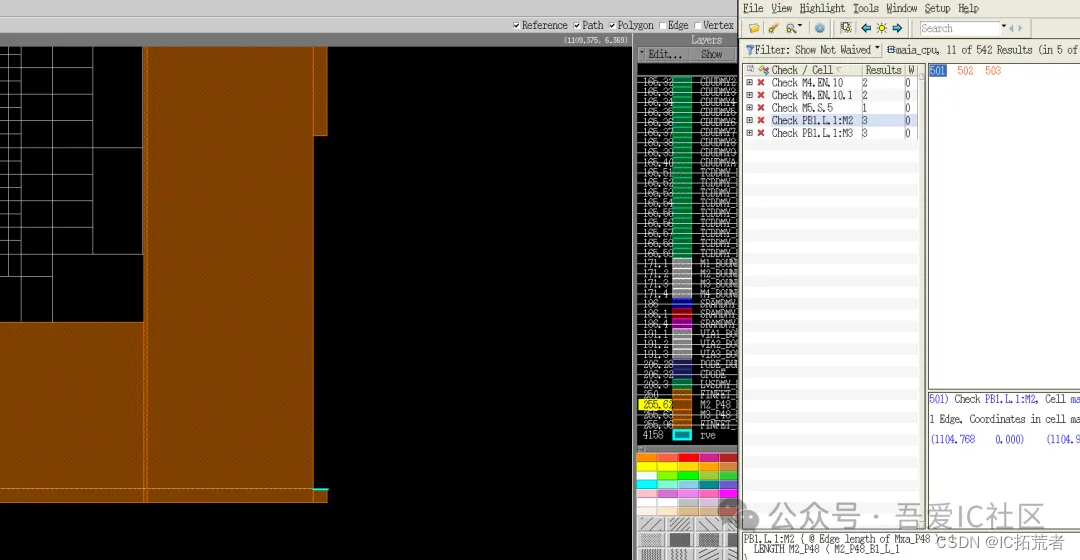

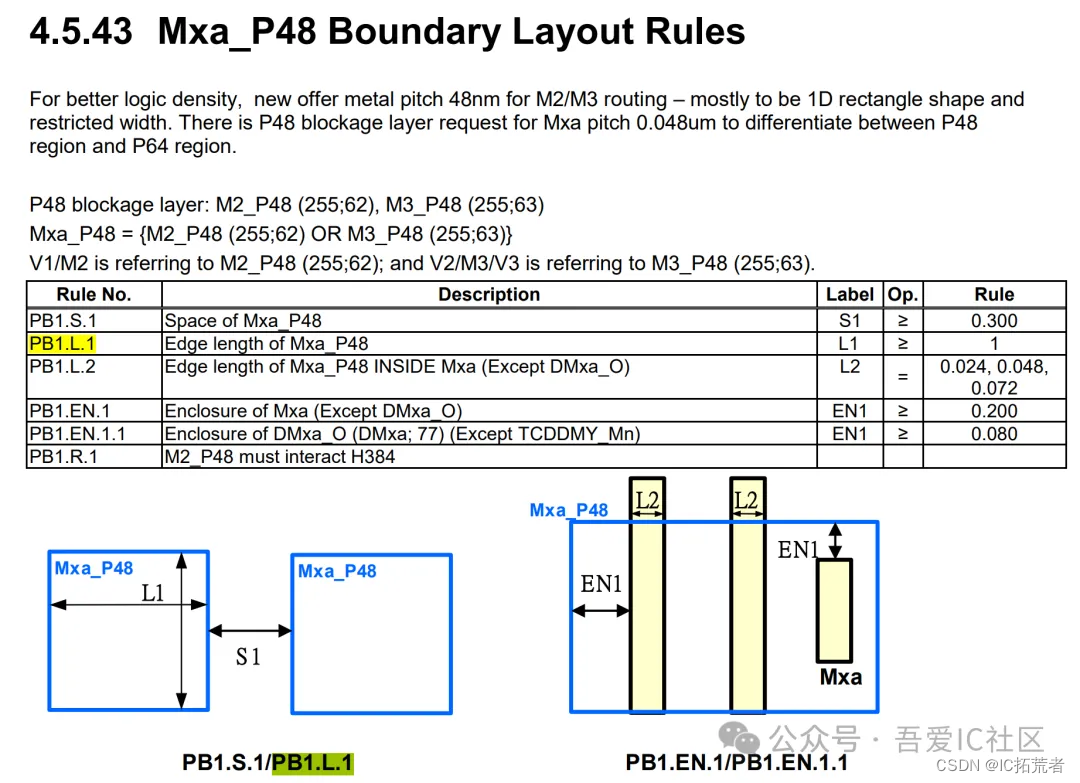

4)PB.L.1

通过Calibre DRC Violation的描述,我们知道这是关于M2_P48和M3_P48 Layer length不够的问题。

如果一开始看不太懂这类drc violation,我们可以查阅T12 design manual中对应drc violation的文字描述和图形示意图。

出现这类DRC Violation主要原因有两个。

第一个是报P48 Layer没有盖好!

解决方案如下:

createSpecialDrcRegion -layer M2_P48 -extendOuterY 0.2 -extendOuterX 0.2 -insts [dbGet [dbGet -p2 top.insts.cell.baseClass block].name]

createSpecialDrcRegion -layer M3_P48 -extendOuterY 0.2 -extendOuterX 0.2 -insts [dbGet [dbGet -p2 top.insts.cell.baseClass block].name]

第二种是设计中存在未摆放的TCD 或memory!本案例就是学员在添加TCD Cell时存在一颗未摆放到core区域的TCD cell。