目录

[1 认识TIM1和TIM8](#1 认识TIM1和TIM8)

[2 TIM1和TIM8的特性](#2 TIM1和TIM8的特性)

[3 TIM1和TIM6时基和分频](#3 TIM1和TIM6时基和分频)

[3.1 时基单元](#3.1 时基单元)

[3.2 预分频](#3.2 预分频)

[3.3 时基和分频相关寄存器](#3.3 时基和分频相关寄存器)

[3.3.2 TIMx_PSC](#3.3.2 TIMx_PSC)

概述

本文主要介绍STM32高级定时器TIM1和TIM8的功能,还介绍了与之相关的寄存器的配置参数。包括:分频计数,时间基准等内容。

1 认识TIM1和TIM8

高级控制定时器(TIM1和TIM8)由一个16位自动重新加载计数器驱动通过可编程预分频器。它可以用于多种功能:

测量输入的脉冲长度信号(输入捕获)

生成输出波形(输出比较,PWM、PWM等)

死区插入的互补PWM

脉冲长度和波形周期可以从几微秒调制到几微秒毫秒。可通过使用定时器预分频器和RCC时钟控制器预分频器来实现脉冲长度和波形周期的参数设置。高级控制(TIM1和TIM8)和通用(TIMx)定时器完全独立,不共享任何资源。

2 TIM1和TIM8的特性

| 索引 | 功能描述 |

|---|---|

| 1 | 16位计数功能: 1)加计数 2)减计数 3)加/减计数 4)自动重载计数 |

| 2 | 16位可编程预分频器,允许对计数器时钟进行分频(也可"动态") 频率乘以1和65536之间的任何因子。 |

| 3 | 最大实现4个独立通道工作: 1)输入捕获 2)输出比较 3)自动输出PWM( 边缘和中心对齐模式 ) 4)单脉冲模式输出 |

| 4 | 具有可编程死区时间的互补输出 |

| 5 | 用外部信号控制定时器并互连的同步电路 几个定时器在一起。 |

| 6 | 重复计数器,仅在给定周期数后更新定时器寄存器 计数器。 |

| 7 | 断开输入,使计时器的输出信号处于重置状态或已知状态 |

| 8 | 以下事件的中断/DMA生成: 1)更新:计数器上溢/下溢,计数器初始化(通过软件或内部/外部触发器) 2)触发器事件(计数器启动、停止、初始化或通过内部/外部触发器计数) 3)输入捕获 输出比较 打断输入 |

| 9 | 支持增量(正交)编码器和霍尔传感器电路进行定位目的 |

| 10 | 外部时钟或逐周期电流管理的触发器输入 |

3 TIM1和TIM6时基和分频

3.1 时基单元

可编程高级控制定时器的主块是一个16位计数器,其相关的自动重新加载寄存器。计数器可以向上计数、向下计数或同时向上计数和向下计数。这个计数器时钟可以被预分频器分频。

计数器、自动重新加载寄存器和预分频器寄存器可以通过写入或读取软件即使在计数器运行时也是如此。

时基单位包括:

1)计数寄存器:TIMx_CNT

2)分频寄存器:TIMx_PSC

3)自动重载寄存器:TIMx_ARR

4)重复计数寄存器:TIMx_RCR

自动重新加载寄存器已预加载。写入或读取自动重新加载寄存器访问预加载寄存器。预加载寄存器的内容被传输到影子寄存器永久或在每次更新事件(UEV)时,取决于自动重新加载TIMx_CR1寄存器中的预加载使能位(ARPE)。当计数器达到溢出(或向下计数时下溢),并且如果TIMx_CR1寄存器中的UDIS位等于0 。它也可以由软件生成。更新的生成事件将针对每个配置进行详细叙述。

计数器由预分频器输出CK_CNT计时,仅当TIMx_CR1寄存器中的计数器启用位(CEN)已设置(另请参阅从属模式控制器描述以获得有关计数器启用的更多详细信息)。

注意:

在TIMx_CR1中设置CEN位后,计数器开始计数1个时钟周期登记。

3.2 预分频

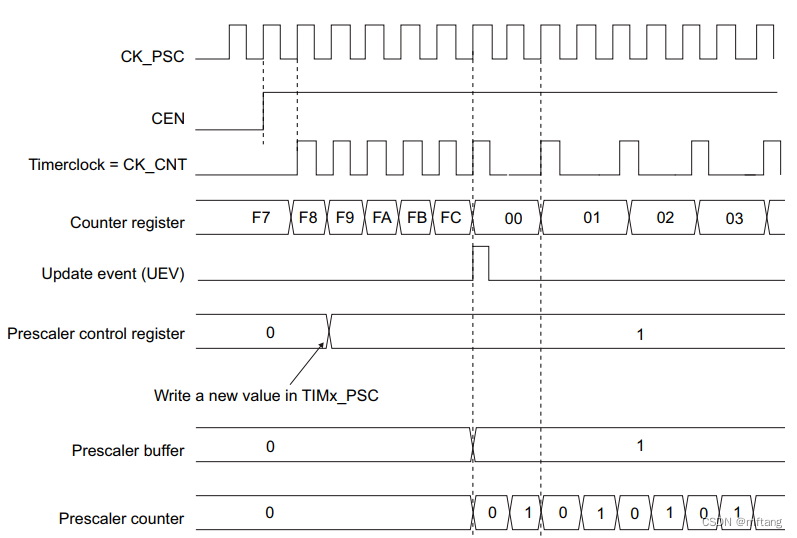

预分频器可以将计数器时钟频率除以1和65536之间的任何因子。它基于通过16位寄存器(在TIMx_PSC寄存器中)控制的16位计数器。它可以在缓冲该控制寄存器时进行动态更改。新的预分频器比率为在下一次更新事件中考虑。

几个动态改变计数器值的实例:

1)预分频器分频从1变为2的计数器时序图

2)预分频器分频从1变为4的计数器时序图

3.3 时基和分频相关寄存器

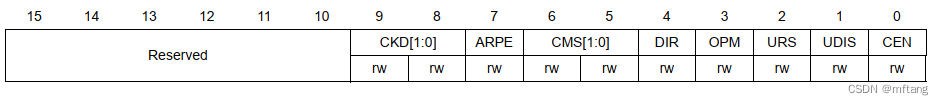

3.3.1TIMx_CR1

TIM1 and TIM8 control register 1 (TIMx_CR1)

Address offset: 0x00

Reset value: 0x0000

参数介绍

Bits 9:8 CKD[1:0]: 时钟分频

该比特字段指示定时器时钟(CK_INT)频率与死区时间发生器和数字滤波器使用的死区时间和采样时钟(tDTS)(ETR、TIx):

00: tDTS=tCK_INT

01: tDTS=2*tCK_INT

10: tDTS=4*tCK_INT

11: Reserved, do not program this value

Bit 7 ARPE::自动重载使能

0: TIMx_ARR register is not buffered

1: TIMx_ARR register is buffered

Bits 6:5 CMS[1:0]: 居中对齐模式选择

00:边缘对齐模式。计数器根据方向位向上或向下计数(目录)。

01:居中对齐模式1。计数器交替向上和向下计数。输出比较设置输出中配置的通道的中断标志(TIMx_CCMRx寄存器中的CCxS=00)只有在计数器倒计时时。

10:居中对齐模式2。计数器交替向上和向下计数。输出比较设置输出中配置的通道的中断标志(TIMx_CCMRx寄存器中的CCxS=00)只有当计数器正在计数时。

11:居中对齐模式3。计数器交替向上和向下计数。输出比较设置输出中配置的通道的中断标志(TIMx_CCMRx寄存器中的CCxS=00)无论是在计数器向上计数还是向下计数时。

Bit 4 DIR: 计数方向

0: 增计数

1:减计数

Bit 3 OPM: 单脉冲模式

0: 计数器未在更新事件中停止

1:计数器在下一次更新事件时停止计数(清除位CEN)

Bit 2 URS: 更新请求源

该位由软件设置和清除,以选择UEV事件源。

0:如果启用,以下任何事件都会生成更新中断或DMA请求。这些事件可以是:

1)计数器上溢/下溢

2)设置UG位

3)通过从属模式控制器更新生成

1:只有计数器上溢/下溢才会生成更新中断或DMA请求,如果启用。

Bit 1 UDIS: 禁止更新

该位由软件设置和清除,以启用/禁用UEV事件生成。

0:UEV已启用。更新(UEV)事件由以下事件之一生成:

1)计数器上溢/下溢

2)设置UG位

3)通过从属模式控制器更新生成

1:UEV已禁用。未生成Update事件,影子寄存器保留其值(ARR、PSC、CCRx)。然而,如果UG位为设置,或者如果从从属模式控制器接收到硬件重置。

Bit 0 CEN: 计数使能

0: 计数失能

1:计数使能

3.3.2 TIMx_PSC

TIM1 and TIM8 prescaler (TIMx_PSC)

Address offset: 0x28

Reset value: 0x0000

参数介绍

Bits 15:0 PSC[15:0]: 分频值

计数器时钟频率(CK_CNT)等于fCK_PSC/(PSC[15:0]+1)。PSC包含在每次更新事件时要加载到活动预分频器寄存器中的值(包括通过TIMx_EGR寄存器的UG位或通过在"重置模式"下配置时触发控制器)。