@TOC

一、System-Verilog实现流水灯

1.流水灯代码

led_flow.sv

c

module led_flow (

input logic clk, // 时钟信号

input logic rst_n, // 复位信号(低有效)

output logic [7:0] led // 8位LED输出

);

logic [23:0] counter; // 24位计数器,用于产生慢时钟信号

// 计数器逻辑

always_ff @(posedge clk or negedge rst_n) begin

if (!rst_n)

counter <= 24'd0;

else

counter <= counter + 1;

end

// LED流水灯逻辑

always_ff @(posedge counter[23] or negedge rst_n) begin

if (!rst_n)

led <= 8'b0000_0001;

else

led <= {led[6:0], led[7]};

end

endmoduletestbench

c

module led_flow_tb;

logic clk;

logic rst_n;

logic [7:0] led;

// 实例化待测试的流水灯模块

led_flow uut (

.clk(clk),

.rst_n(rst_n),

.led(led)

);

// 时钟信号生成

initial begin

clk = 0;

forever #10 clk = ~clk; // 50MHz时钟周期为20ns

end

// 测试逻辑

initial begin

// 初始化信号

rst_n = 0;

#100;

rst_n = 1;

// 仿真运行一段时间后结束

#1000000;

$stop;

end

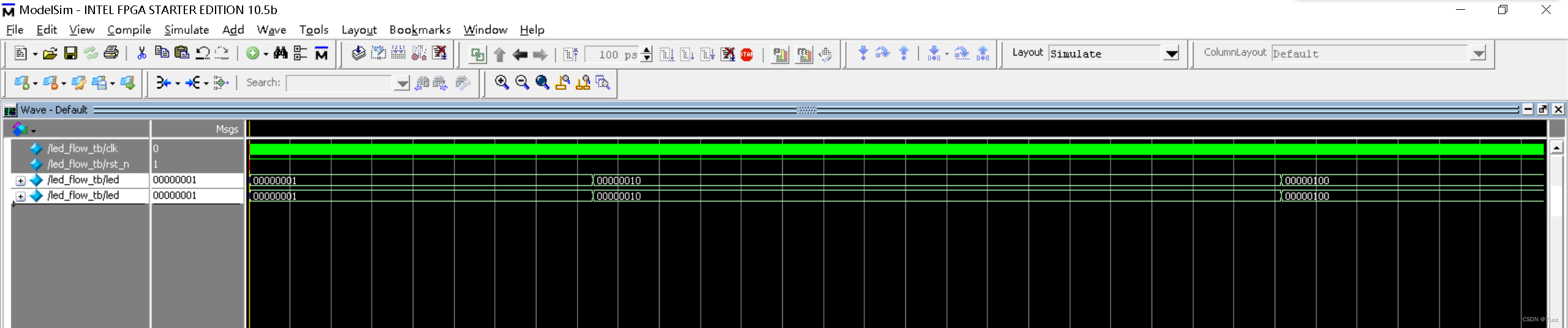

endmodule2.实验结果

3.testbench