帧同步和bitslip操作:

之前做了比特时钟对齐操作,现在要做帧同步,确定哪些比特组成一个有效字节;

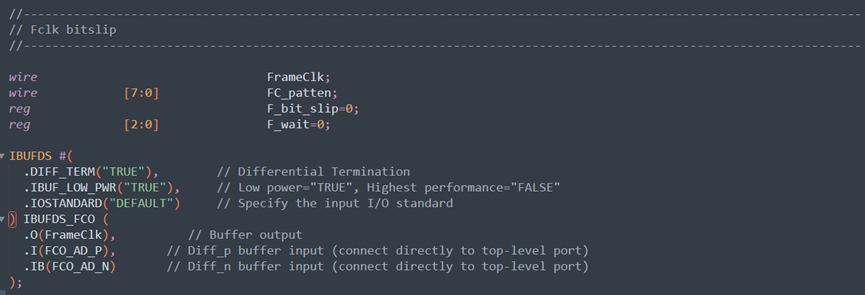

FCO_AD_P和FCO_AD_N经过IBUFDS后,转成单端信号FrameClk,这里FCO过一个IBUFDS,之前DCO也过一个IBUFDS,后面的各通道的DCO差分信号也要过一个IBUFDS,大家都加一个IBUFDS延时能大概保持FCO和DCO单端信号的对齐;

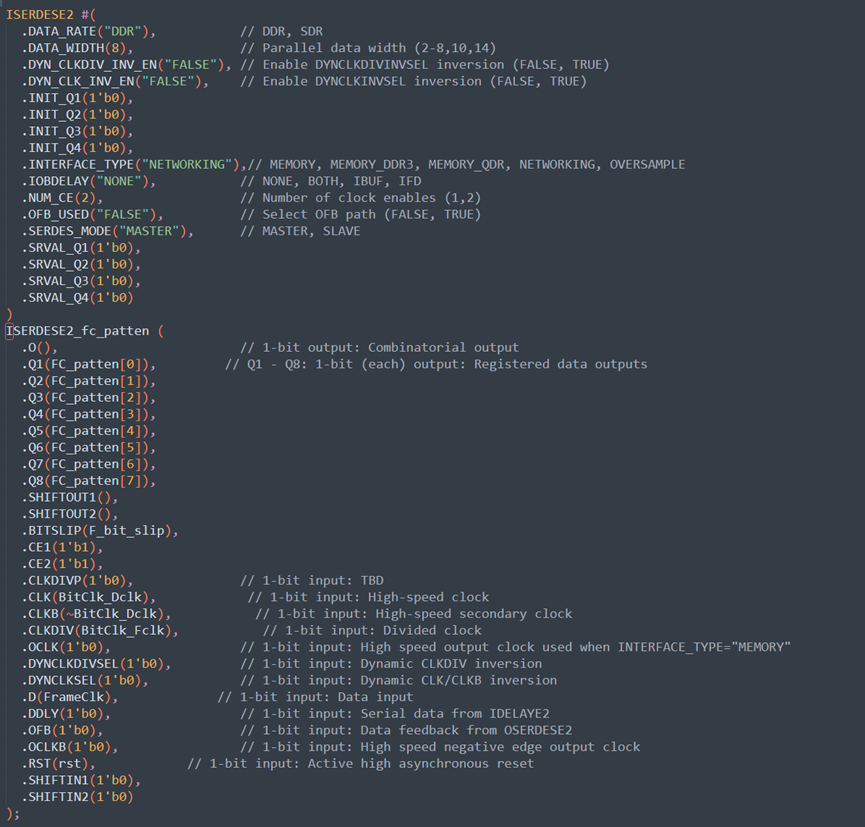

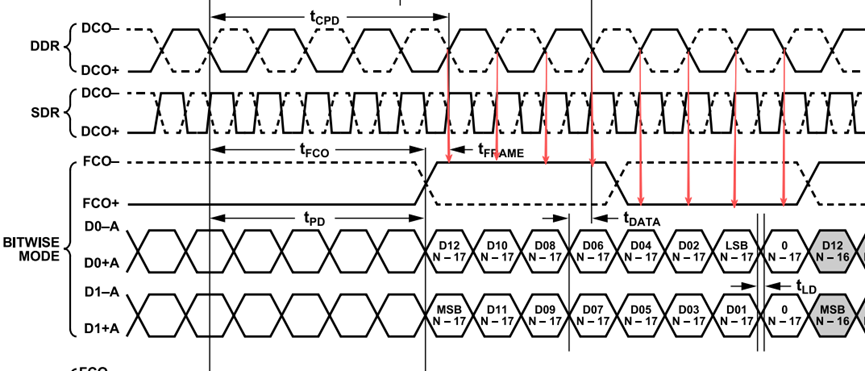

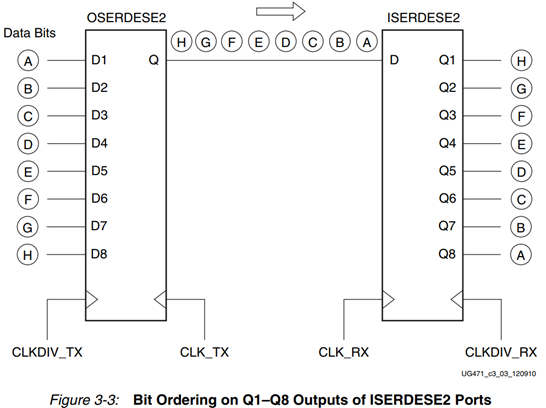

使用8:1,DDR模式的ISERDESE2,使用之前对齐的比特时钟BitClk_Dclk去采样FrameClk帧时钟,采集的8bit FC_patten信号,则表示了此刻FPGA内部要使用的数据采样时钟和帧时钟或者说和通道数据的相对位置;

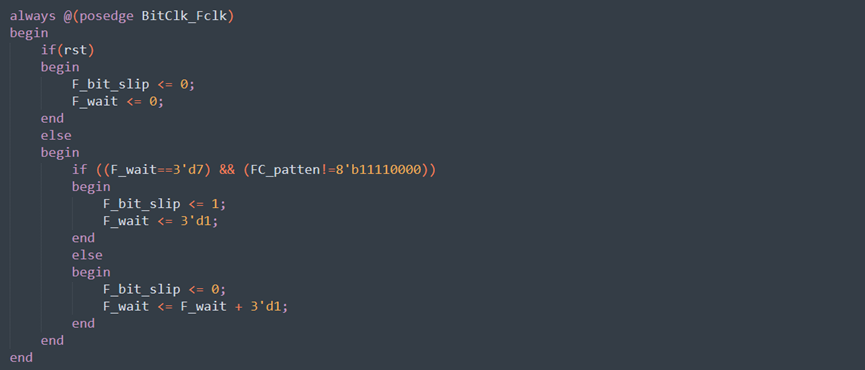

见上方逻辑,F_wait一直做循环递增1,当值为7时,判断FC_patten值是否为8'b11110000,这个值是是根据这里时序图,在一个串行字节传输的时间段里,FCO前4个比特为高,后4个比特为低,

且根据ISERDESE2的串转并时序,先接收的比特,放在8比特高位,所以匹配值为8'b11110000,

当在比较时刻,发现判断值不等于想要的值,就会拉高一拍F_bit_slip,ISERDESE2组件将进行一次bitslip操作,一直到每次F_wait=7时,判断值都为8'b11110000,bitslip就不会再进行;

通道数据采样:

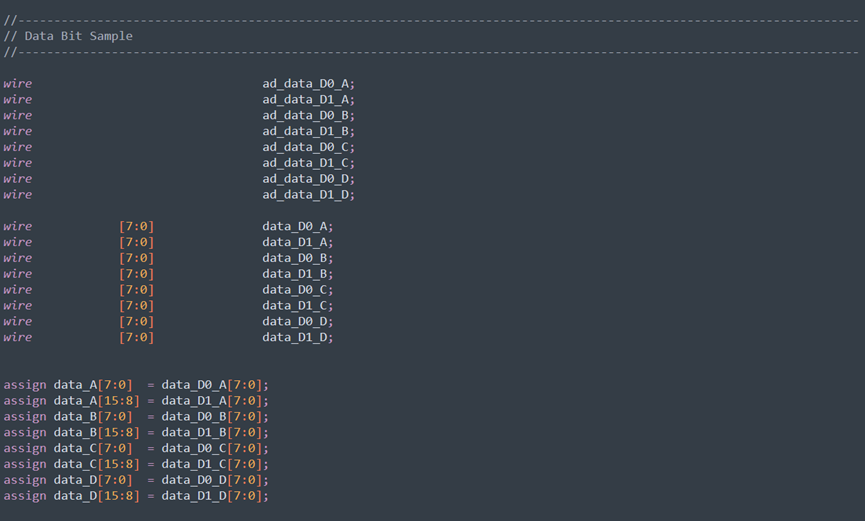

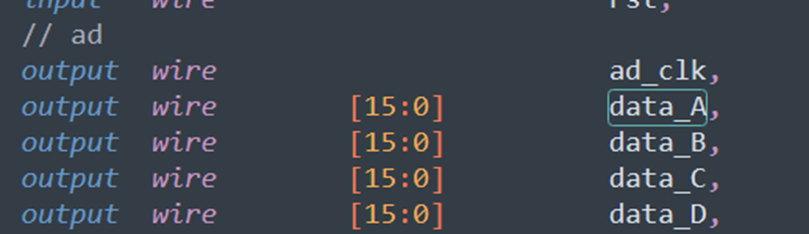

Ad9253有4路数据,16bit DDR模式,但是每路数据分为了两个数据通道,共有A通道D0-A、D0+A、D1-A、D1+A,B通道D0-B、D0+B、D1-B、D1+B,C通道D0-C、D0+C、D1-C、D1+C,D通道D0-D、D0+D、D1-D、D1+D;

这里就列出A通道的处理逻辑,其他几个通道与之相同;

8个通道字节数据,拼接为4个通道16bit后输出,

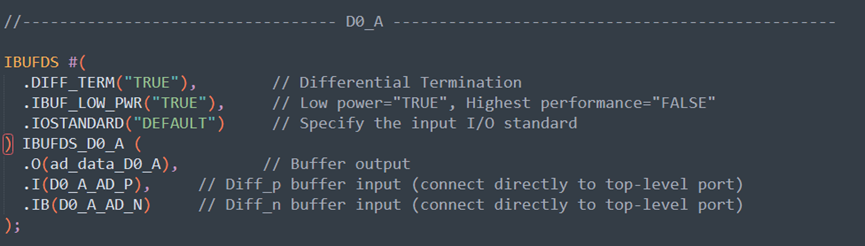

D0_A_AD_P和D0_A_AD_N,差分转单端为ad_data_D0_A,过这个IBUFDS,保持与FCO接近的延时值,

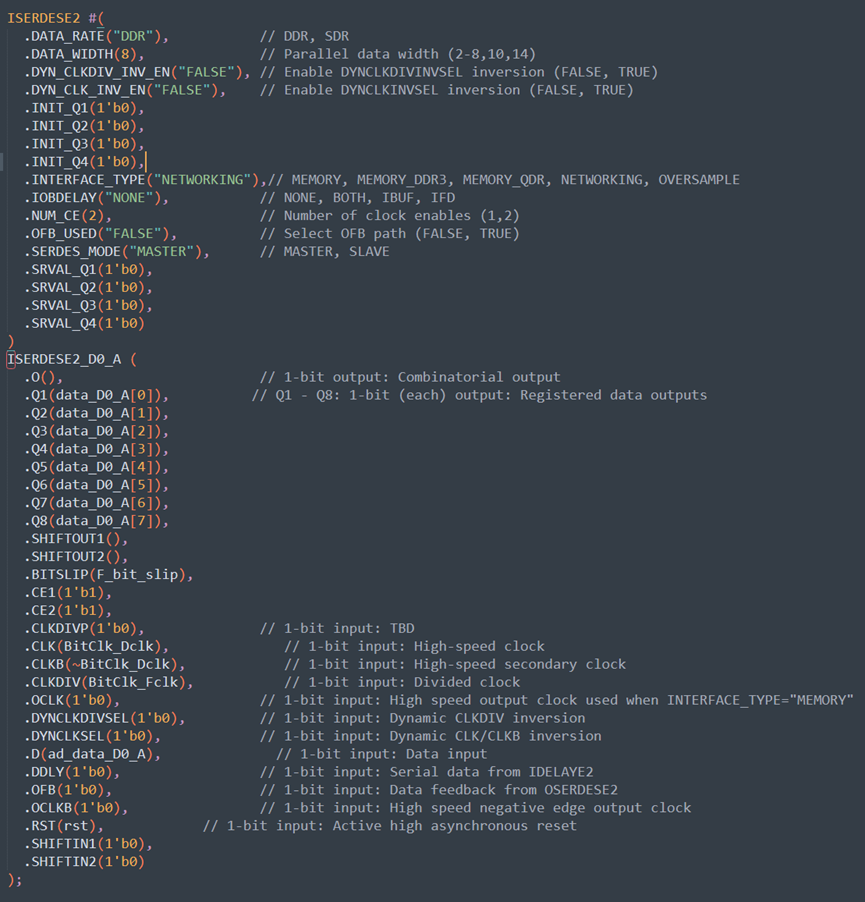

ad_data_D0_A信号被BitClk_Dclk比特时钟采样,且通道数据的ISERDESE2也使用FCO的ISERDESE2使用的相同的F_bit_slip信号,也就是FCO帧同步逻辑进行bitslip时,实际上是所有的通道数据的ISERDESE2都会同时进行bitslip操作,保持数据和帧时钟的同步,最后采样得到的数据data_D0_A,则是用于拼接的8个通道中的一个,

其他7个数据通道,也是过IBUFDS后,使用BitClk_Dclk比特时钟采样,使用F_bit_slip移位,采样得到的8个8比特数据,在此处进行拼接后输出,

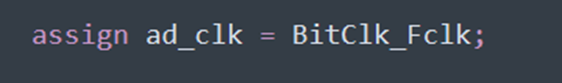

这4个通道的16比特数据输出到外部使用,和BitClk_Fclk作为其同步时钟,一起输出;

下一节进行整体的数据仿真验证操作;

本文章由威三学社出品

对课程感兴趣可以私信联系