描述

超级逻辑区(SLR)是包含在堆叠硅中的单个FPGA芯片

互连(SSI)设备。堆叠式硅互连(SSI)技术使用无源硅

具有微凸块和硅通孔(TSV)的内插器,用于组合多个FPGA管芯

切片,称为超级逻辑区域(SLR),集成到单个封装中。

每个SLR都包含大多数Xilinx FPGA设备通用的有源电路,并且

通过在硅中介层上发现的超长线(SLL)连接。请参阅此链接

在Vivado设计套件的超快设计方法指南(UG949)[参考文献24]中

有关使用SSI组件的更多信息。

相关对象

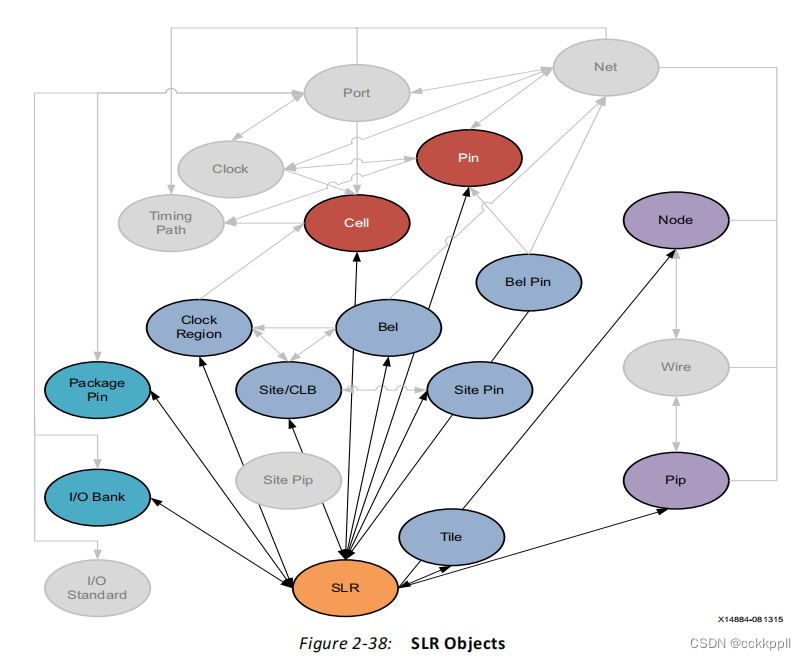

超级逻辑区域(SLR)是XilinxFPGA架构或器件的芯片。如所示

图2-38,第133页,每个单反包含时钟区域、瓦片、站点、站点引脚、贝尔、贝尔引脚,

节点、点、单元、引脚、I/O组和封装引脚。您可以找到与关联的单反

这些不同类型的对象中的每一个,使用Tcl命令,例如以下命令

返回指定单元格分配给的SLR:

get_slrs-属于[get_cells DataIn_pad_0_i_IBUF[3]_inst]

您还可以查询与单反相关的时钟区域、磁贴、站点或贝尔。这个

以下Tcl命令获取与特定SLR相关联的时钟区域的I/O组:

get_iobanks-of[get_clock_regions-of[get_slrs SLR3]]

属性

可以使用report_property命令来报告SLR的特性。提到

Vivado设计套件Tcl命令参考指南(UG835)[参考文献13]了解更多信息

信息SLR对象上的属性包括以下内容,以及示例值:

Property Type Read-only Visible Value

ARCH string true true virtex7

CHIP_TYPE string true true xc7vx1140t 0

CLASS string true true slr

CONFIG_ORDER_INDEX int true true 0

IS_FABRIC bool true true 1

IS_MASTER bool true true 1

LOWER_RIGHT_CORNER int true true (0,157)

LOWER_RIGHT_X int true true 0

LOWER_RIGHT_Y int true true 157

MAX_SITE_INDEX int true true 278381

MAX_TILE_INDEX int true true 266114

MIN_SITE_INDEX int true true 185588

MIN_TILE_INDEX int true true 177410

NAME string true true SLR1

NUM_CHANNELS int true true 220

NUM_SITES int true true 92794

NUM_SLLS int true true 10780

NUM_TILES int true true 23169

NUM_TOP_CLOCK_CONNECTIONS int true true 32

NUM_TOP_DATA_CONNECTIONS int true true 10780

SLR_INDEX int true true 1

UPPER_LEFT_CORNER int true true (564,313)

UPPER_LEFT_X int true true 564

UPPER_LEFT_Y int true true 313

要报告特定SLR的属性,可以复制并粘贴以下命令

进入Vivado Design Suite Tcl外壳或Tcl控制台:

report_property -all [get_slrs <name> ]