目录

- [1.模块实例化(module instantiation)](#1.模块实例化(module instantiation))

- [2.实例数组(Array of Instances)](#2.实例数组(Array of Instances))

微信公众号获取更多FPGA相关源码:

1.模块实例化(module instantiation)

- 模块实例化时实例必须有一个名字。

- 使用位置映射时,端口次序与模块的说明相同。

- 使用名称映射时,端口次序与位置无关

- 没有连接的输入端口初始化值为x。

verilog

module comp (o1, o2, i1, i2);

output o1, o2;

input i1, i2;

. . .

endmodule

module test;

comp c1 (Q, R, J, K); // Positional mapping

comp c2 (.i2(K), .o1(Q), .o2(R), .i1(J)); // Named mapping

comp c3 (Q, , J, K); // One port left unconnected

comp c4 (.i1(J), .o1(Q)); // Named, two unconnected ports

endmodule2.实例数组(Array of Instances)

实例名字后有范围说明时会创建一个实例数组。在说明实例数组时,实例必须有一个名字 (包括基本单元实例)。其说明语法为:

<模块名字> <实例名字> <范围> (<端口>);

verilog

module driver (in, out, en);

input [2: 0] in;

output [2: 0] out;

input en;

bufif0 u[2:0] (out, in, en); // array of buffers

endmodule

verilog

module driver_equiv (in, out, en);

input [2: 0] in;

output [2: 0] out;

input en;

// Each primitive instantiation is done separately

bufif0 u2 (out[2], in[2], en);

bufif0 u1 (out[1], in[1], en);

bufif0 u0 (out[0], in[0], en);

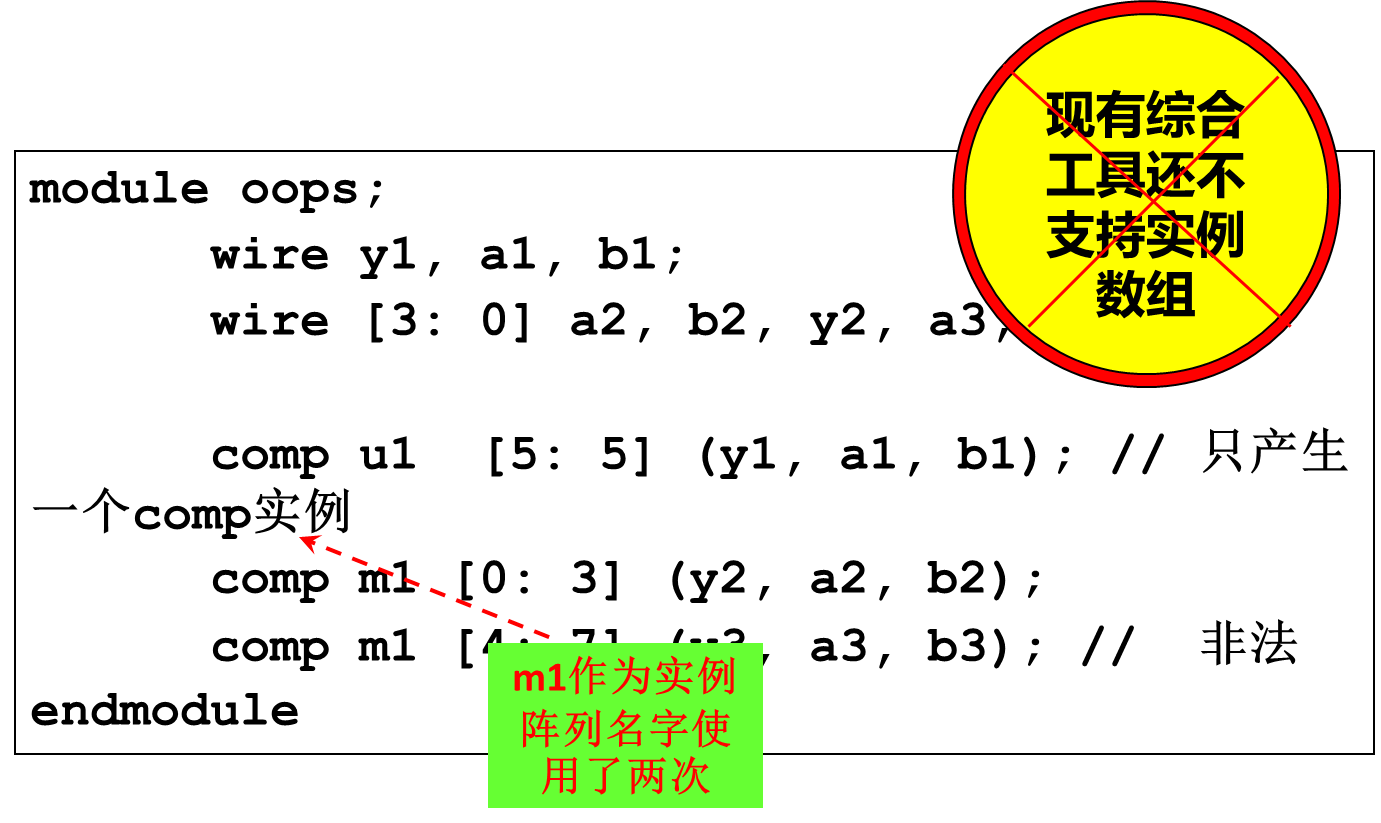

endmodule- 如果范围中MSB与LSB相同,则只产生一个实例。

- 一个实例名字只能有一个范围。

- 下面以模块comp为例说明这些情况

verilog

module oops;

wire y1, a1, b1;

wire [3: 0] a2, b2, y2, a3, b3, y3;

comp u1 [5: 5] (y1, a1, b1); // 只产生一个comp实例

comp m1 [0: 3] (y2, a2, b2);

comp m1 [4: 7] (y3, a3, b3); // 非法

endmodule微信公众号获取更多FPGA相关源码: