目录

- 1、前言

- 2、相关方案推荐

-

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- [我这里已有的 GT 高速接口解决方案](#我这里已有的 GT 高速接口解决方案)

- [我这里已有的 JESD204 高速AD接口解决方案](#我这里已有的 JESD204 高速AD接口解决方案)

- 3、工程详细设计方案

-

- 工程设计原理框图

- [JESD204B 硬件设计架构](#JESD204B 硬件设计架构)

- 信号输入设备

- AD9208芯片解读

- [纯verilog实现的JESD204B 物理层方案](#纯verilog实现的JESD204B 物理层方案)

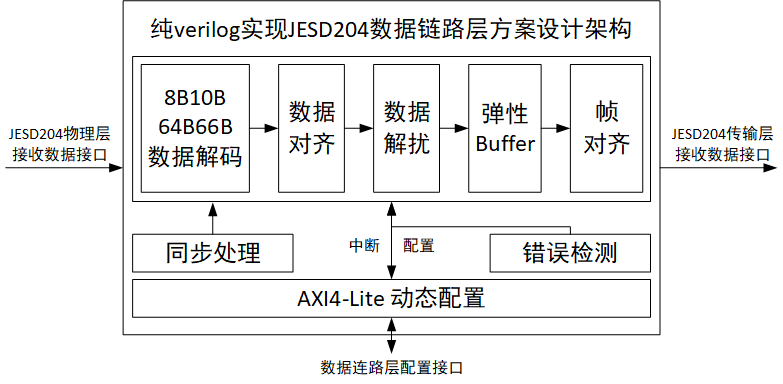

- [纯verilog实现的JESD204B 数据链路层方案](#纯verilog实现的JESD204B 数据链路层方案)

- [纯verilog实现的JESD204B 传输层方案](#纯verilog实现的JESD204B 传输层方案)

- PL端逻辑工程源码架构

- PS端软件工程源码架构

- 4、vivado工程源码1详解-->VU9P版本

- 5、工程移植说明

- 6、上板调试验证

- 7、工程代码的获取

FPGA纯verilog实现JESD204B协议,基于AD9208数据接收,提供工程源码和技术支持

1、前言

什么是JESD204B协议?

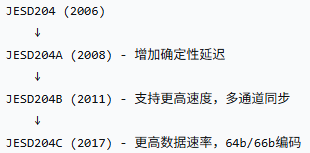

JESD204B是一种高速串行接口标准,专门用于连接数据转换器(ADC/DAC)和逻辑设备(如FPGA、ASIC)。它由JEDEC固态技术协会制定,是JESD204标准的修订版本;JESD204B协议通过其高速串行接口、确定性延迟和多通道同步能力,已成为现代高速数据采集系统的首选接口标准。FPGA凭借其并行处理能力、灵活性和可重构特性,在JESD204B系统实现中展现出显著优势,特别是在需要实时处理、多通道同步和定制化应用的场景中。随着5G、航空航天、医疗影像等领域的持续发展,JESD204B与FPGA的结合将继续推动高性能数字系统向更高速度、更高集成度和更智能化的方向发展。协议发展历程如下:

JESD204关键特性如下:

数据速率:最高达12.5 Gbps

通道数量:支持1-8个通道

编码方式:8B/10B编码

同步机制:支持确定性延迟

子类支持:Subclass 0, 1, 2

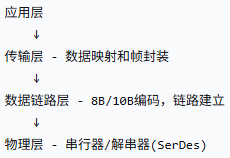

JESD204协议分层结构如下:

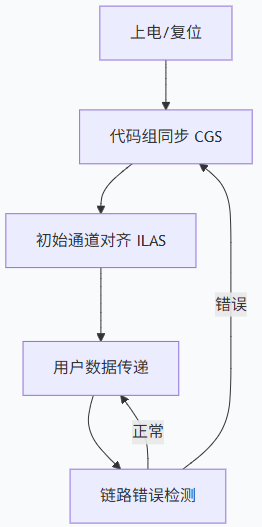

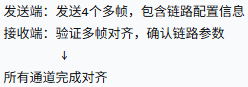

JESD204B链路建立过程如下:

JESD204B详细建立步骤如下:

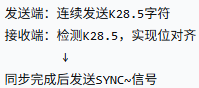

步骤1:代码组同步(CGS)

步骤2:初始通道对齐(ILAS)

步骤3:用户数据传输

正常数据传输开始

持续监控链路状态

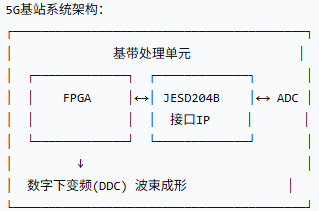

JESD204B具体应用领域

1、无线通信基础设施,如下:

应用优势:

支持大规模MIMO系统

高采样率满足5G宽带需求

多通道同步支持相控阵列

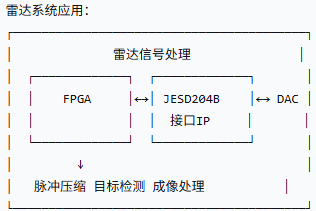

2、航空航天与国防,如下:

应用优势:

高可靠性,抗干扰能力强

支持高速数据采集和处理

适用于恶劣环境

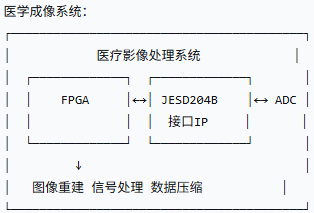

3、医疗影像设备,如下:

应用设备:

MRI(磁共振成像)

超声成像系统

CT扫描仪

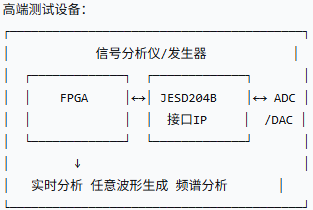

4、测试与测量仪器,如下:

FPGA实现JESD204B的优势概括

1、架构灵活性,如下:

2、主要优势对比如下:

FPGA实现JESD204B的优势详解

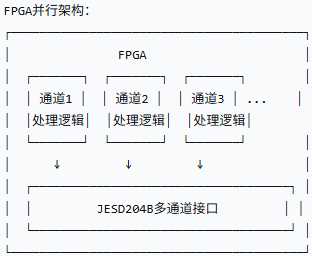

1、并行处理能力,如下:

优势:同时处理多个数据通道,实现真正的并行处理。

2、定制化信号处理,如下:

优势:在数据进入系统前完成预处理,降低后端处理负担。

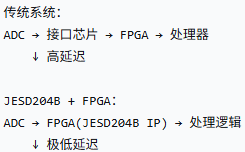

3、低延迟设计,如下:

优势:适用于需要快速响应的实时系统。

官方有Example,为何要用你这个?

Xilinx官方的确有JESD204B IP核的Example例程;

然后呢?你看得懂吗?你会照着模仿做自己的项目吗?

如果你会,那么请划走;

如果你不会,不妨看看下面的聊天记录

这位朋友用了我的JESD204B参考工程,感觉少走了一年的弯路。。。

工程概述

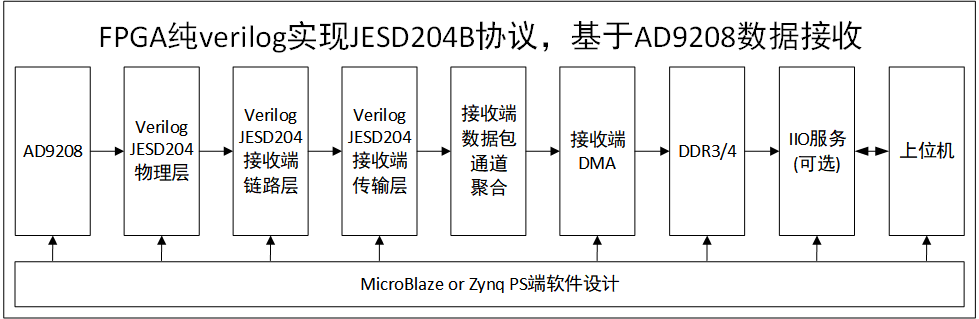

本设计使用Xilinx系列FPGA为平台,基于纯verilog实现的JESD204B协议实现AD9208数据收发,旨在为读者提供一套精简版的、基于JESD204B协议的的数据收发架构;

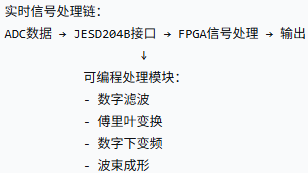

首先在由示波器产生正弦波或者使用其他信号源输入AD9208转接板;AD9208实现模数转换后将双通道AD数据通过FMC高速连接器发送到FPGA开发板的GT高速BANK;然后调用纯verilog实现的JESD204B物理层实现并行AD数据与高速低压差分串行数据接口的转换,并输出并行数据;然后调用纯verilog实现的JESD204B链路层实现JESD204B协议层解码功能,数据链路层由解码模块和控制模块两个部分构成;然后调用纯verilog实现的JESD204B传输层实现数据帧解析和格式转换;完成解码解码后的数据送入纯verilog实现的FIFO实现位宽转换和时钟域转换;然后数据送入纯verilog实现的DMA模块实现数据搬运,搬运到FPGA开发板板载DDR3中缓存;然后vitis软件端控制DMA读取AD数据通过串口打印或者通过IIO服务发送到上位机做后续处理;针对市场主流需求,本博客设计并提供1套工程源码,具体如下:

工程源码1

开发板FPGA型号为Xilinx--Virtex UltraScale±-xcvu9p-flga2104-2L-e;首先在由示波器产生正弦波或者使用其他信号源输入AD9208转接板;AD9208实现模数转换后将双通道AD数据通过FMC高速连接器发送到FPGA开发板的GTH高速BANK;然后调用纯verilog实现的JESD204B物理层实现并行AD数据与高速低压差分串行数据接口的转换,并输出并行数据;然后调用纯verilog实现的JESD204B链路层实现JESD204B协议层解码功能,数据链路层由解码模块和控制模块两个部分构成;然后调用纯verilog实现的JESD204B传输层实现数据帧解析和格式转换;完成解码解码后的数据送入纯verilog实现的FIFO实现位宽转换和时钟域转换;然后数据送入纯verilog实现的DMA模块实现数据搬运,搬运到FPGA开发板板载DDR4中缓存;然后vitis软件端控制DMA读取AD数据通过串口打印或者通过IIO服务发送到上位机做后续处理;

本博客详细描述了FPGA纯verilog实现AD9208协议实现AD9208数据收发的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

我这里已有的 GT 高速接口解决方案

我的主页有FPGA GT 高速接口专栏,该专栏有 GTP 、 GTX 、 GTH 、 GTY 等GT 资源的视频传输例程和PCIE传输例程,其中 GTP基于A7系列FPGA开发板搭建,GTX基于K7或者ZYNQ系列FPGA开发板搭建,GTH基于KU或者V7系列FPGA开发板搭建,GTY基于KU+系列FPGA开发板搭建;以下是专栏地址:

点击直接前往

我这里已有的 JESD204 高速AD接口解决方案

我的主页有FPGA JESD204 高速AD接口解决方案专栏,有JESD204B、JESD204C等接口解决方案,以下是专栏地址:

点击直接前往

3、工程详细设计方案

工程设计原理框图

工程设计原理框图如下:

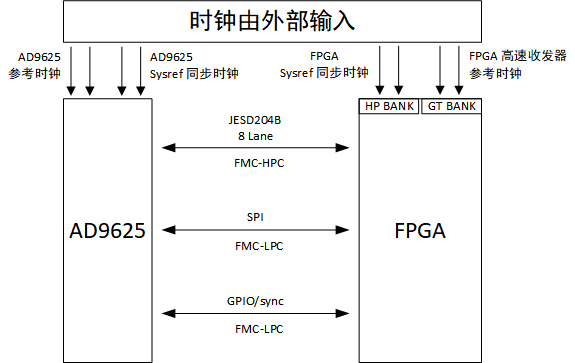

JESD204B 硬件设计架构

JESD204B硬件设计实现AD9208芯片与FPGA之间的物理通道交互,基于JESD204B协议,其中AD9208采用FMC转接板形式与FPGA开发板实现物理连接,MFC的HPC接口时钟完全右MFC转接板供给,本设计采用外部时钟输入方式,你也可以采用时钟晶振方式,比如TI公司的LMK04828,多路同源时钟实现JESD204B协议的可靠运行,JESD204B硬件设计架构如下:

信号输入设备

做测试时,可采用示波器产生正弦波作为信号输入,不再赘述;

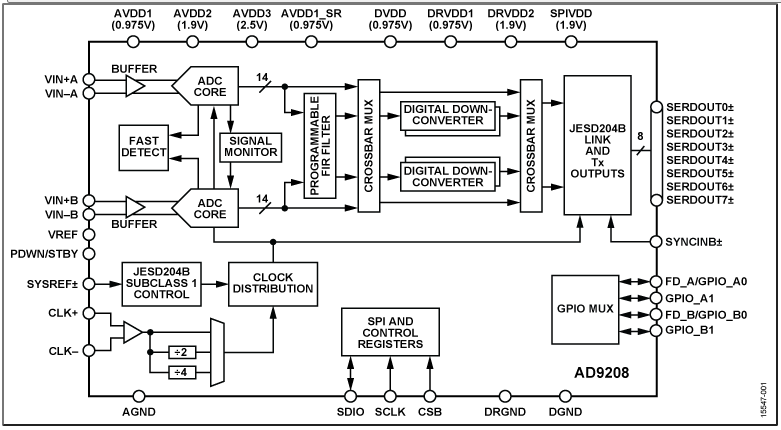

AD9208芯片解读

AD9208内部架构如下:

AD9208是一款双通道、14 位、3 GSPS 模数转换器 (ADC)。该器件具有片内缓冲器和采样保持电路,确保实现较低的功耗、较小的封装尺寸和出色的易用性。该产品经过专门设计,支持那些可对高达 5 GHz 带宽的模拟信号进行直接采样的通信应用场合。ADC 输入的 −3 dB 带宽为 9 GHz。AD9208 经过了全面优化,采用小巧紧凑的封装,可以提供宽泛的输入带宽、快速的采样速率、卓越的线性度以及较低的功耗。

AD9208双通道 ADC 内核采用具有集成式输出纠错逻辑的多级差分流水线架构。每个 ADC 都配备了宽泛的带宽输入,支持各种用户可选的输入范围。集成基准电压源简化了设计考虑事项。模拟输入和时钟信号是差分输入。ADC 数据输出通过交叉复用器从内部连接到四个数字下变频器 (DDC)。每个 DDC 包括多达五个级联信号处理级:48 位变频器(数控振荡器 (NCO)),以及多达四个半带抽取滤波器。NCO 允许在通用输入/输出 (GPIO) 引脚上选择预置频段(最多可以选择三个频段)。通过 SPI 可编程配置文件,可以在多个 DDC 模式之间选择 AD9208 的操作。

AD9208除了 DDC 模块外,AD9208 还配备了其他多种功能以简化通信接收器中的自动增益控制 (AGC) 功能。通过使用 ADC 的寄存器 0x0245 中的快速检测控制位,可编程阈值检测器可以监测传入信号的功率。如果输入信号电平超过可编程阈值,快速检测指示器会变高。由于此阈值指示器具有较低的延迟,用户可以迅速调低系统增益,从而避免 ADC 输入处出现超范围状态。除了快速检测输出功能外,AD9208 还具有信号监测能力。信号监测模块提供正由 ADC 数字化的信号的附加信息。

用户可以根据 DDC 配置和接收逻辑器件的可接受线速,在各种单线、双线、四线和八线配置中配置基于子类 1 JESD204B 的高速串行化输出。此外,还通过 SYSREF± 和 SYNCINB± 输入引脚支持多器件同步。

AD9208 还提供了灵活的功耗减低选项,可以在必要时大幅度降低功耗。所有这些功能均可通过一个 3 线串口接口 (SPI) 进行编程。

AD9208 提供不含铅的 196 球状引脚 BGA 封装,可以在 −40°C 至 +85°C 的环境温度范围内工作。此产品受美国专利保护。

请注意,在整个数据手册中,多功能引脚(例如 FD_A/GPIO_A0)可由整个引脚名称指定,也可以由引脚的单一功能指定,例如 FD_A(当仅与该功能相关时)。

AD9208特性如下:

JESD204B(子类 1)编码串行数字输出

支持每线高达 16 Gbps 的线速

3 GSPS 时每通道的总功率为 1.65 W(默认设置)

−2 dBFS 幅度、2.6 GHz 输入时的性能

SFDR = 70 dBFS

SNR = 57.2 dBFS

−9 dBFS 幅度、2.6 GHz 输入时的性能

SFDR = 78 dBFS

SNR = 59.5 dBFS

集成式输入缓冲器

噪声密度 = −152 dBFS/Hz

0.975 V、1.9 V 和 2.5 V 直流电源供电

9 GHz 模拟输入全功率带宽 (−3 dB)

用于高效 AGC 实施的幅度检测位

每个通道具有 2 个集成式宽带数字处理器

48 位 NCO

4 个级联半带滤波器

相位相干 NCO 切换

提供多达 4 个通道

串口控制

具有除以 2 和除以 4 选项的整数时钟

灵活的 JESD204B 线配置

片內抖动

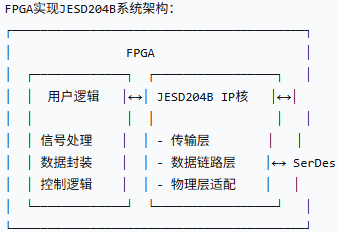

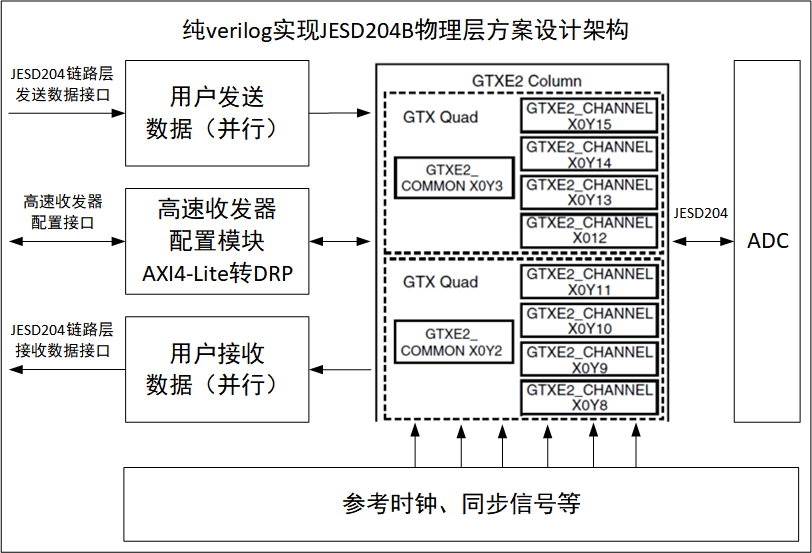

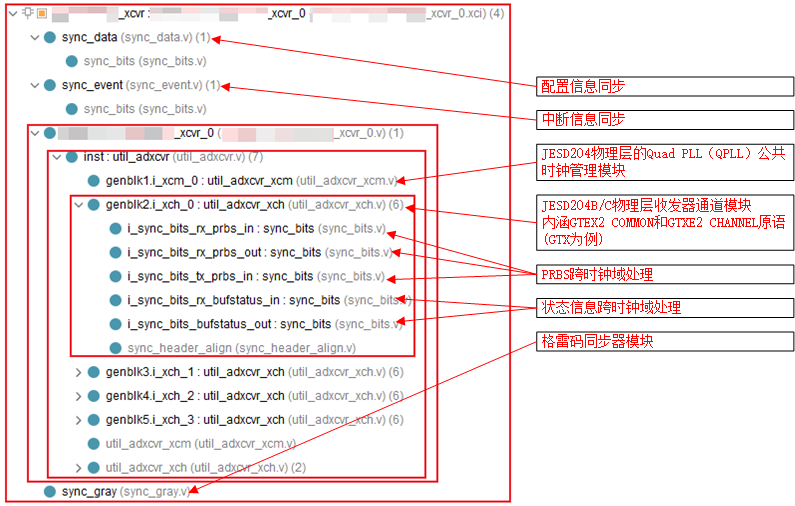

纯verilog实现的JESD204B 物理层方案

JESD204B物理层采用纯verilog代码实现,注意这里的纯verilog指的是非Xilinx原语部分,里面包含了GTEX2_COMMON和GTXE2_CHANNEL(GTX为例)原语,实现JESD204B物理层,即实现并行AD数据与高速低压差分串行数据接口的转换。

纯verilog实现的JESD204B物理层方案特性如下:

1、纯verilog代码实现,适用于Xilinx 7系列、Ultrascale和Ultrascale+系列FPGA;

2、支持Xilinx系列的GTXE2、GTHE3、GTHE4、GTYE4高速收发器原语;

3、最高可支持到单Lane 32.75Gbps线速率,根据选择的GT原语类型而定;

4、与Xilinx的JESD204 PHY IP核相比,简化了高速收发器配置流程,可任意修改底层代码,缺点是需要对高速收发器底层十分了解,否则很难精准配置;

5、预留了高速收发器的COMMON、CHANNEL和Eye-Scan的DRP配置接口,并转换为AXI4-Lite接口,可通过软件实现高速收发器线速率的动态配置;

6、支持8B10和64B66B编解码协议;

纯verilog实现JESD204B物理层方案设计架构如下:

纯verilog实现JESD204B物理层方案源码架构如下:

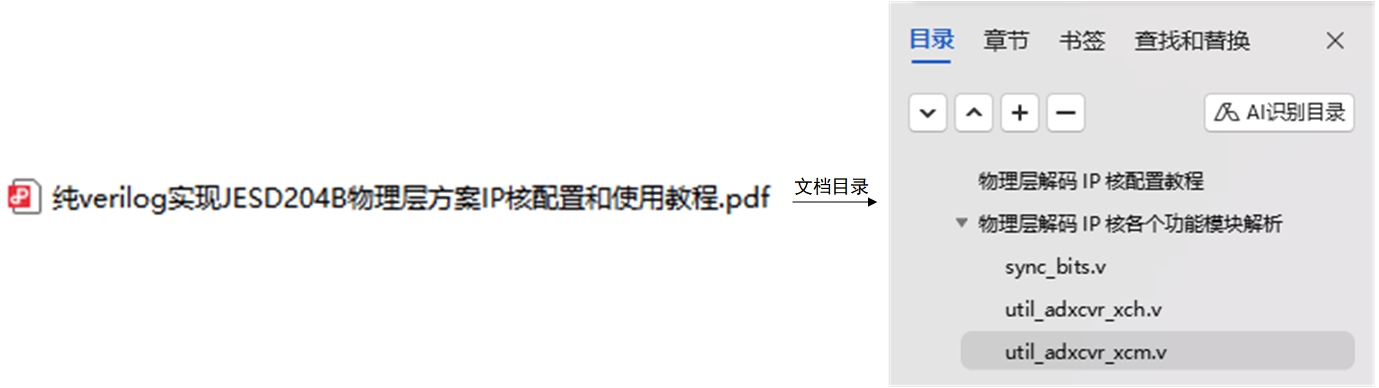

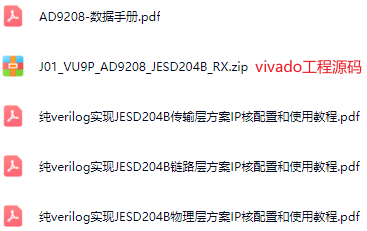

关于这个纯verilog实现JESD204B物理层方案IP的详细配置和使用,博主专门写了一个文档并放在了资料包中,如下:

纯verilog实现的JESD204B 数据链路层方案

JESD204B数据链路层采用纯verilog代码实现,实现JESD204B数据链路层解码功能。数据链路层由解码模块和控制模块两个部分构成;

纯verilog实现的JESD204B数据链路层方案特性如下:

1、纯verilog代码实现,适用于Xilinx 7系列、Ultrascale和Ultrascale+系列FPGA;

2、支持JESD204B和JESD204C;

3、支持JESD204子类0和1;

4、确定性延迟(用于子类1操作);

5、支持AXI4-Lite动态配置;

6、支持事件、中断;

7、8B/10B模式下的最大带宽:15 Gbps;

8、64B/66B模式下的最大带宽:32 Gbps;

9、低延迟;

10、每个独立的Lane可启用/禁用;

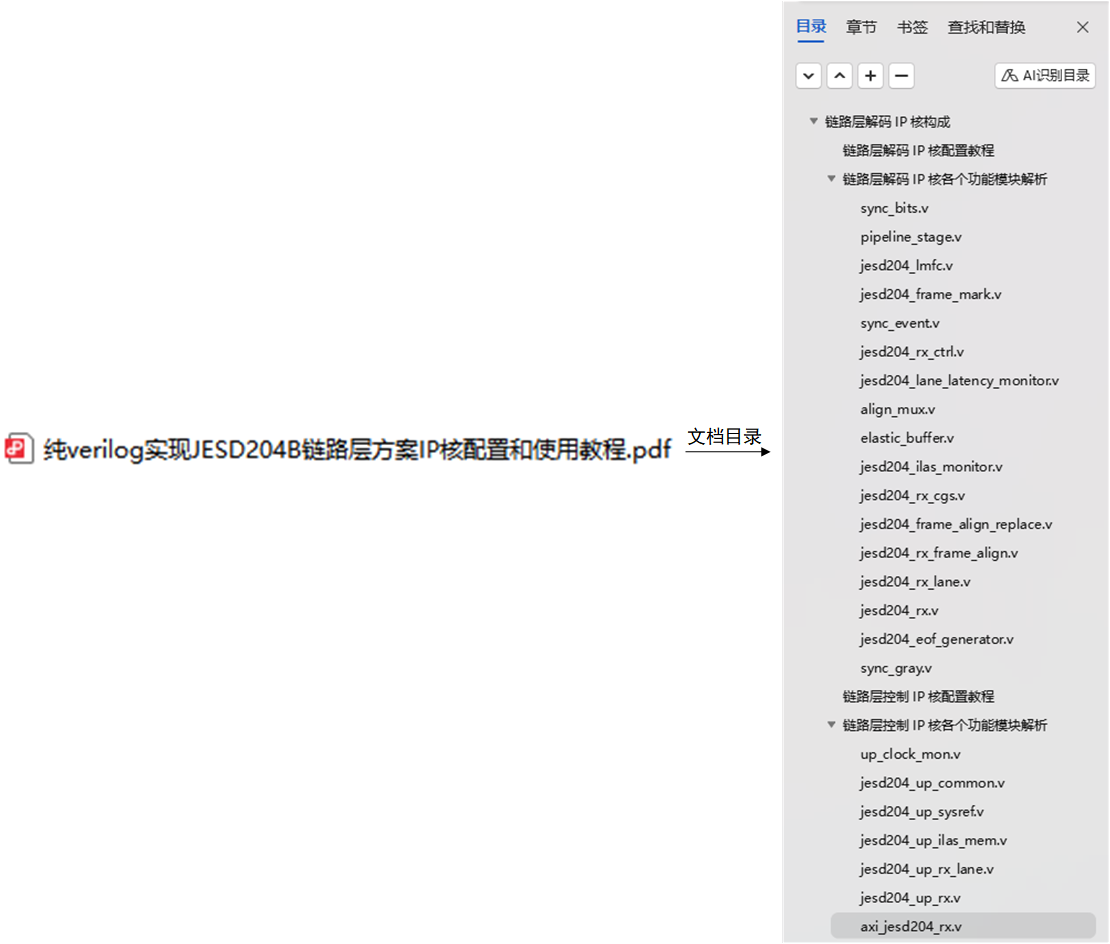

纯verilog实现JESD204B数据链路层方案设计架构如下:

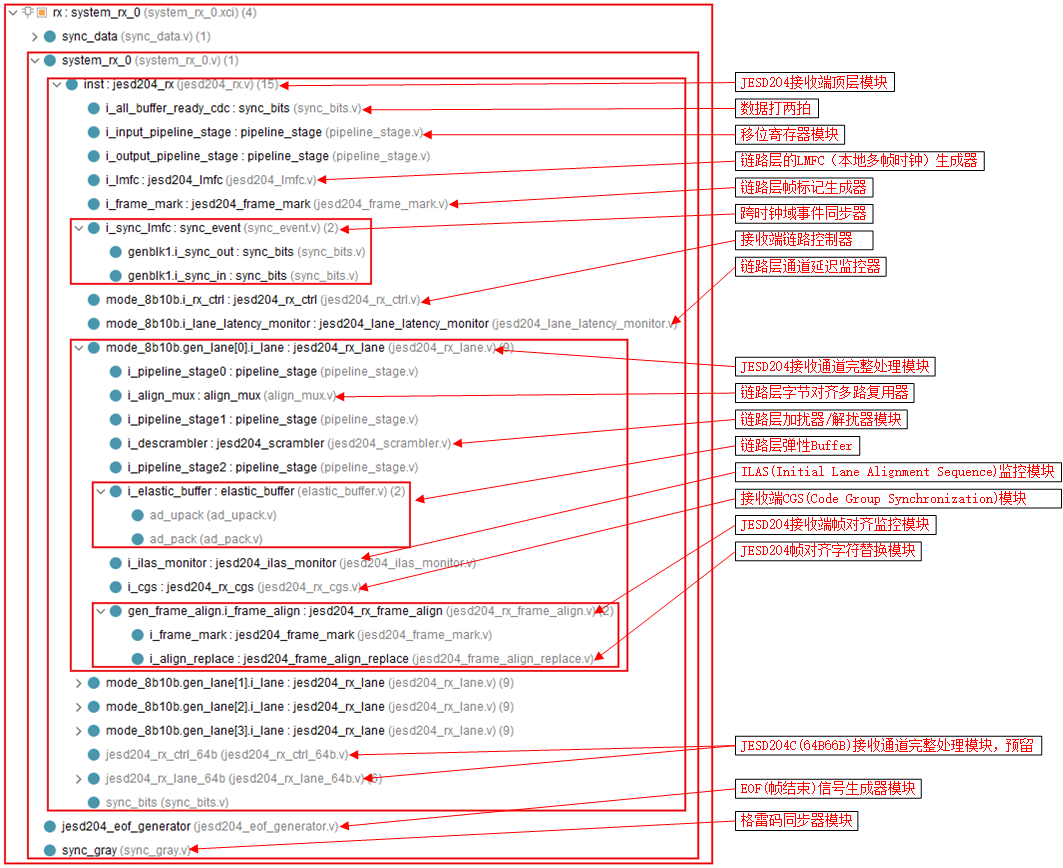

纯verilog实现JESD204B数据链路层解码模块方案代码架构如下:

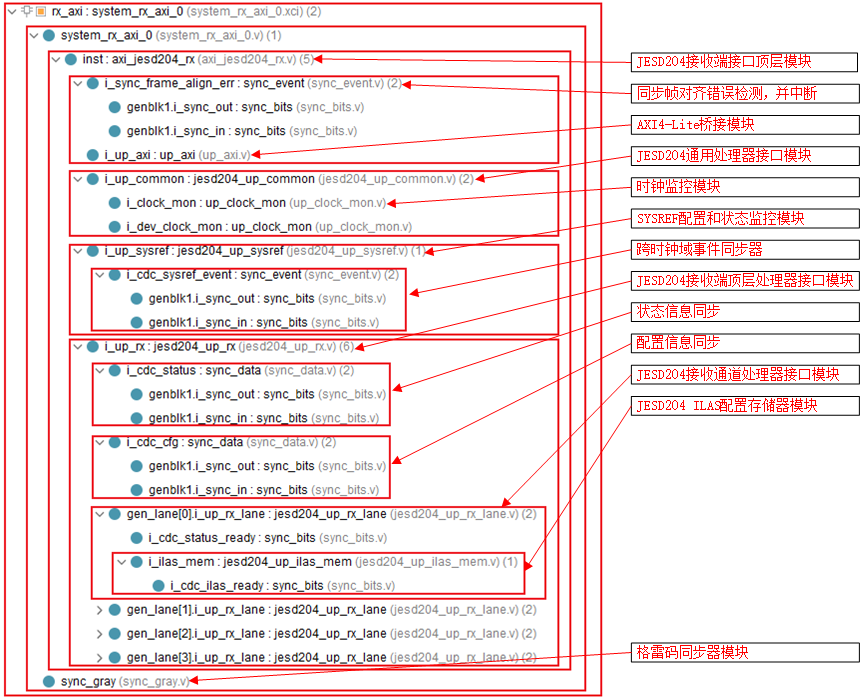

纯verilog实现JESD204B数据链路层控制模块方案代码架构如下:

关于这个纯verilog实现JESD204B链路方案IP的详细配置和使用,博主专门写了一个文档并放在了资料包中,如下:

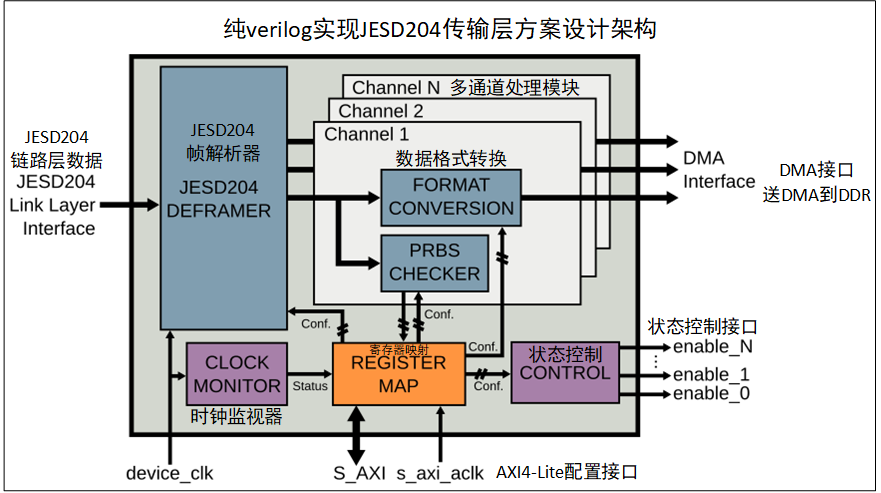

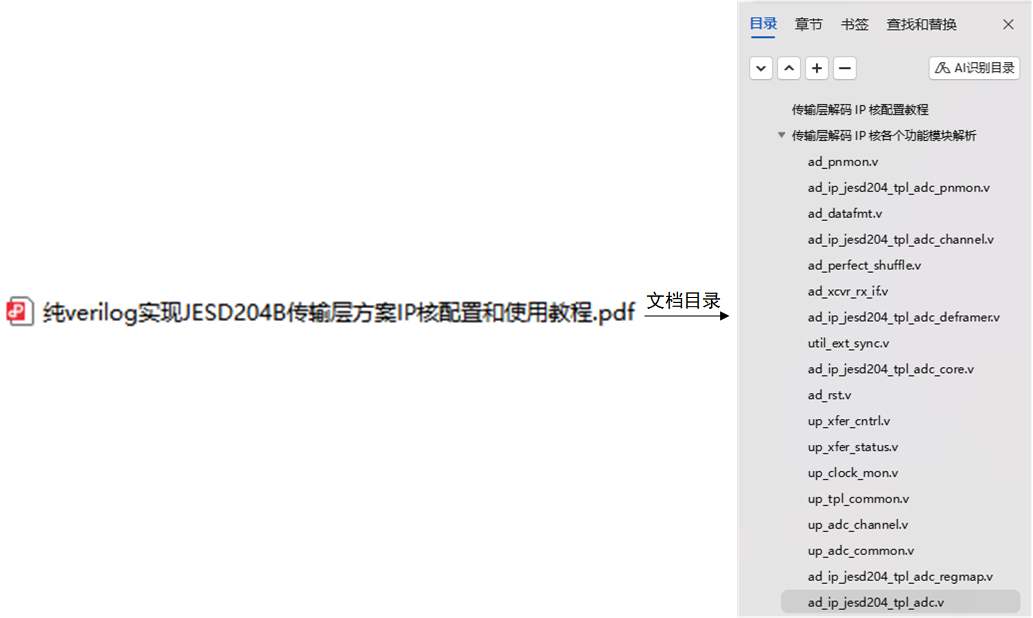

纯verilog实现的JESD204B 传输层方案

JESD204B传输层采用纯verilog代码实现,实现JESD204B接收数据帧解析和格式转换功能。

该JESD204B传输层方案特性如下:

1、纯verilog代码实现,适用于Xilinx 7系列、Ultrascale和Ultrascale+系列FPGA;

2、支持JESD204B和JESD204C;

3、支持AXI4-Lite动态配置;

纯verilog实现JESD204B传输层方案设计架构如下:

JESD204B数据传输层负责在AD9625 JESD204B接口中进行数据格式的映射和解映射,即根据ADC芯片数据手册调整

关于这个纯verilog实现JESD204B传输层方案IP的详细配置和使用,博主专门写了一个文档并放在了资料包中,如下:

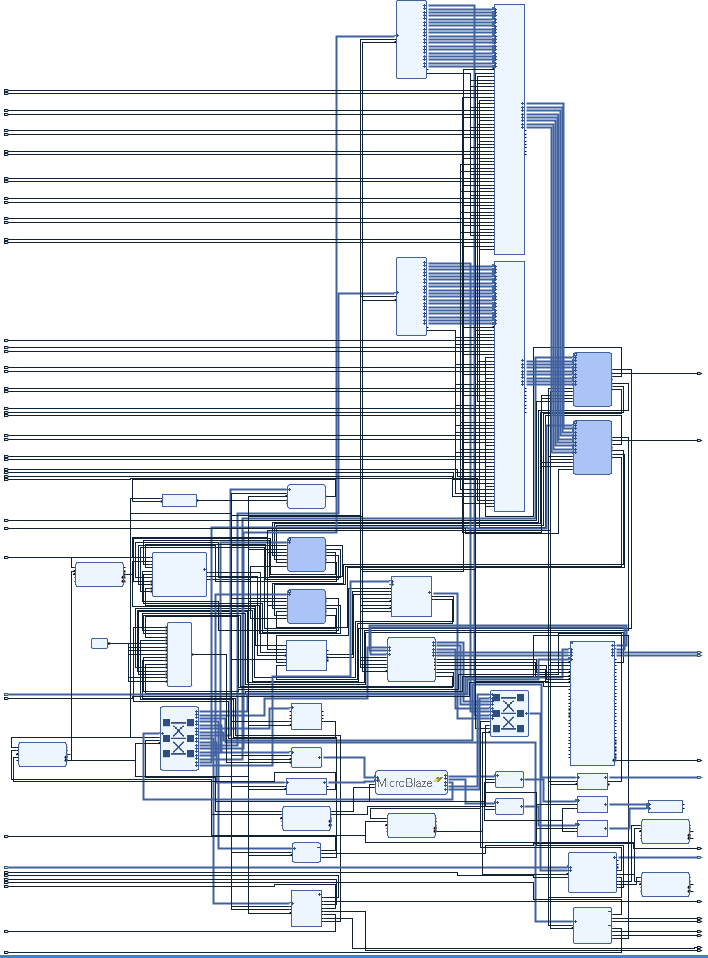

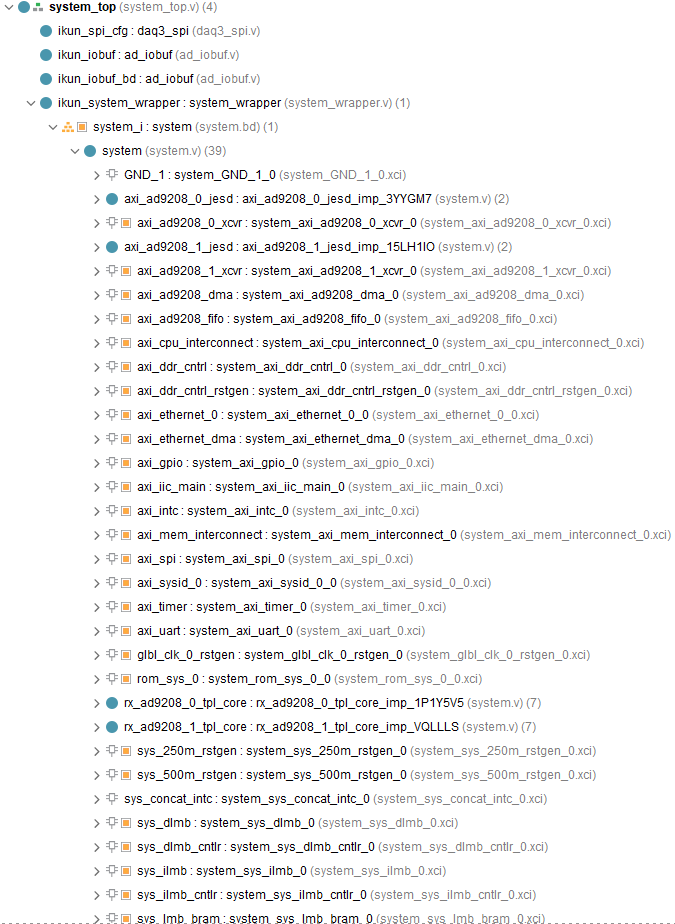

PL端逻辑工程源码架构

提供1套工程源码,以工程源码1为例,工程Block Design设计如下:

提供1套工程源码,以工程源码1为例,综合后的工程源码架构如下:

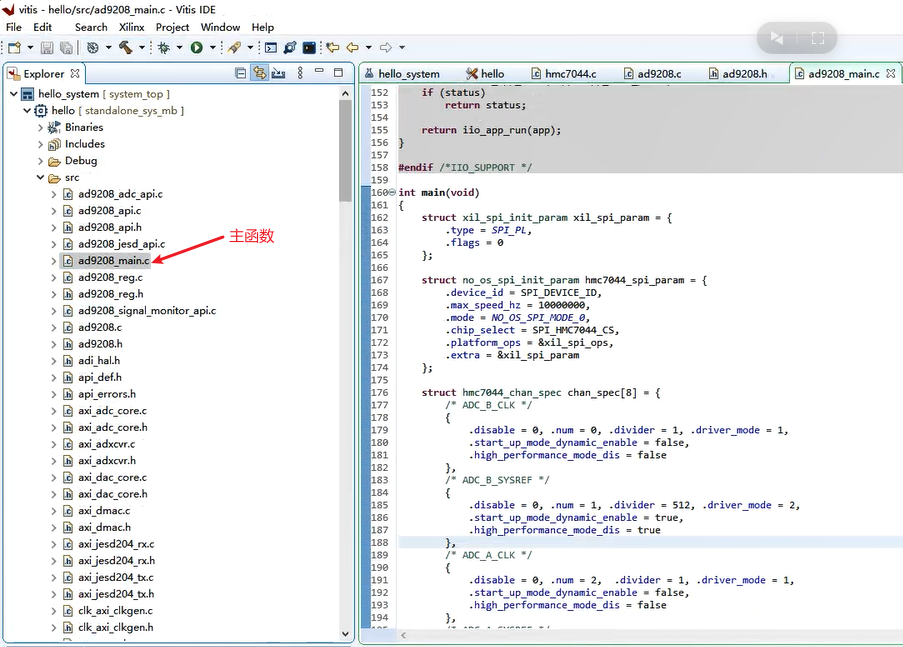

PS端软件工程源码架构

PS端软件代码架构

PS端软件工程源码架构如下:

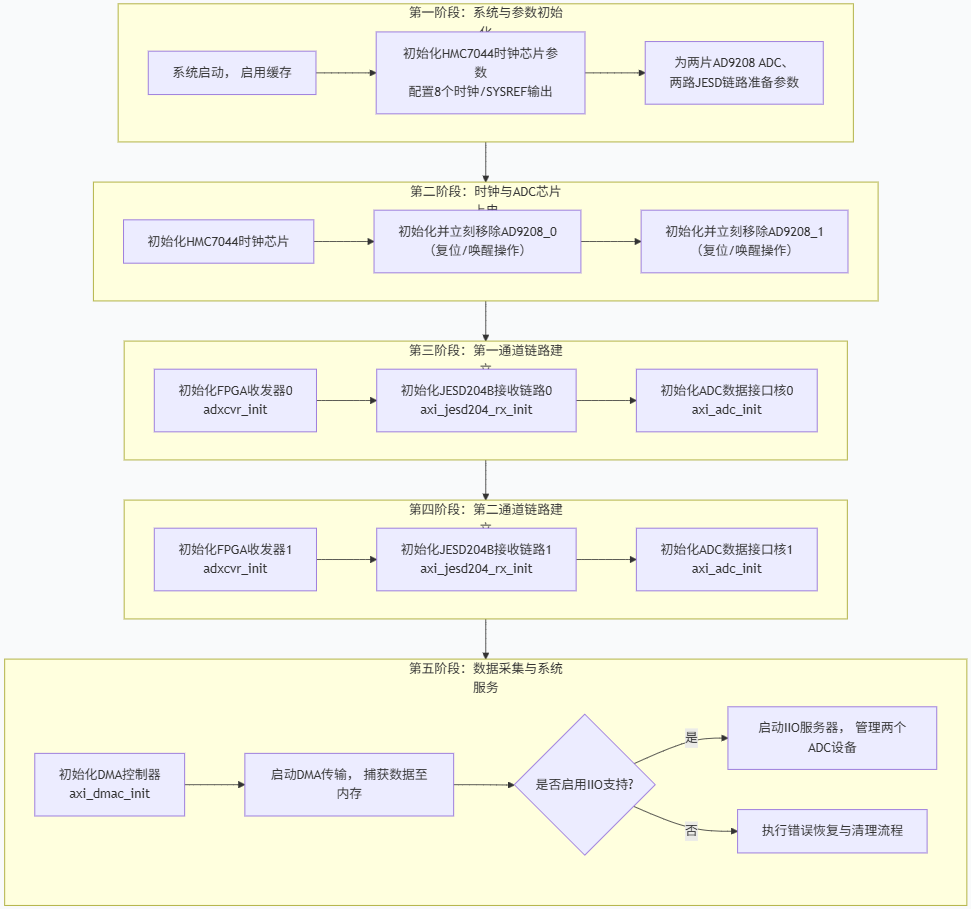

软件程序流程图

程序流程图如下:

PS端代码功能

简单来说,PS端代码构建的一个高带宽、双通道同步数据采集系统,其核心工作流程是:

1、搭建精密时钟树:用单颗HMC7044产生所有同步时钟,这是多通道、多芯片JESD204B系统的关键。

2、初始化双ADC:执行特定的上电序列来启动两片高速ADC。

3、建立双数据通道:并行配置两套独立的JESD204B接收链路。

4、统一数据采集:通过一个DMA控制器将双路数据流合并采集到内存。

5、提供服务:通过IIO框架同时暴露两个数据源,或进行清理后结束。

它的设计体现了多通道同步采集系统的典型架构:集中时钟、并行链路、统一采集。相较于之前的AD9656系统,它在时钟复杂度、通道数和数据带宽上都显著提升。

PS端代码主要功能模块详解

1、AD9208芯片驱动层 (ad9208.h/c)

作用:控制AD9208 ADC芯片。通过SPI和GPIO配置其复杂功能,是双通道3GSPS高性能ADC。

关键特性:

数字下变频:代码中为每个ADC配置了一个DDC通道,设置70 MHz的NCO和2倍抽取,可将特定频段搬移至基带。

测试模式:test_mode_ch1 分别设置为RAMP(斜坡)和ONE_ZERO_TOGGLE(0/1交替),用于验证链路。

初始化的特殊操作:代码中调用ad9208_initialize()后立即调用ad9208_remove(),这通常是为了执行一次软复位或确保芯片从特定状态唤醒,是此类高速ADC常见的启动序列。

2、时钟生成与分配模块 (HMC7044)

作用:作为整个系统的时钟心脏,为双ADC系统和FPGA收发器提供多路高精度、相位同步的时钟和SYSREF信号。

芯片:HMC7044,一款高性能的JESD204B时钟芯片,内置PLL和抖动消除器。

复杂配置:代码中配置了8个输出通道,分别为:

通道0 & 2:提供1分频(高频)时钟给两个ADC作为采样时钟。

通道1 & 3:提供512分频的SYSREF给两个ADC,用于JESD204B链路确定性延迟。

通道8 & 9:提供分频后的参考时钟给FPGA收发器。

通道10 & 11:提供SYSREF给FMC连接器(可能用于同步其他板卡)。

3、JESD204B高速串行链路与FPGA收发器模块

作用:建立并维护双通道ADC芯片与FPGA逻辑之间的高速串行数据通道。

双路设计:代码中为两个ADC独立配置了 rx_0_ 和 rx_1_ 两套完全相同的链路(收发器、JESD接收器),实现了并行数据采集。

关键参数:lane_rate_khz = 15,000,000(15 Gbps),ref_rate_khz = 750,000,device_clk_khz = 375,000,这些参数根据JESD标准公式与ADC采样率(3 GSPS)和配置(M=2, L=8, NP=16等)严格计算得出。

4、FPGA数据路径与DMA控制器模块

作用:在FPGA侧并行接收两路JESD数据,并高效地将合并后的数据搬运至内存。

双ADC接口核:axi_adc_core 有两个实例(rx_0_adc, rx_1_adc),分别对应两个物理ADC芯片的数据流。

DMA控制器:只有一个 rx_dmac 实例。它在初始化时计算总数据尺寸((rx_1_adc->num_channels + rx_0_adc->num_channels) * sizeof(uint16_t)),表明它将两路ADC的数据在内存中连续存放。axi_dmac_transfer_start 启动从FPGA到DDR的批量传输。

5、工业I/O框架 (IIO Framework) - 可选项

作用:当定义 IIO_SUPPORT 宏时,启动IIO守护进程,同时管理两个ADC设备。

双设备管理:start_iiod 函数初始化两个 iio_axi_adc_desc,并将它们注册为独立的IIO设备("axi_adc0" 和 "axi_adc1")。它还将DDR内存缓冲区平均分割,分别分配给两个设备用于数据读写,实现了资源的独立管理。

6、严谨的错误处理机制

代码后半部分(error_1 到 error_11)展示了典型的"瀑布式"错误恢复。如果后续阶段初始化失败,会通过 goto 语句跳转,按与初始化相反的顺序依次关闭和释放之前已成功初始化的所有硬件资源,确保系统在任何失败点都能安全退出,不会遗留硬件处于未定义状态。

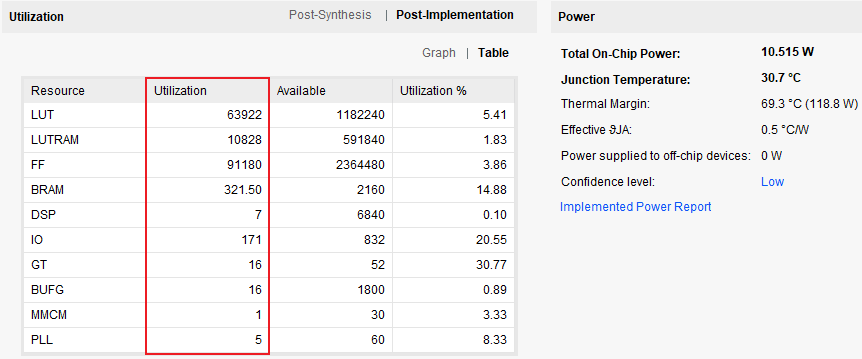

4、vivado工程源码1详解-->VU9P版本

开发板FPGA型号:Xilinx--Virtex UltraScale±-xcvu9p-flga2104-2L-e;

FPGA开发环境:Vivado2022.2;

AD输入:AD9208;

DA输出:串口打印或串口输出到上位机;

数据交互接口:JESD204B;

JESD204B物理层方案:纯verilog实现的JESD204B物理层;

JESD204B链路层方案:纯verilog实现的JESD204B链路层;

JESD204B传输层方案:纯verilog实现的JESD204B传输层;

JESD204B使用高速收发器类型:GTH;

工程作用:让读者掌握FPGA基于JESD204B实现AD9208数据收发的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

5、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件-->另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

6、上板调试验证

准备工作

需要准备的器材如下:

AD9208子卡;

FPGA开发板;

AD9208数据收发效果演示

将AD9208子卡连接FPGA开发板的FMC-HP接口,如下:

然后打开vitis,下载程序,具体演示这里不方便展示,敬请见谅;

7、工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务: