集成电路基础知识经典问答(面向 FPGA 工程师版)

------ 收藏这些就够了!

以下内容基于常见集成电路知识进行了精选整理,同时结合 FPGA 工程师在实际项目中常遇到的模拟接口、电源、信号完整性等场景,风格保持原稿的"问答式、短句、够用、能落地"的路线。

1. 为什么 FPGA 工程师也要懂点模拟基础?

因为 FPGA 在真实硬件中永远不是"独立存在"的,它需要和电源、ADC/DAC、时钟、传感器、通信收发器打交道,而这些全部依赖模拟电路。

FPGA 的高速 IO、参考电压、供电完整性、时钟质量等,都与模拟电路直接相关。

不会模拟基础,就做不好"板级系统工程"。

2. FPGA 供电为什么要多路 LDO/DC-DC?

FPGA 需要 多电压域 :核心电压、IO 电压、PLL 电压、SerDes 电压等各不相同。

而模拟 PLL、电源噪声敏感域必须用噪声更低的 LDO,核心电压又更适合 DC-DC。

所以你经常会看到:

-

DC-DC 给核心供电

-

LDO 给 PLL 或参考电压供电

这是实际工程的最佳折中方案。

3. 常见 ADC 输入有什么区别?FPGA 该怎么接?

ADC 有两种典型输入结构:

-

单端输入:适合低速、低精度

-

差分输入 :适合高速、抑制共模噪声

FPGA 采集 ADC 数据时要重点注意:

-

差分时应使用 LVDS 或 Sub-LVDS 采样

-

数据时钟(DCLK)最好采用 source-synchronous

-

模拟前端要注意阻抗匹配和驱动能力

这是 FPGA 与 ADC 的关键接口要求。

4. 为什么很多模拟器件前后都要加 TVS/ESD?

FPGA 的 IO 对静电是 极度敏感 的。

前端传感器、天线、按键、USB、射频接口,都可能把瞬态电压传递到 FPGA。

ESD/TVS 的目的就是:

-

限制浪涌

-

保护前级放大器

-

避免 FPGA IO 损坏

5. 为什么时钟线一定要走差分?

因为差分具备:

-

更小的 EMI

-

更强的抗干扰

-

更稳定的抖动

FPGA 内的 PLL 对输入时钟质量极敏感,因此推荐用:

-

LVDS

-

LVPECL

-

HCSL

这些协议本质都属于高质量差分时钟标准。

6. 模拟电路里的"地"为什么要分?数字地、模拟地不能乱合?

FPGA 系统里常见:

-

AGND:模拟地(ADC 前端、PLL)

-

DGND:数字地(FPGA 核心、逻辑)

分地的工程原因:

-

模拟信号只有毫伏级

-

数字地的噪声是模拟回路的"天敌"

但要注意:

不是完全隔离,而是单点等电位汇合。

7. FPGA 工程中,为什么高速 ADC 时常用差分放大器?

差分放大器能做到:

-

信号幅度转换(比如传感器输出不足)

-

共模电压调节(使信号适应 ADC 量程)

-

低失真、高带宽

这是高速采集系统的标配结构(数据手册常称为 "Driver")。

8. 如何判断电源对 FPGA 是否"干净"?

看四个指标:

-

纹波(Ripple)

-

瞬态响应(Load Transient)

-

噪声频谱(PSRR)

-

供电边界条件是否满足器件 datasheet

FPGA 核心电压一般容差更严格,比如 ±3% 或更小。

电源抖一下,FPGA 逻辑瞬间出问题,属于工程常见坑。

9. 什么时候需要运放?什么时候需要比较器?

-

运放:信号调理、放大、滤波

-

比较器 :做"0/1"判断、过流保护、阈值触发

很多初学者把二者混用是常见错误。

FPGA 中的高速比较、过欠压检测,大都需要独立比较器。

10. 为什么高频信号一定要控制走线阻抗?

因为 FPGA 的高速 IO(如 LVDS、GTX、GTP、SerDes)依赖精确的:

-

特性阻抗

-

延时差

-

反射控制

如果 100MHz+ 信号没有阻抗控制,你会看到:

-

时序抖动

-

眼图闭合

-

数据错码

这不是"玄学",而是电磁特性的必然结果。

11. 模拟电路中,为什么要加 RC 滤波?FPGA 也需要?

模拟前端常用:

-

低通(去噪)

-

高通(隔直、去漂移)

而 FPGA 的 复位、电源、配置脚 也非常依赖 RC:

-

去抖动

-

延时

-

保证时序

FPGA 的配置脚"上电太快"导致无法配置,是常见新手问题。

12. FPGA 工程中常见的模拟测量方式有哪些?

-

霍尔电流检测(带放大)

-

分压采样电压

-

电流采样电阻 + 运放

-

ADC 采样温度、压力等传感器

-

反向电动势(在电机控制中常见)

这些都必须经过模拟电路调理后,才能安全进入 FPGA。

13. 模拟电路中为什么强调"带宽 × 压摆率"?

运放必须跟得上你的信号速度。

比如 ADC 采集 1MHz 正弦波,你至少要准备:

-

运放带宽:10MHz 以上

-

SR:保证上升沿不过度畸变

输出跟不上,会直接导致 FPGA 采集到失真信号。

14. 常见模拟器件的作用总结(FPGA 工程必背)

| 器件 | 用途 |

|---|---|

| 运算放大器 | 信号放大/调理 |

| 比较器 | 阈值判断/保护 |

| LDO | 低噪声供电 |

| DC-DC | 高效率供电 |

| TVS | ESD/浪涌保护 |

| 差分放大器 | 驱动高速 ADC |

| 参考电压源 | ADC 稳定性关键 |

这些在 FPGA 外围电路中出现频率极高。

15. FPGA 新手最容易踩的模拟坑有哪些?

-

ADC 输入量程不对

-

时钟驱动方式错误

-

模拟地和数字地乱接

-

电源纹波大导致随机死机

-

未给 PLL 用低噪声供电

-

高速信号走线未控阻抗

-

TVS 没加导致 IO 烧毁

这些都是工程中的 真实案例。

总结

以上是 对 FPGA 工程最有价值的模拟知识点:

-

电源完整性

-

信号完整性

-

ADC/传感器接口

-

时钟质量

-

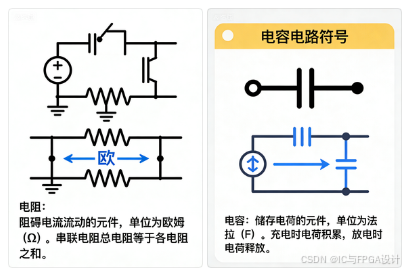

基础模拟元件原理

掌握这些,你的 FPGA 工程质量会稳得多,不是浮于表面的"数字逻辑工程师",而是能真正把板子做通、系统跑稳的工程师。