目录

CAN

1.物理层

[1.1 CAN总线结构](#1.1 CAN总线结构)

[1.2 电平定义](#1.2 电平定义)

2.协议层

[2.1 位时序与波特率](#2.1 位时序与波特率)

[2.2 同步机制](#2.2 同步机制)

[2.3 报文类型](#2.3 报文类型)

[-------------------------------------------------------------------------------------

I2S](#------------------------------------------------------------------------------------- I2S)

1.物理特性

2.电气特性

3.常见的I2S数据格式

Philips标准

左对齐(MSB)标准

右对齐(LSB)标准

-------------------------------------------------------------------------------------

RS232

1.接口定义:

2.关于RTS与CTS

3.数据帧格式

CAN

1.物理层

1.1 CAN总线结构

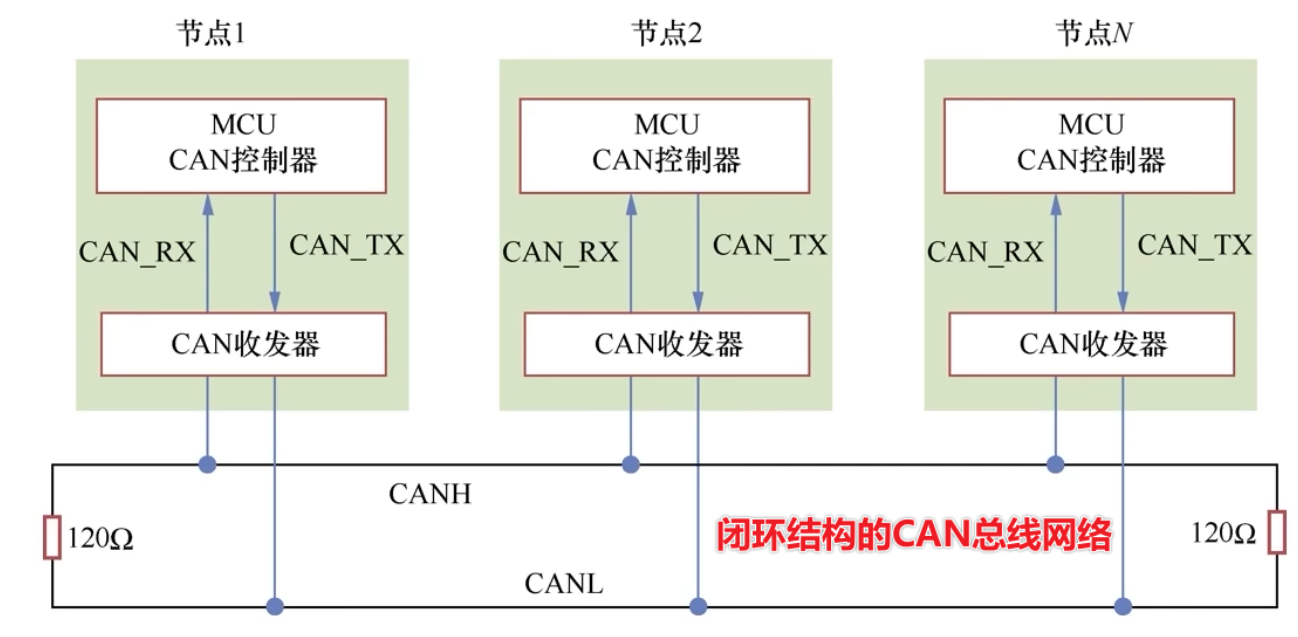

- 闭环结构

CAN总线闭环结构由 ISO 11898标准定义,适用于高速、短距离,速率在125kb/s ~ 1Mb/s,总线长度可以40m

两端各接一个120R电阻,用于阻抗匹配

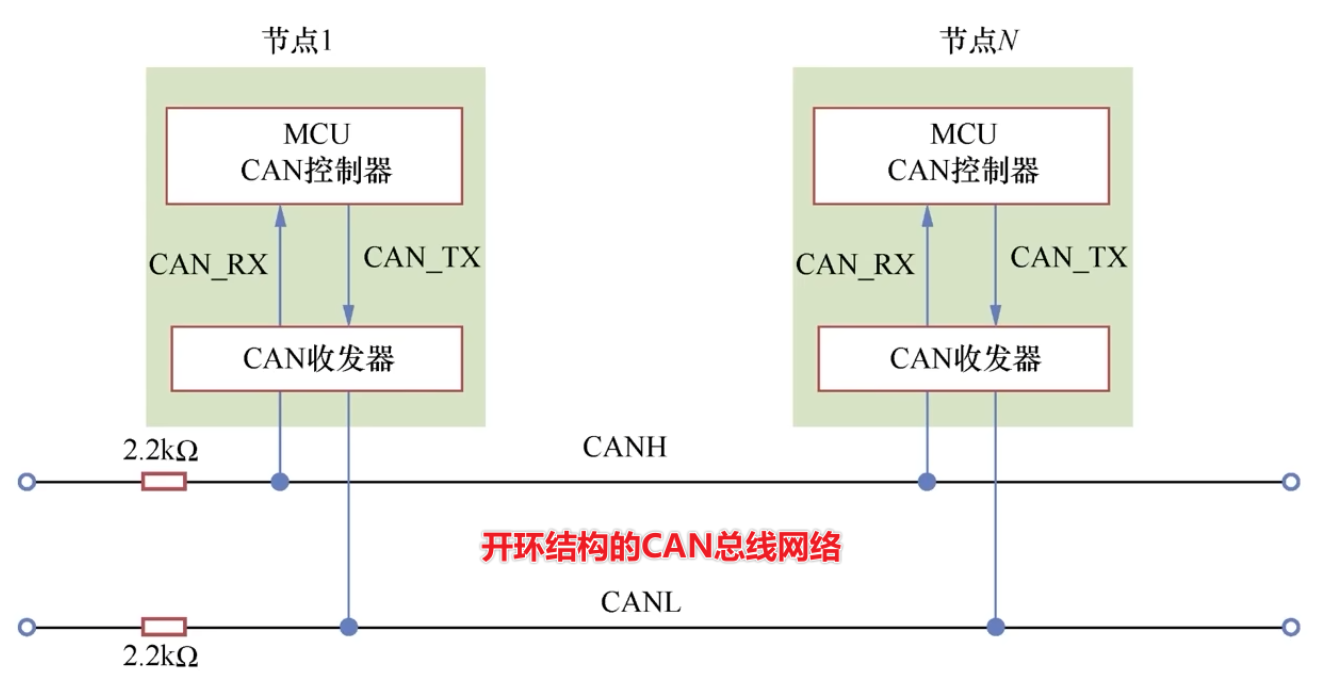

- 开环结构

CAN总线开环结构由 ISO 11519-2标准定义,用于低速、远距离

1.2 电平定义

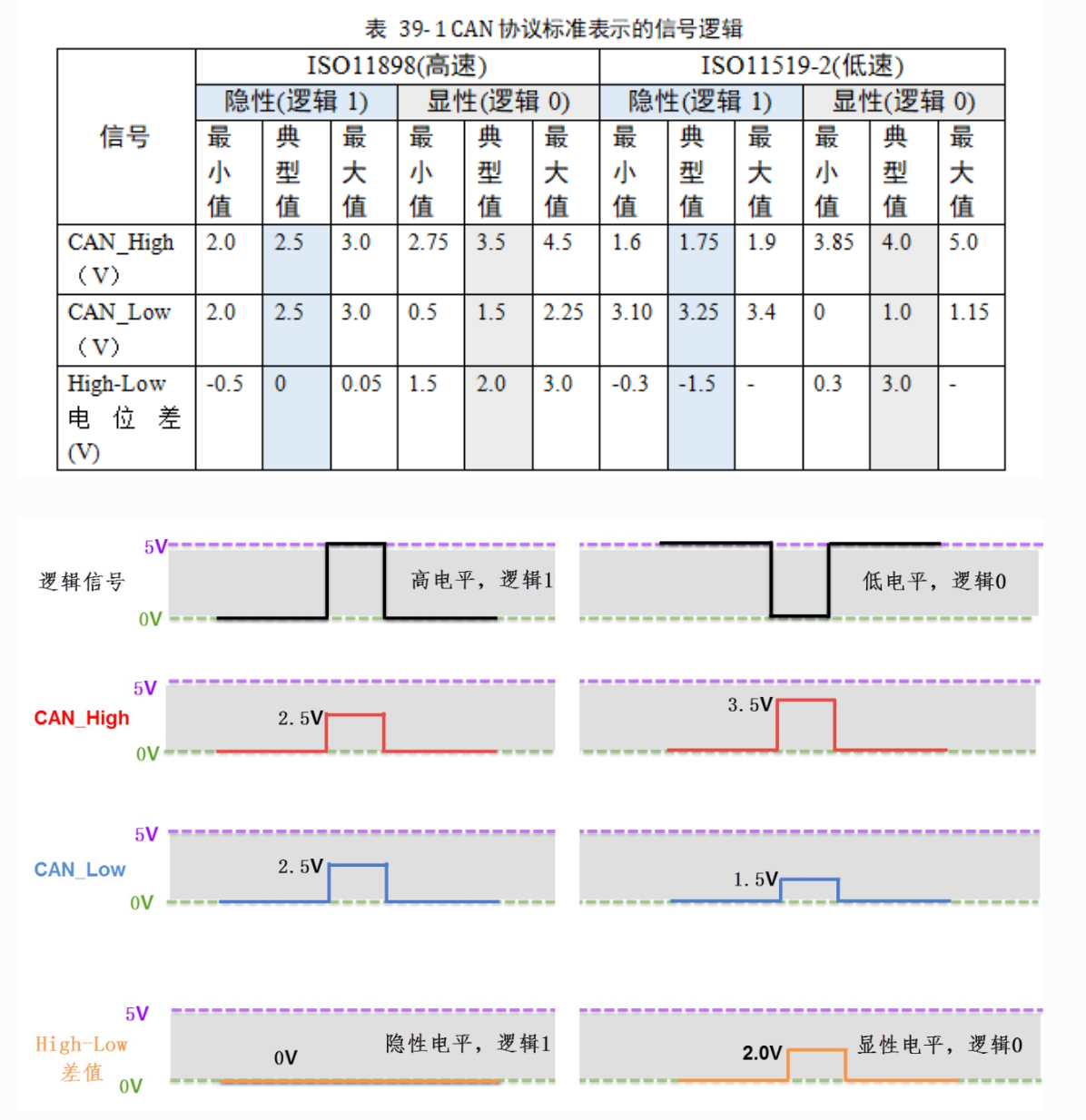

对应逻辑 1 的,称为隐性电平。对应逻辑 0 的,称为显性电平;

闭环结构:隐性电平压差0V附近,显性电平压差2V附近;

开环结构:隐性电平压差小于0V,显性电平压差大于2V;

2.协议层

2.1 位时序与波特率

- 波特率确定

首先要明白,CAN波特率与挂载时钟速率不同。比如某个CAN总线挂载在42Mhz的时钟上面,

时钟6分频之后,fcan=7Mhz

那么

然后我们想要配置波特率为500kbps,那么位时间

为

假设同步段占 1tq,位段1占 4tq,位段2为 2tq

那么

,得出 tq=285.71ns

根据285.71ns再来进行时钟的分频;

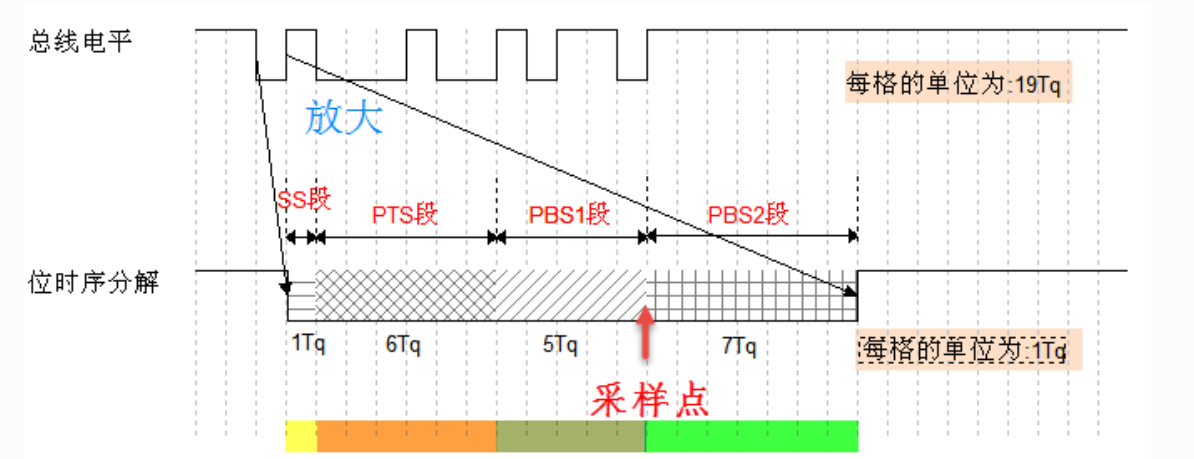

- 位时序分解

上面我们展示了 SS(同步段) PBS1(位段1) PBS2(位段2)

其实在 SS 后面往往伴随着 PTS(传播时间段)

SS(同步段):通讯节点用于检测是否同步,假如信号跳变在SS内,那么认为是同步的;

PTS(传播时间段):用于补偿传播的物理时间;

PBS1(相位缓冲段):主要用来补偿边沿阶段的误差;

PBS2(相位缓冲段):用来补偿边沿阶段误差的;

2.2 同步机制

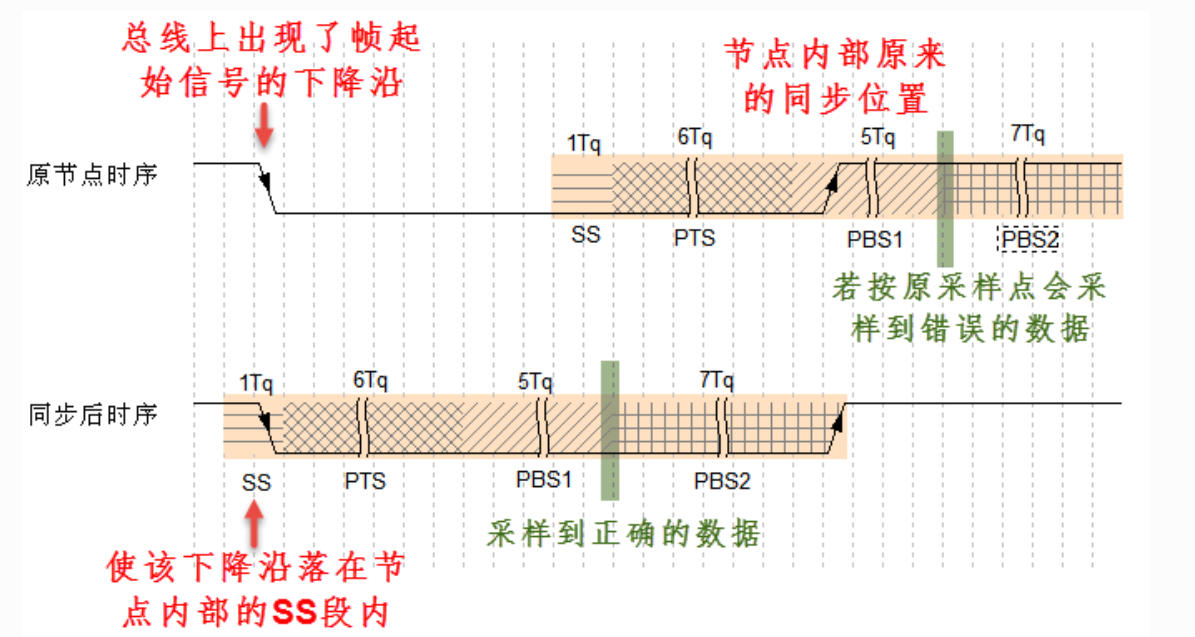

- 硬同步

总线上出现起始信号(下降沿),各个节点都会监测,

若是这个下降沿落在该节点SS段内,则表示同步,否则不同步;

硬同步的方式是更改SS段,使其包含下降沿,达到同步

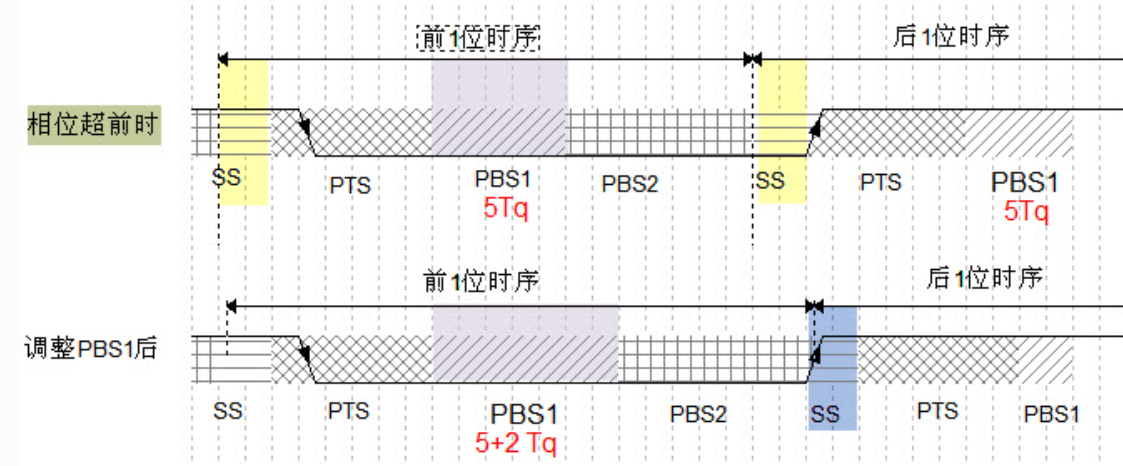

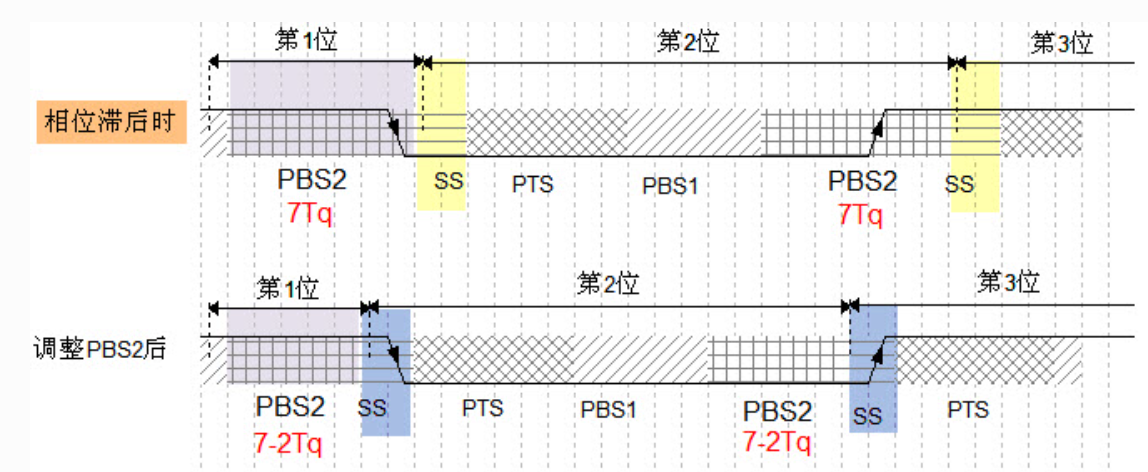

- 重新同步

分成相位超前、相位滞后

比如相位超前2tq,那么下一个位时序,会把PBS1段 +2tq,使得SS可以同步;

若是相位滞后2tq,那么下一个位时序,会把PBS2段 -2tq,使得SS可以同步;

PS:此外,称这段同步时间段为"重新同步补偿宽度SJW",CAN控制器会限定SJW的最大值;

比如 SJW=3Tq时,认为增加或者减少不能超过3Tq的时间长度;

SJW越大,吸收误差越大,但是通信速率下降;

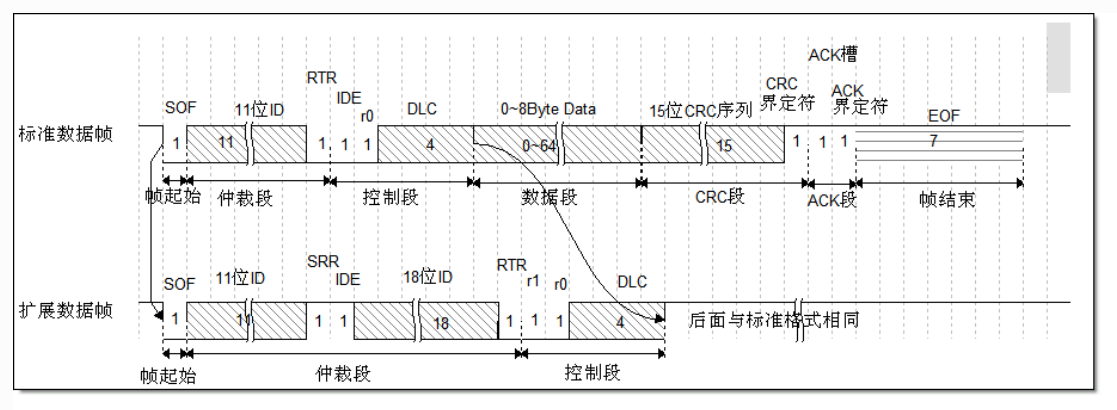

2.3 报文类型

- 报文种类

数据帧 用于节点向外传送数据 遥控帧 用于向远端节点请求数据 错误帧 用于向远端节点通知校验错误,并且请求重新发上一个数据 过载帧 通知远端节点:本节点尚未做好接受准备 帧间隔 用于把数据帧/遥控帧与前面的帧分开

- 帧的结构

帧起始 | 仲裁段 | 控制段 | 数据段 | CRC | ACK

数据帧以一个显性位(逻辑0)开始,以七个连续隐形位(逻辑1)结束;

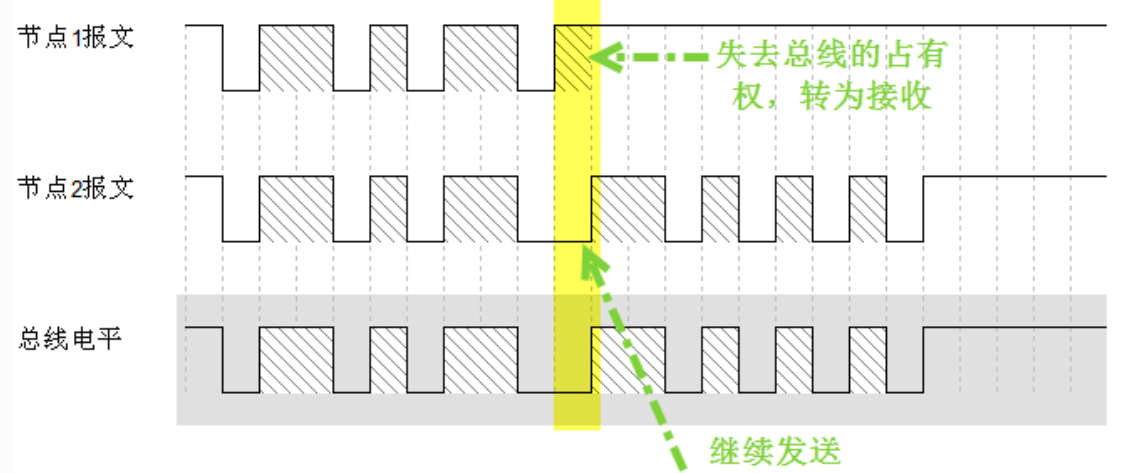

帧起始 一个显性电平 通知各个节点有数据、其它节点通过起始信号电平跳变沿来同步 仲裁段(标准格式) 主要包含ID信息(11位) 两个报文同时被发送时,根据仲裁段内容,判断哪个优先 ID:包含ID信息,用于报文优先级判定 RTR:区分数据帧/遥控帧,显性数据,隐性遥控 仲裁段(拓展格式) 主要包含ID信息(29位) IDE:区分标准/拓展,显性标准,隐性拓展 SRR:只存在拓展格式中,用于代替标准格式中的RTR,在拓展帧中,SRR为隐性,RTR为显性 RTR:... 控制段 4个数据位组成 用于表示报文有多少字节,0~8 r1和r0为保留位,设置为显性 数据段 0~8个字节 MSB先行 CRC段 15位 在15位CRC之后,有个界定符,用于与ACK间隔开,界定符为隐性 ACK段 2位 一位ACK、一位界定符 发送节点隐性位,接收节点发送显性表示应答 帧结束 7 个连续隐性位(逻辑1)

- 标准帧与扩展帧区别:

在ID信息上面,

优先级:总线上同时出现显性电平和隐性电平,那么总线状态会被置为显性电平,优先级标准格式>拓展格式;

I2S

1.物理特性

I2S一般用于音频传输;

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2S由一根系统时钟线和三根信号线组成: 1.MCLK 主时钟:频率为128 / 256 / 512 * 采样频率; 2.SCLK(BCLK):串行时钟SCLK(位时钟BCLK),因为每一位音频数据都对应一个脉冲,所以SCLK频率 == 声道数*采样率*采样位数; 3.LRCK(WS):帧时钟,用于切换左右声道数据,0表示左声道,1表示右声道,LRCK频率 == 采样频率; 4.SDATA(SD):二进制补码表示的音频数据; |

| 通信时序:LRCK时钟控制数据发送到左右声道,SCLK输出时钟方波,数据在SCLK下降沿时触发; |

2.电气特性

|-------------------------------------------------------------|

| > 输出电压 :VL<0.4V , VH>2.4V; > 输入电压 :VIL==0.8V , VIH==2.0V; |

3.常见的I2S数据格式

I2S有左对齐(MSB)与右对齐(LSB);

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ###### Philips标准其中: LRCLK需要在第一位(MSB)之前一个时钟就开始跳变,才有效; 并且LRCLK在BCLK下降沿的时候发送变化; 发送端在BCLK下降沿发送数据,接收端在BCLK上升沿接收数据; 这种模式下,数据高位总是在LRCLK变化后的第二个BCLK处,所以接收端和发送端的有效位数可以不同。也就是接收端能处理的有效位数少于发送端发过来的数据,就可以把多余的低位数据给放弃掉,并且假如发送端发送的数据比较少,接收端这边也会自动补足剩余位; 此模式特点: 不会造成数据错位; |

左对齐(MSB)标准

|---------------------------------------------------------------------------------------------------------------------------------|

|这种模式在LRCLK反转时开始传输数据, 但是此模式下LRCLK为1时传输左声道数据,0传输右声道数据; |

右对齐(LSB)标准

|-------------------------------------------------------------------------------------------------------------------------------------------|

|此模式下,是发送数据,在数据发送完之后LRCLK实现翻转; 且此模式与MSB一样,LRCLK为1时传输左声道,0传输右声道; |

RS232

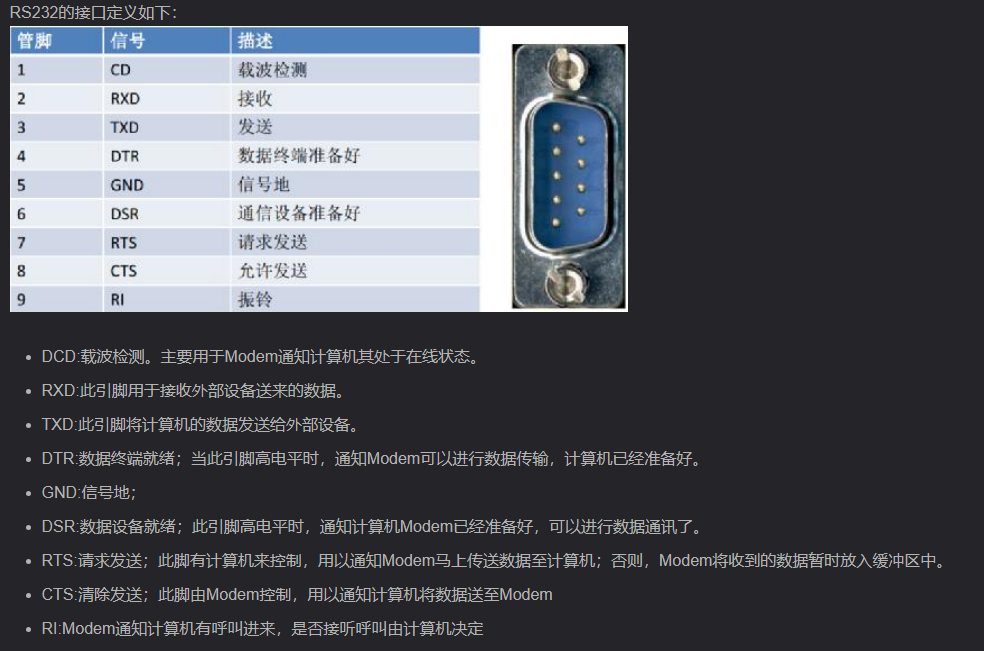

1.接口定义:

通常情况下只需要TX、RX和GND

在RS232中,逻辑1一般是 -3V~-15V , 逻辑0一般为 3V~15V

也就是和印象中的01倒过来的

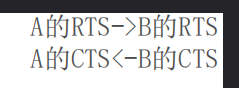

2.关于RTS与CTS

A的RTS有效,说明A请求发送数据给B了。当A检测到A的CTS有效,也就说明B做好了接受数据的准备

此时:

A的RTS对接B的RTS,当A要给B发送数据

B做好准备,将B的CTS对接A的CTS

A的CTS有效,表明B做好接受的准备

A开始发送数据

(每个字节在发送前都会确保A的CTS有效)

当A的数据发完了,就会将A的RTS无效化,此时B接受到的是A不准备发送信息,也将自己的CTS置为无效

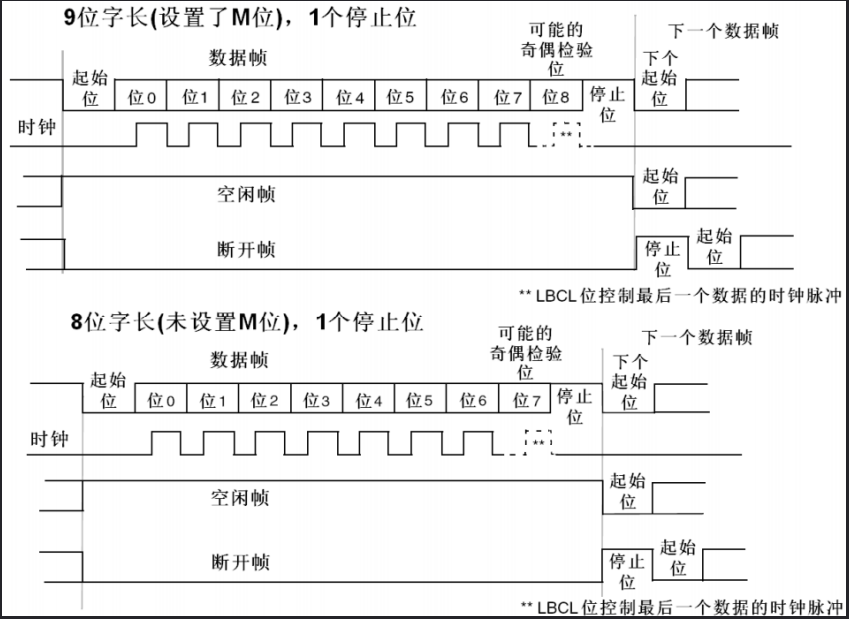

3.数据帧格式

有些时候需要在发送方的TX上面,上拉一个电阻,以增强驱动性。