在高速缓存内存(HBM)领域持续领跑的三星与SK海力士,正以混合键合技术为突破口,开启3D DRAM技术的新纪元。这一战略转型不仅预示着存储技术的深度革新,更体现了两大半导体巨头在提高集成度、优化性能与成本上的不懈追求。

混合键合:3D DRAM的革命性飞跃

当前,DRAM模块的连接主要依赖于微凸点技术,而混合键合技术的引入,则通过硅通孔(TSV)实现芯片的垂直堆叠,从根本上消除了对微凸点的依赖,显著降低了芯片厚度。这一技术革命不仅简化了制造流程,更在物理层面为提升存储密度与性能提供了可能。

传统DRAM的局限与3D DRAM的对策

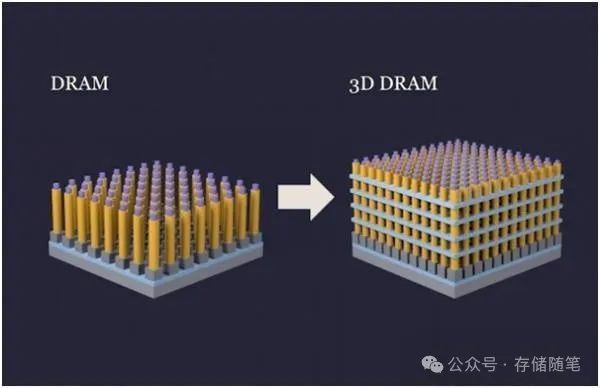

《韩国经济日报》早前报道指出,传统DRAM在单一基板上集成高达620亿个存储单元,密集排列的晶体管在二维平面上引发了电流泄漏与干扰等问题。而3D DRAM通过将晶体管分层堆叠,有效增加了晶体管间的间隔,显著降低了泄漏与串扰风险,为解决这些问题提供了创新途径。

3D堆叠:空间利用与性能的双重提升

3D DRAM通过垂直堆叠存储单元,实现了单位面积存储容量的三倍增长,与传统横向布局相比,这种设计极大提升了集成效率。与主要通过垂直连接多片DRAM芯片以提升带宽的HBM技术相比,3D DRAM的堆叠策略在提升存储容量的同时,也开辟了新的性能提升路径。

三星与SK海力士的前瞻布局

在2024年国际内存研讨会上,SK海力士明确表示将在3D DRAM生产中引入混合键合技术,展现出对技术创新的坚定承诺。另一边,三星则预计在2025年推出其3D DRAM产品,同时,三星还在积极探索4F² DRAM技术,并计划将其与混合键合技术相结合。据《The Elec》透露,一旦4F²结构的DRAM在10纳米或更精细工艺节点上实现商用,三星有望将芯片表面积缩减30%,相比当前商用的6F2 DRAM,这将带来显著的成本与空间节省。

结语:3D DRAM市场的份额争夺战悄然启幕

三星与SK海力士对混合键合技术的采用,不仅预示着3D DRAM时代的到来,也拉开了市场竞争的新篇章。随着技术的不断成熟与应用的逐步推广,3D DRAM有望成为推动存储行业发展的新引擎,同时也将为数据中心、高性能计算乃至移动设备等领域带来前所未有的性能与效率提升。这场静悄悄的3D DRAM市场份额争夺战,正见证着存储技术的一次重大转型,也为未来智能化世界的构建铺设了坚实的基石。

随着CPU core的不断增加,单core享用的内存带宽却在不断的下降,这对计算绝对是巨大的拖后腿。

DRAM 的核心工作原理基于电荷存储,通常采用一晶体管一电容(1T1C)结构。随着制程节点不断缩小,要在更小的空间内实现稳定的电荷存储和读写操作变得日益困难。

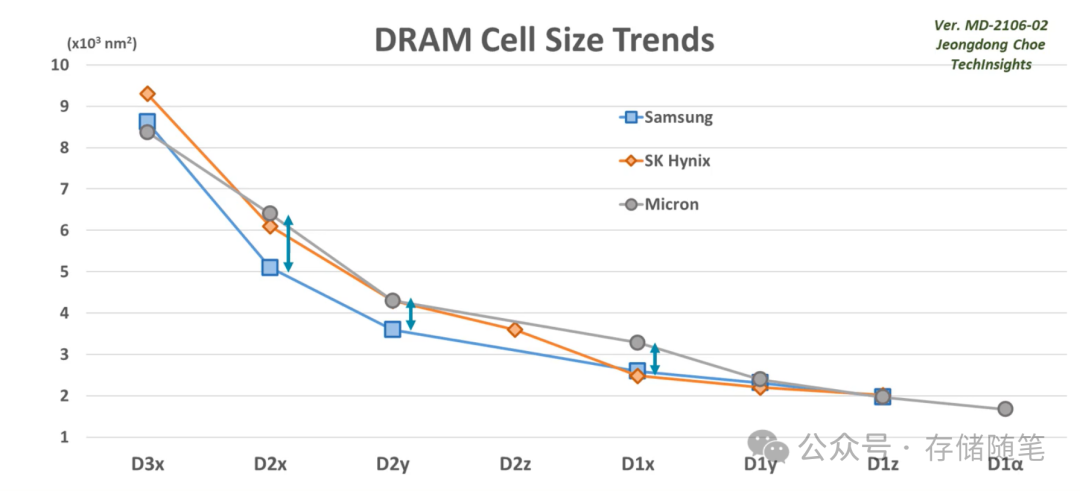

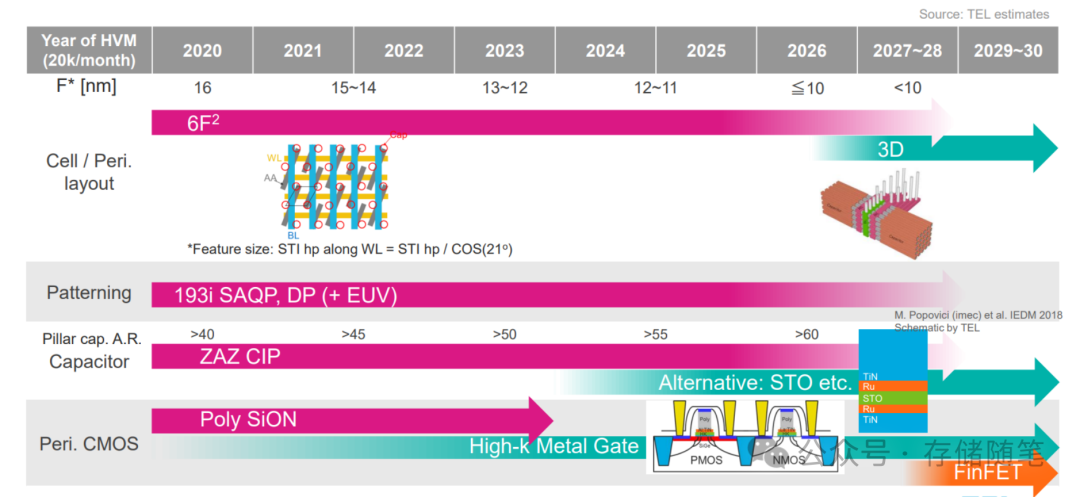

物理极限(如量子隧穿效应、漏电流增加、热稳定性下降等)、材料科学挑战(如电介质厚度减少导致的电容减小、泄漏电流增大等)以及制造工艺的精密控制要求,都使得 DRAM 在继续沿用 2D 方式缩小器件尺寸(如提到的 4F² 缩放)时遭遇严重阻碍。

随着 2D DRAM 缩放难度增大,研发投入、制造成本以及良率控制问题日益突出。在技术节点不断微缩的过程中,单位面积内增加更多比特所需的投资呈非线性增长,而性能提升和成本节省却可能不如预期。这种成本效益的失衡使得继续沿用传统路径进行 DRAM 缩放不再经济可行,成为产业难以回避的财务难题。

随着数据量爆炸性增长,尤其是云计算、人工智能、大数据分析等领域对高速、大容量、低延迟内存的需求持续攀升,市场对更高密度、更低功耗、更大带宽的 DRAM 产品有着强烈需求。然而,现有 2D DRAM 技术的发展速度已无法满足这些需求的增长速度,形成了供需之间的矛盾,进一步加剧了 DRAM 不再有效缩放问题的紧迫性。

为了解决这个难题,业内常见的有High Bandwidth Memory (HBM)、Computational In-Memory (CIM)、Emerging Memories(新型存储器)、CXL等技术,它们旨在通过不同的方式(如堆叠封装、计算与存储一体化、采用新材料新机制等)来绕过传统 2D DRAM 的缩放限制,提升存储密度和性能。

扩展阅读:

特别是对 3D DRAM 的探索,通过将存储单元垂直堆叠而非水平排列,可以在不大幅改变单个单元尺寸的情况下显著增加单位体积内的存储比特数,从而在一定程度上克服 2D 缩放的局限。尽管 3D DRAM 技术尚处于早期研发阶段,且面临诸多技术挑战(如专利布局、工艺复杂性、架构选择等),但因其巨大的潜力,已成为业界关注的焦点。

目前3D DRAM 的公开技术文献数量极少。行业主要厂商在公开交流上保持沉默,但在背后却在积极申请大量与 3D DRAM 相关的专利。这种现象表明,尽管企业不愿意公开分享技术细节,但他们对 3D DRAM 技术的开发投入巨大,并且通过专利保护的方式为未来的市场竞争和技术主导权做准备。这种策略反映出 3D DRAM 技术的战略重要性和潜在的巨大商业价值。

可以公开查询的关于3D DRAM的论文,比如来自 国内长鑫存储CXMT(2023 IMW Conf.)和三星(2023 VLSI Symp.),都是DRAM厂商在专业会议上发布的针对 1T1C(一晶体管一电容)结构的 3D DRAM

-

2023 IMW Conf. "A 3D Stackable 1T1C DRAM: Architecture, Process..." by CXMT

-

2023 VLSI Symp. " Ongoing Evolution of DRAM Scaling via 3rd Dimension: V-DAM" by Samsung

**除了主流的 1T1C 3D DRAM 研究,还有其他创新的无电容 DRAM 方法在探索中。**其中,2T0C Gain Cell 主要集中在学术研究层面,而 Gate-controlled-thyristor DRAM 则由 Macronix 开发。这两种无电容方案旨在通过简化结构、减少或取消电容元件来降低制造复杂度,提高集成度,可能是 3D DRAM 发展的另一种可能路径。

从 2D DRAM 向 3D DRAM 转变过程中将面临无数技术挑战。这些挑战涵盖工艺技术的各个方面,如硬掩模刻蚀(HAR etch)、横向刻蚀、原子层沉积(ALD)、原子层刻蚀(ALE)、外延生长、沉积技术、掺杂、硅化物形成、接触形成以及应力管理等。这些复杂且精密的工艺步骤需要相应的设备支持和技术创新,为半导体设备供应商提供了技术服务和设备升级的市场空间。

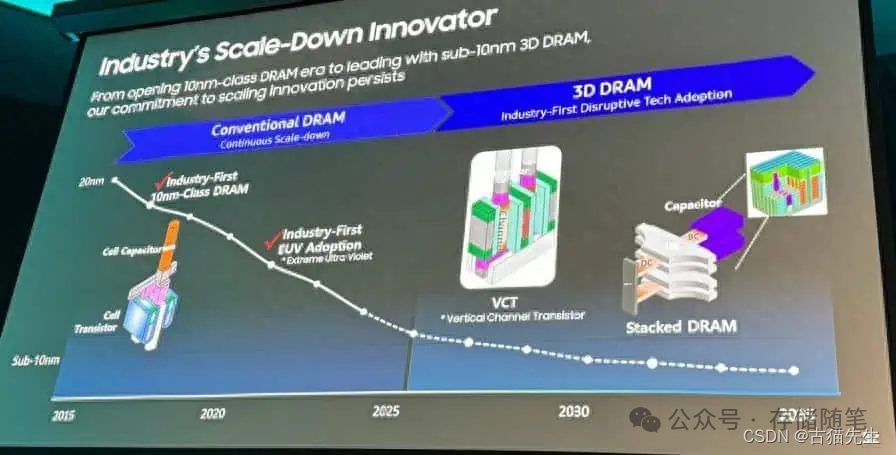

近日,在行业大会Memcon 2024上,三星宣布其计划成为首家在2025年后步入3D DRAM内存时代的行业领军者。随着DRAM内存行业在本十年后期将线宽压缩至低于10纳米,现有的设计解决方案在如此精细的尺度上难以进一步扩展,因此业界正在探索包括3D DRAM在内的多种创新内存设计。

在Memcon 2024大会上,三星展示了两项新型3D DRAM内存技术,即垂直通道晶体管(Vertical Channel Transistor)和堆叠DRAM(Stacked DRAM)。

-

相较于传统晶体管结构,垂直通道晶体管将沟道方向由水平改为垂直,这虽能显著减小器件面积占用,但对刻蚀工艺的精度要求更高。

-

相较于现有的2D DRAM结构,堆叠DRAM能充分利用Z轴空间,在较小区域内容纳更多存储单元,使得单颗芯片容量提升至超过100G级别。

-

三星已于今年早些时候在美国硅谷开设了一家新的3D DRAM研发实验室。

预计到2028年,3D DRAM市场规模将达到1000亿美元(约为7240亿人民币)。