一,灰度图像概念

灰度数字图像是每个像素只有一个采样颜色的图像。这类图像通常显示为从最暗黑色到最亮的白色的灰度,尽管理论上这个采样可以任何颜色的不同深浅,甚至可以是不同亮度上的不同颜色。灰度图像与黑白图像不同,在计算机图像领域中黑白图像只有黑白两种颜色,灰度图像在黑色与白色之间还有许多级的颜色深度。

一幅完整的图像,是由红色、绿色、蓝色 三个通道组成的。红色、绿色、蓝色三个通道的缩览图都是以灰度显示的。用不同的灰度色阶来表示" 红,绿,蓝"在图像中的比重。通道中的纯白,代表了该色光在此处为最高亮度,亮度级别是255。

Gray 图像:灰度(gray)图像就是我们常说的黑白图像,由黑到白为灰阶,其值域为 0- 255(8bit)。

二,彩色图像灰度化处理方法

1,分量法

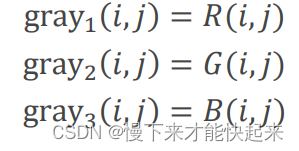

将彩色图像中的三分量的亮度作为三个灰度图像的灰度值,可根据应用需要选取一种 灰度图像。具体表达式如下。

其中,gray1 (𝑖,𝑗), gray2 (𝑖,𝑗), gray3 (𝑖,𝑗)为转换后的灰度图像在(i,j)处的灰度值, R(i,j),G(i,j),B(i,j)分别为转换前的彩色图像在(i,j)处 R、G、B 三个分量的值。

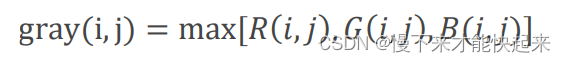

2,最大值法

将彩色图像中的三分量亮度 R,G,B 的最大值作为灰度图的灰度值。具体表达式如下。

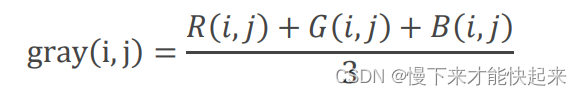

3,平均值法

将彩色图像中的三分量亮度求平均得到一个灰度值。如下:

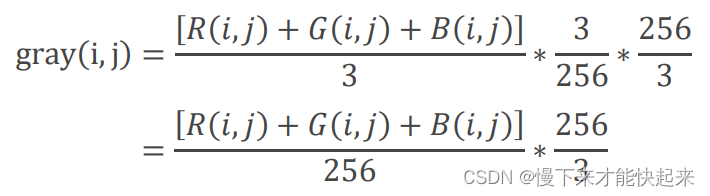

上式中有除法,考虑到在 FPGA 中实现除法比较的消耗资源,我们可以将其转换一下,

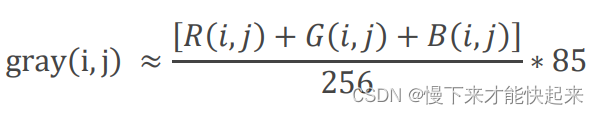

对 256/3 做近似取整处理,将 256/3 替换成 85,则公式变为如下:

然后利用移位的方法去实现除法(右移8位):

而乘法也可以用移位实现,85 = 2^6 + 2^4 + 2^2 + 2^0;

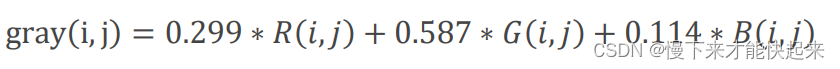

4,加权平均法

将三个分量以不同的权值进行加权平均:

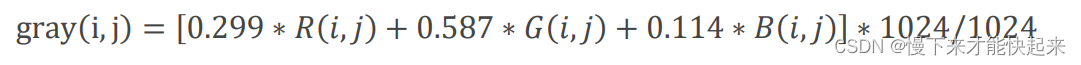

实际应用时,为了能避免浮点运算以及除法运算,可以先将式子缩放 1024 倍来实现运算算法,如下:

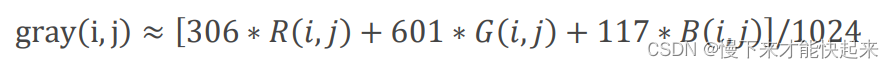

通过近似取整处理后得到近似公式:

也可以压缩到 8 位以内,式子变为如下。具体压缩到多少位可以根据实际需求。

其中乘法和除法都可使用移位实现。

三,代码实现

分量法和最大值法较为简单,这里实现平均值法和加权平均。

1,平均值法

代码如下:

module Avg_Gray(

input clk ,

input reset ,

input rgb_vaild ,

input [7:0] red_in ,

input [7:0] green_in ,

input [7:0] blue_in ,

output [7:0] gray_o ,

output reg gray_vaild

);

//求平均法GRAY = (R+B+G)/3=((R+B+G)*85)>>8

wire [9 :0] sum_rgb ;

reg [15:0] gray_r ;

assign sum_rgb = red_in + green_in + blue_in;

always @(posedge clk )

if (reset) begin

gray_r <= 0;

end

else if (rgb_vaild) begin

gray_r <= (sum_rgb << 6) + (sum_rgb << 4) + (sum_rgb << 2) + sum_rgb;

end

assign gray_o = gray_r[15:8];

always @(posedge clk) begin

gray_vaild <= rgb_vaild;

end

endmodule2,加权平均值

代码如下:

module Weight_avg_Gray(

input clk ,

input reset ,

input rgb_vaild ,

input [7:0] red_in ,

input [7:0] green_in ,

input [7:0] blue_in ,

output [7:0] gray_o ,

output reg gray_vaild

);

//灰度转换公式Gray = R*0.299+G*0.587+B*0.114=(R*77 + G*150 + B*29) >>8

wire [15:0] red_77 ;

wire [15:0] green_150 ;

wire [15:0] blue_29 ;

reg [15:0] sum_rgb ;

assign red_77 = (red_in<<6) + (red_in<<3) + (red_in<<2) + red_in;

assign green_150 = (green_in<<7) + (green_in<<4) + (green_in<<2) + (green_in<<1);

assign blue_29 = (blue_in<<4) + (blue_in<<3) + (blue_in<<2) + (blue_in<<1);

always @(posedge clk )

if (reset) begin

sum_rgb <= 0;

end

else if (rgb_vaild) begin

sum_rgb <= red_77 + green_150 + blue_29;

end

assign gray_o = sum_rgb[15:8];

always @(posedge clk) begin

gray_vaild <= rgb_vaild;

end

endmodule四,总结

在FPGA中,如果涉及到浮点数运算,除法运算,乘法运算,我们都可以将其进行变换,使用移位的方法实现。关于具体FPGA - 数 - 加减乘除可以看我的这篇文章:FPGA - 数 - 加减乘除-博客