Chapter 8 Feedback

这一章我们介绍feedback 反馈运放的原理. 负反馈是模拟电路强有力的工具.

8.1 General Considerations

反馈系统如下图所示

Aol=amp open-loop gain即开环增益. Aol=xo/xi

β \beta β 是 feedback factor, 注意方向.

β = x f x o \beta=\frac{x_{f}}{x_{o}} β=xoxf

Closed-loop gain, Acl

A C L = x o x s = A O L 1 + A O L β A_{CL}=\frac{x_{o}}{x_{s}}=\frac{A_{OL}}{1+A_{OL}\beta} ACL=xsxo=1+AOLβAOL

Loop gain = T= A O L β A_{OL}\beta AOLβ , 用来判断环路稳定性

8.1.1 Properties of Feedback Circuits

负反馈有几大好处: 降低gain的工艺偏差, 减少非线性失真, 增加op-amp的bandwidth, 控制输入和输出阻抗.

Gain Desensitivity

将上公式取导

d A C L A C L = 1 1 + A O L β d A O L A O L \frac{dA_{CL}}{A_{CL}}=\frac{1}{1+A_{OL}\beta}\frac{dA_{OL}}{A_{OL}} ACLdACL=1+AOLβ1AOLdAOL

因为Loop gain T很大, 相比开环增益AOL, 闭环增益 Acl 的变化很小.

我们以CS结构为例

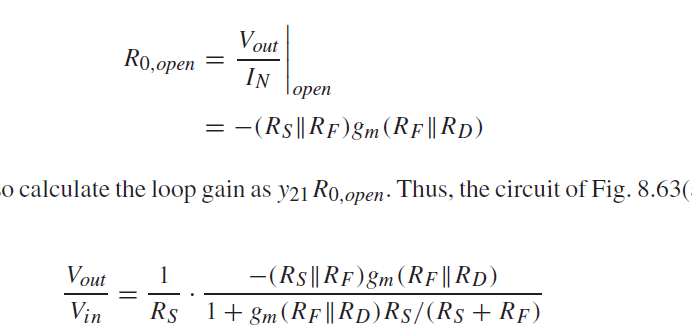

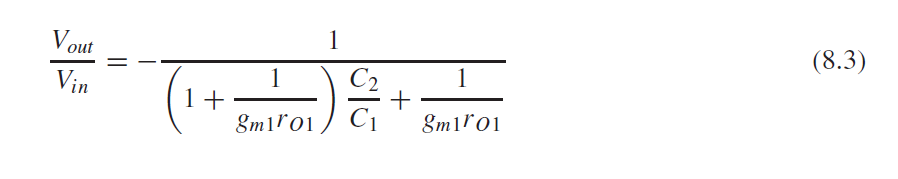

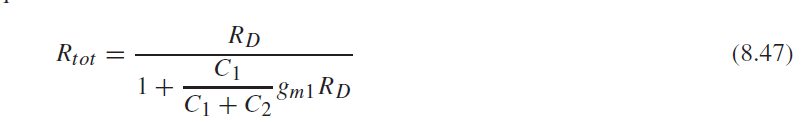

输入输出传函为

gm1*ro1 >> 1, 因此

这样增益就和C1/C2有关, 不取决于gm1*ro1, 变化很小.

Terminal Impedance Modification 控制输入输出阻抗

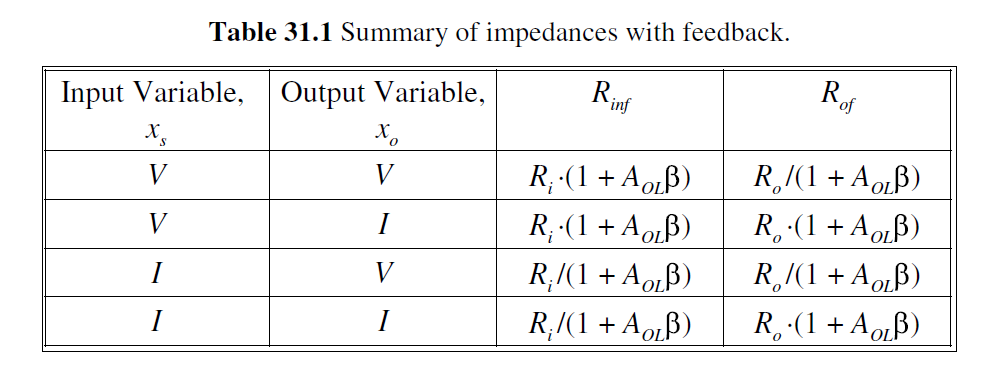

如下图所示, Ri和Ro是开环输入/输出阻抗, Rinf和Rof是闭环输入/输出阻抗.

负反馈可以增加或者降低闭环输入/输出阻抗 (1 + AOL*beta)倍.

闭环输入/输出阻抗取决于输入/输出类型是电压还是电流. 如下图所示.

输入类型是电压 (串联), 闭环输入阻抗增大 (1 + AOL* beta)倍. 输入类型是电流(并联), 闭环输入阻抗减小 (1 + AOL* beta)倍.

输出类型是电压(并联), 闭环输出阻抗减小 (1+AOL* beta)倍. 输出类型是电流(串联), 闭环输出阻抗增大(1+AOL* beta)倍.

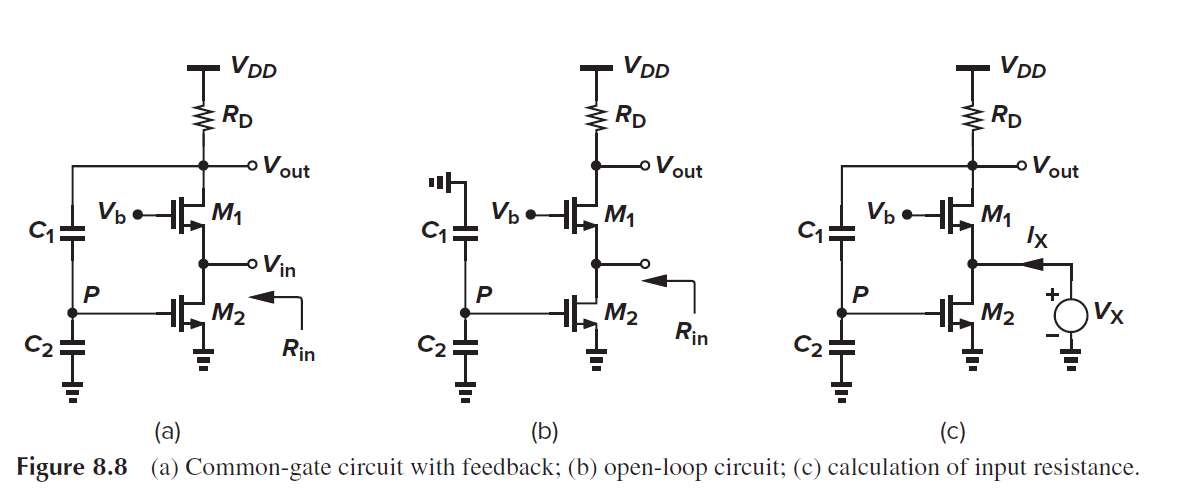

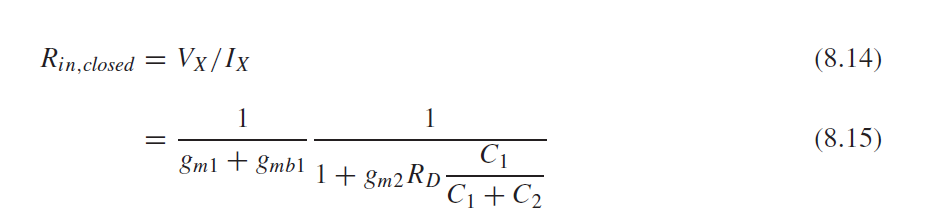

我们以下图CG为例

开环输入阻抗为

输入类型是电流(并联), 输出类型是电压(并联)

因此闭环输入阻抗减小(1+Aol*beta)倍, 闭环输出阻抗减小(1+Aol *beta)倍

输入阻抗

输出阻抗

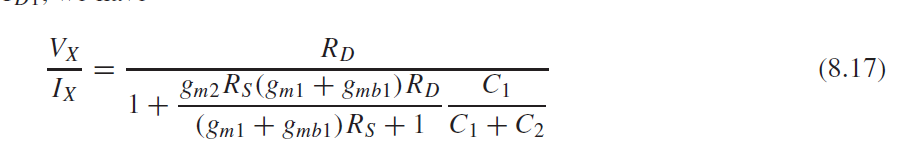

Bandwidth Modification

我们以单负反馈的单极点系统为例

开环系统传输函数为

闭环系统传输函数为

open-loop 传输函数的pole为WH. 经过负反馈后, closed-loop传输函数 的pole为WH=(1+Aol*beta). pole扩展了(1+Loop Gain)倍.

当beta=1, pole最大, 为GBW, 当beta=0, 回到open-loop 场景.

Nonlinearity Reduction

负反馈可以改善op-amp的非线性行为, 如下图所示:

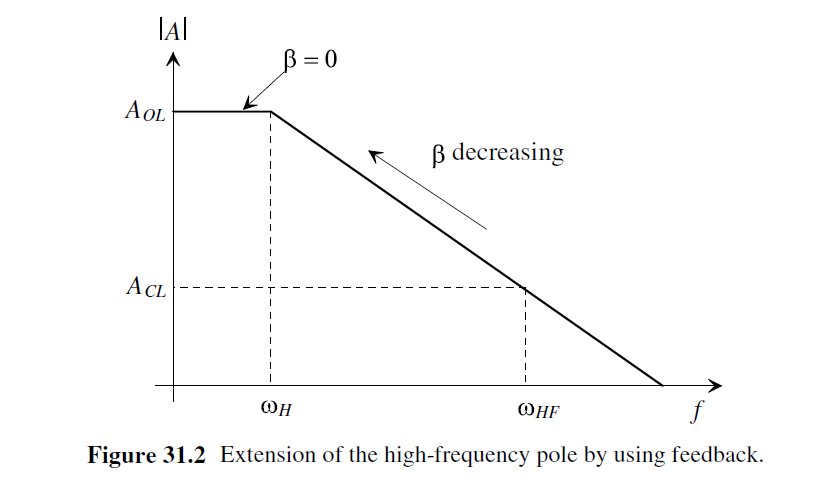

8.1.2 Types of Amplifiers

运放按照输入输出的电压/电流可分为4类

采样电压需要高阻抗, 采样电流需要低阻抗. 生成电压需要低阻抗, 生成电流需要高阻抗. 如下图所示

实际电路参考:

8.1.3 Sense and Return Mechanisms

根据采样和反馈电流/电压类型, 我们可以把反馈分为4种

电压-电压, 电压-电流, 电流-电流, 电流-电压. 第一项为输出采样类型, 第二项为返回输入的类型

输入是电压为series串联(voltage mixing), 输入是电流为shunt并联(voltage mixing).

输出是电压为shunt并联(voltage sampling), 输出是电流为series串联(current sampling).

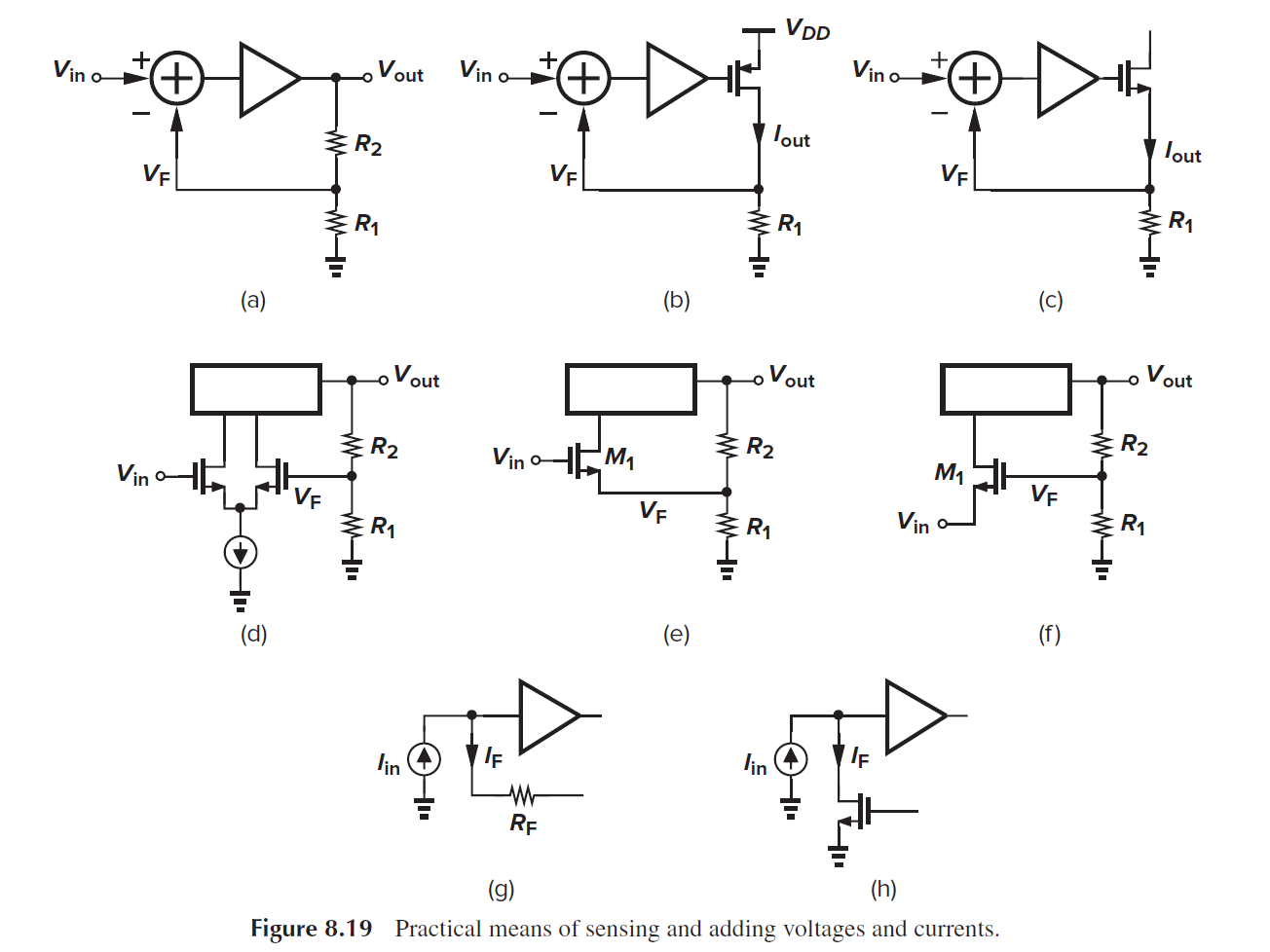

下图展示了采样和反馈类型

a) 采用resistor (or capacitor) divider 采样电压.

b),c)通过一个电阻采样电流.

d) 是采样差分对进行电压相减

e) 和 f) 采用单管实现电压相减

g) 和 h) 实现电流相减

对于电压相减, 输入信号的和反馈信号是两个 不同的点, 而对于电流相减, 是一个点, 这有助于识别反馈类型.

反馈网络实际会影响开环loading, 我们将在8.5小结讨论

8.2 Feedback Topologies

8.2.1 Voltage-Voltage Feedback

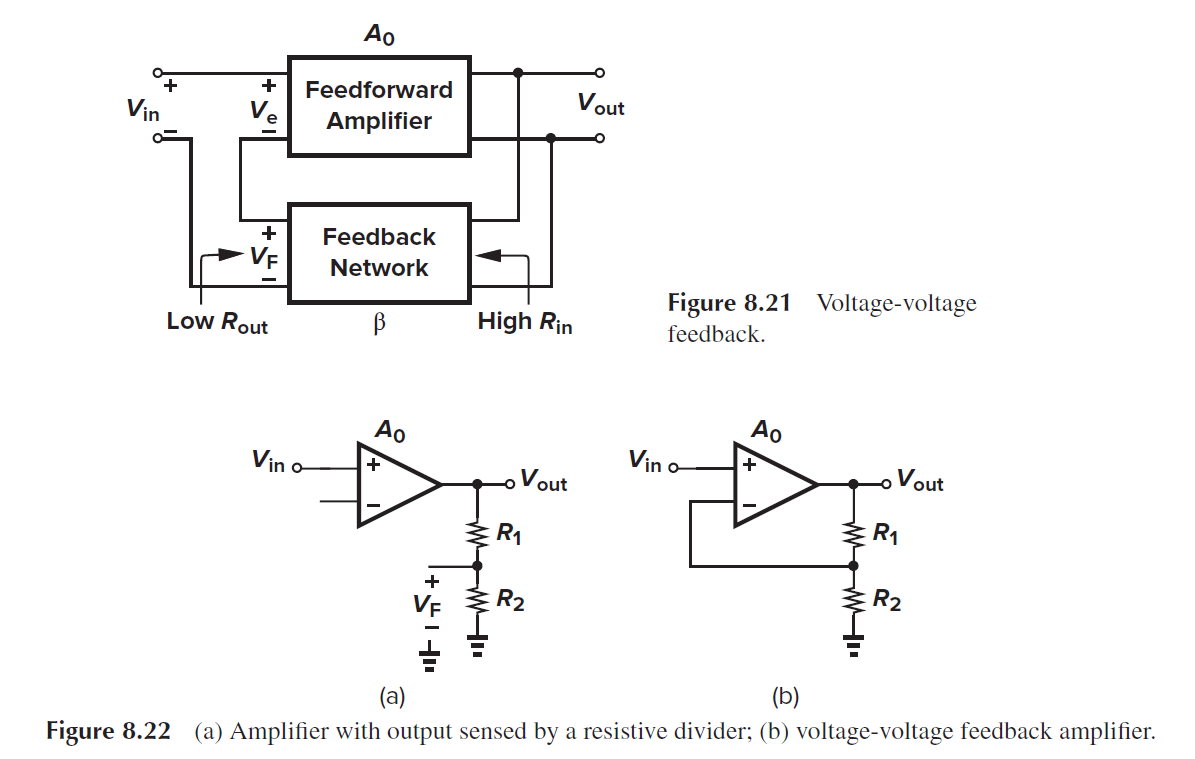

Voltage-Voltage, Series-Shunt, 采样输出电压, 反馈叠加到输入电压, 反馈系统如下图所示

注意第一个电压是输出采样类型, 第二个电压是输入反馈类型. 名称先输出, 再输入

输出阻抗减小为1/(1+beta*A0) 倍

输入阻抗增加1+beta*A0倍

总结: Voltage-Voltage 负反馈, 增加了输入阻抗, 降低了输出阻抗, 可做链接高阻source和低阻load非常好的buffer.

8.2.2 Current-Voltage Feedback

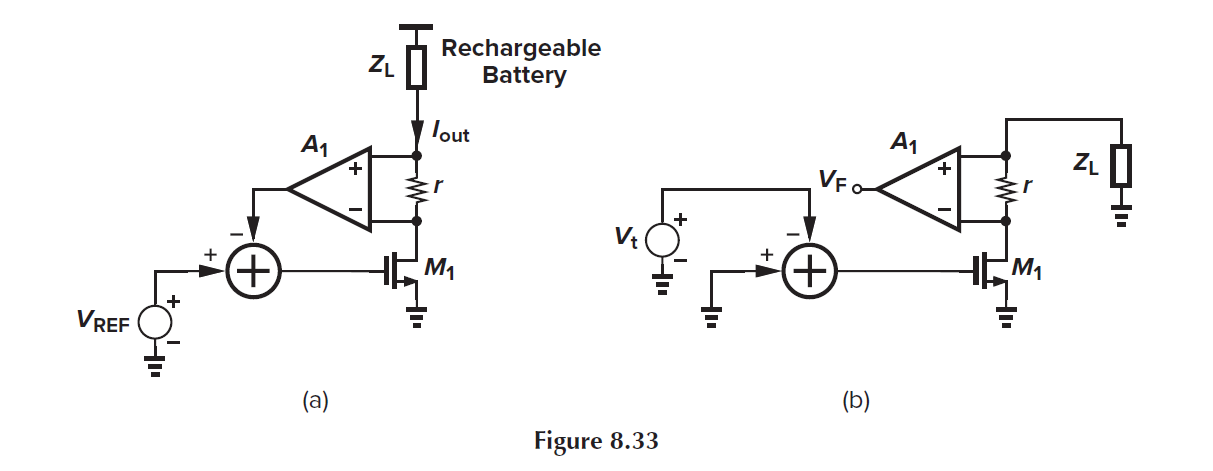

电流-电压反馈, series-series, 采样输出的电流 反馈到输入的电压.

注意第一个电流是输出采样类型, 第二个电压是输入反馈类型. 名称先输出, 再输入

输出阻抗增加1+beta*A0倍

输入阻抗增加1+beta*A0倍

ZL看进去的输出阻抗, 变大为

8.2.3 Voltage-Current Feedback

电压-电流反馈, shunt-shunt, 采样输出的Voltage, 在输入端加入反馈电流

注意第一个电压是输出采样类型, 第二个电流是输入反馈类型. 名称先输出, 再输入

输入阻抗减小1+beta*A0倍

输出阻抗减小1+beta*A0倍

A C L = A O L 1 + A O L ⋅ β A_{CL}=\frac{A_{OL}}{1+A_{OL}\cdot \beta} ACL=1+AOL⋅βAOL

R i n f = R i ( 1 + A O L ⋅ β ) R_{inf}=\frac{R_{i}}{(1+A_{OL}\cdot \beta)} Rinf=(1+AOL⋅β)Ri

R o f = R o ( 1 + A O L ⋅ β ) R_{of}=\frac{R_{o}}{(1+A_{OL}\cdot \beta)} Rof=(1+AOL⋅β)Ro

输出阻抗

输入阻抗

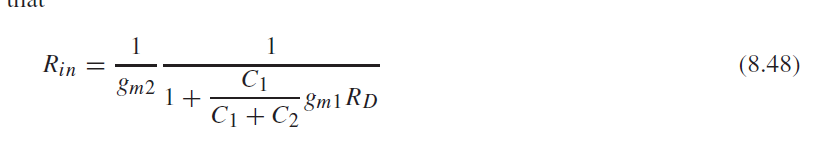

低输入阻抗可应用于光通信做receivers,通过加入负反馈, 输入阻抗从R1减小为 R1/(1 + A). 输出电压−R1*ID1.

bandwidth从1/(2π R1CD1) 增加为 (1 + A)/(2π R1CD1)

8.2.4 Current-Current Feedback

电流-电流, Shunt-Series, 负反馈如下图所示, 采样输出的电流, 在输入端加入反馈电流,

注意第一个电流是输出采样类型, 第二个电流是输入反馈类型. 名称先输出, 再输入

输出阻抗减小1+beta*A0倍

输入阻抗增大1+beta*A0倍

8.3 Effect of Feedback on Noise

反馈电路并不提升电路的噪声性能. 如果忽略反馈网络引入的噪声, input-referred噪声不变.

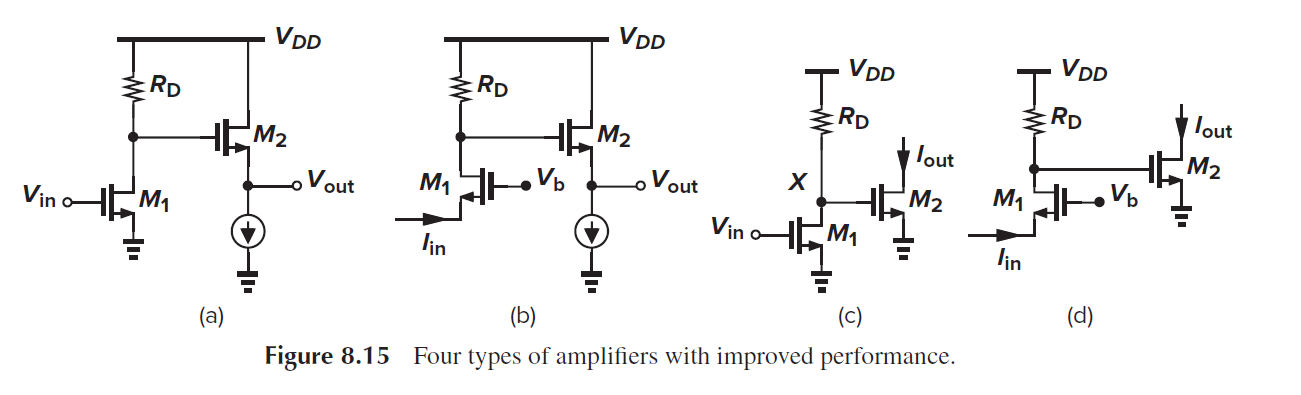

8.4 Feedback Analysis Difficulties

分析负反馈电路包括几个步骤

a) break loop, 找到开环增益和输入输出阻抗

b) 决定环路增益 loop gain, 和闭环参数 (取决于开环参数)

c) 通过环路增益 loop gain来判断稳定性.

断环点选取很有讲究, 一般选取高阻节点, 防止断环影响环路增益的计算.

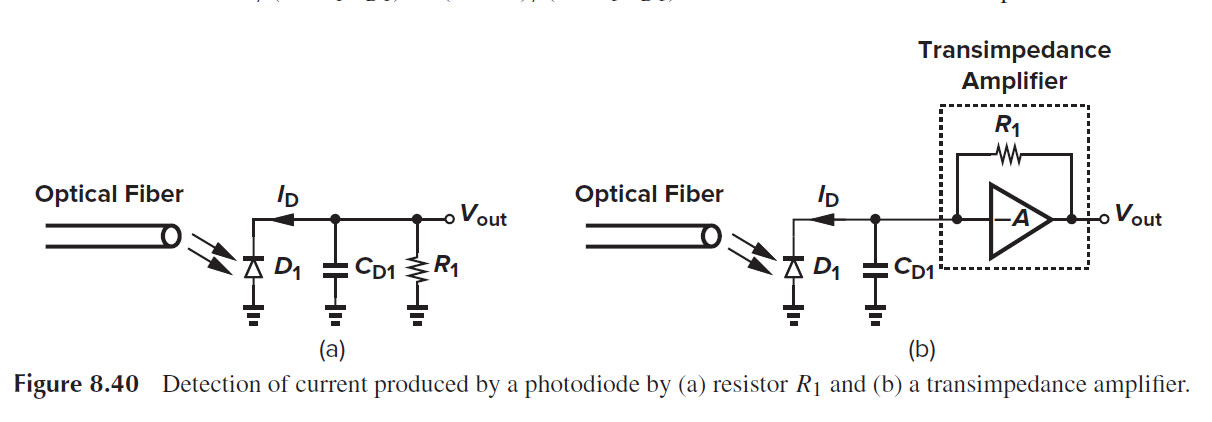

但在实际电路分析中, 断环分析不是那么容易, 有时候很难看出负反馈电路. 例如degenerated CS结构. 或者部分电路既作为反馈, 又作为loading, 或者一个环路有多重反馈. 下图展示了负反馈分析中的难点

我们可以用下面三种方法来解决

8.5 Effect of Loading