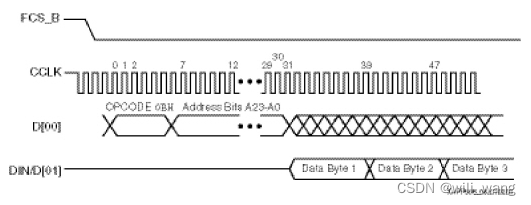

在 FPGA 完成自初始化后,INIT 释放,FPGA 对模式引脚 (M[2:0]) 进行采样,以确定使用哪种配置模式。当模式引脚 M[2:0] = 001 时,FPGA 开始以大约 3 MHz 的频率在 CCLK 上输出时钟。随后,FCS_B 驱动为低电平,紧接着在 D[00] 引脚上发送一个 x1 快速读取指令的操作码和地址,如下图所示。

数据最初以 x1 模式从 SPI 闪存传输到 FPGA。切换到外部时钟、x2 或 x4 总线宽度或其他选项的命令都包含在位流的早期部分。在读取这些选项之后,FPGA 会进行中间配置调整。

默认情况下,数据在 CCLK 的下降沿从 SPI 闪存输出,并在 CCLK 的上升沿被 FPGA 捕获。默认行为可以通过启用 set_property BITSTREAM.CONFIG.SPI_FALL_EDGE: YES(Vivado 设计套件)和 bitgen -g SPI_FALL_EDGE:yes(ISE 设计套件)选项更改为在下降沿捕获。