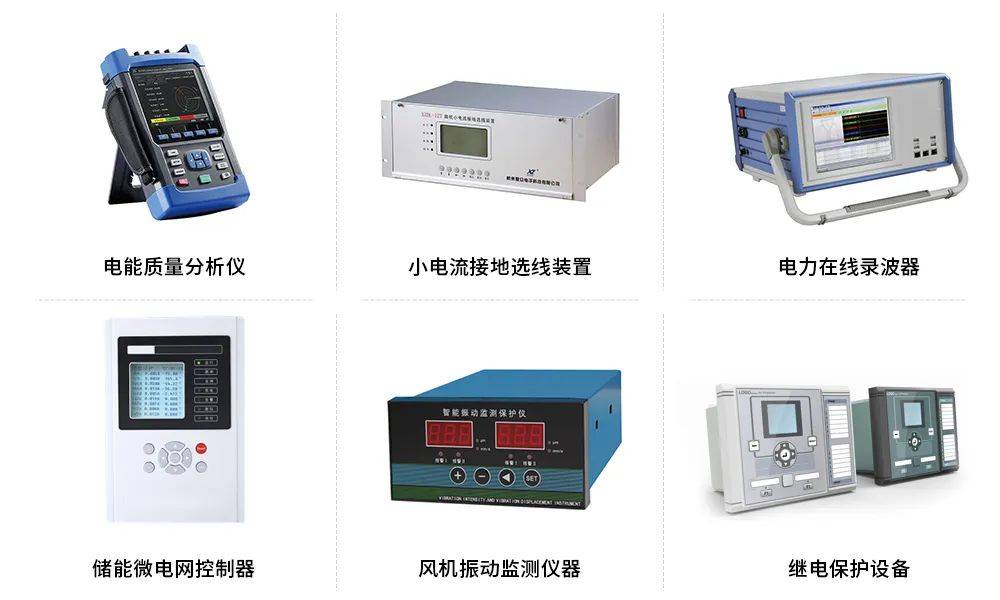

近年来,随着中国新基建、中国制造2025规划的持续推进,单ARM处理器越来越难胜任工业现场的功能要求,特别是如今能源电力、工业控制、智慧医疗等行业,往往更需要ARM + FPGA架构的处理器平台来实现例如多路/高速AD采集、多路网口、多路串口、多路/高速并行DI/DO、高速数据并行处理等特定功能,因此ARM + FPGA架构处理器平台愈发受市场欢迎。

因此,创龙科技一年前正式推出了国产化率100%的ARM + FPGA工业核心板,它基于全志T3 + 紫光同创Logos处理器设计。

全志T3为准车规级芯片,四核ARM Cortex-A7架构,主频高达1.2GHz,支持双路网口、八路UART、SATA大容量存储接口,同时支持4路显示、GPU以及1080P H.264视频硬件编解码。另外,创龙科技已在T3平台适配国产嵌入式系统翼辉SylixOS,真正实现软硬件国产化。

紫光同创Logos PGL25G/PGL50G FPGA在工业领域应用广泛,逻辑资源分别为27072/51360,与国外友商产品pin to pin兼容,主要用于多通道/高速AD采集或接口拓展。因其价格低、质量稳定、开发环境易用等优点,受到工业用户的广泛好评。尤其是开发环境,最快3天可完成从国外友商产品到紫光同创产品的切换。

图1 ARM + FPGA典型应用场景

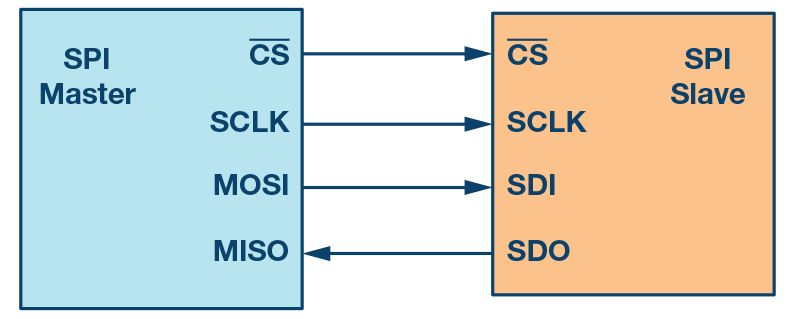

SPI通信优势与应用场景

SPI(Serial Peripheral Interface)是一种用于串行数据传输的通信协议,SPI通信具有带宽高、实时性强、传输速度快、连接简单、可靠性高和灵活性强等优势。

SPI协议适用于许多嵌入式系统和外围设备之间的通信需求,可提供快速、可靠和灵活的数据传输,非常适合"小数据-低时延 "和"大数据-高带宽"的应用场景。

图2 SPI通信总线

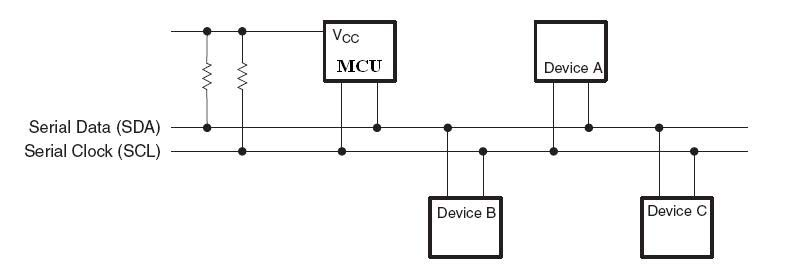

I2C通信优势和应用场景

I2C(Inter-Integrated Circuit)是一种串行双向通信协议,I2C通信具有硬件资源需求低、简单灵活、可靠性高和支持多种设备类型等优势。

I2C协议可提供简单、可靠和灵活的数据传输。它广泛应用于各种传感器、存储设备、显示设备和通信模块等领域。适用控制命名传输和系统配置的应用场景。

图3 I2C通信总线

国产T3 + FPGA的SPI与I2C通信方案介绍

本章节主要介绍全志科技T3与紫光同创Logos基于SPI、I2C的ARM + FPGA通信方案,使用的硬件平台为:创龙科技TLT3F-EVM工业评估板。

I2C通信案例

**案例功能:**实现T3(ARM Cortex-A7)与FPGA的TWI(I2C)通信功能。

FPGA案例源码为"4-软件资料\Demo\fpga-demo\i2c_slave",实现I2C Slave功能,并内置用户可读写寄存器、LED寄存器、KEY寄存器。

ARM端作为I2C Master,可通过TWI(I2C)总线读写FPGA端用户可读写寄存器0x00、LED写寄存器0x01(写1则点亮FPGA端LED,写0则熄灭),以及查看KEY寄存器0x02检测FPGA端用户输入按键状态。

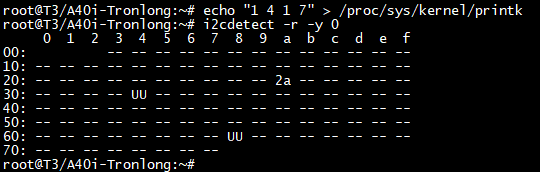

**案例测试:**评估板上电,请先加载运行FPGA端可执行程序。执行如下命令可查看到I2C总线上的挂载设备,其中0x2a为FPGA端I2C Slave的地址。

**Target#**echo "1 4 1 7" > /proc/sys/kernel/printk //屏蔽内核printk打印,避免I2C驱动扫描找不到设备时打印警告信息

**Target#**i2cdetect -r -y 0

图4

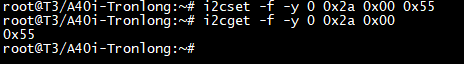

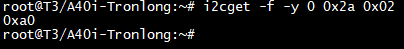

执行如下命令,读写FPGA端用户可读写寄存器0x00。

**Target#**i2cset -f -y 0 0x2a 0x00 0x55 //往寄存器0x00写0x55

**Target#**i2cget -f -y 0 0x2a 0x00 //读取寄存器0x00,值为0x55

图5

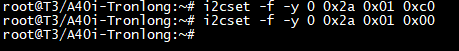

执行如下命令,写FPGA端LED寄存器0x01,实现对FPGA端用户可编程指示灯控制。

**Target#**i2cset -f -y 0 0x2a 0x01 0xc0 //往LED寄存器0x01写0xc0,点亮FPGA端LED3、LED4

**Target#**i2cset -f -y 0 0x2a 0x01 0x00 //往LED寄存器0x01写0x00,熄灭FPGA端LED3、LED4

图6

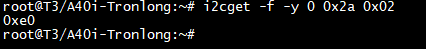

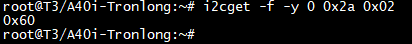

执行如下命令,读FPGA端KEY寄存器0x02,实现对FPGA端用户输入按键的状态检测。

**Target#**i2cget -f -y 0 0x2a 0x02 //读取KEY寄存器0x02,值为0xe0

图7

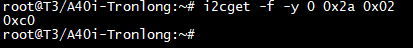

请按下FPGA端用户输入按键KEY7并保持按下状态,再执行如下命令。

**Target#**i2cget -f -y 0 0x2a 0x02 //读取KEY寄存器0x02,值为0xc0

图8

请按下FPGA端用户输入按键KEY8并保持按下状态,再执行如下命令。

**Target#**i2cget -f -y 0 0x2a 0x02 //读取KEY寄存器0x02,值为0xa0

图9

请按下FPGA端用户输入按键KEY9并保持按下状态,再执行如下命令。

**Target#**i2cget -f -y 0 0x2a 0x02 //读取KEY寄存器0x02,值为0x60

图10

基于Linux的SPI通信案例

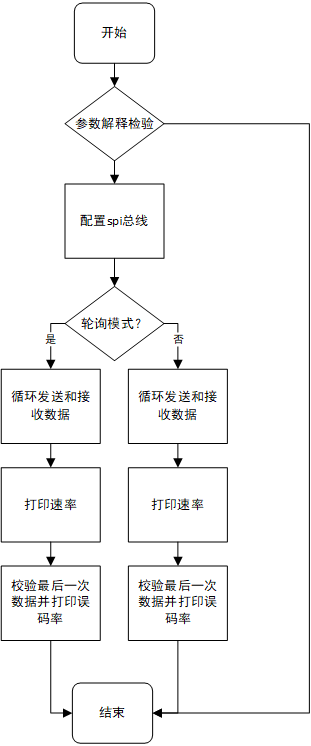

**案例功能:**基于Linux系统,实现T3(ARM Cortex-A7)与FPGA的SPI通信功能。

ARM端案例源码为"4-软件资料\Demo\module-demos\spi_rw",实现SPI Master功能,具体如下:

(1)打开SPI设备节点,如:/dev/spidev0.1。

(2)使用ioctl配置SPI总线,如SPI总线极性和相位、通信速率、数据长度等。

(3)选择模式为单线模式或双线模式。当设置SPI总线为双线模式时,发送数据为单线模式,接收数据为双线模式。

(4)发送数据至SPI总线,以及从SPI总线读取数据。

校验数据,然后打印读写速率、误码率。

FPGA端案例源码为"4-软件资料\Demo\fpga-demos\dram_spi"和"4-软件资料\Demo\fpga-demos\dram_spi_dual",实现SPI Slave功能,具体说明如下:

(1)将SPI Master发送的数据保存至DRAM。

(2)SPI Master发起读数据时,FPGA从DRAM读取数据通过SPI总线传输至SPI Master。

当SPI总线为双线模式时,接收数据支持双线模式,而发送数据仅支持单线模式。

图11 ARM端程序流程图

**案例测试:**评估板上电,请先加载运行FPGA端可执行程序,若进行SPI单线模式测试,请运行案例"dram_spi\bin\"目录下的程序可执行文件;若进行SPI双线模式测试,请运行"dram_spi_dual\bin\"目录下的程序可执行文件。同时将ARM端可执行程序spi_rw拷贝至评估板文件系统任意目录下。

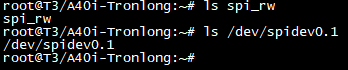

进入评估板文件系统,执行如下命令查看新生成的spidev设备节点。

**Target#**ls /dev/spidev0.1

图12

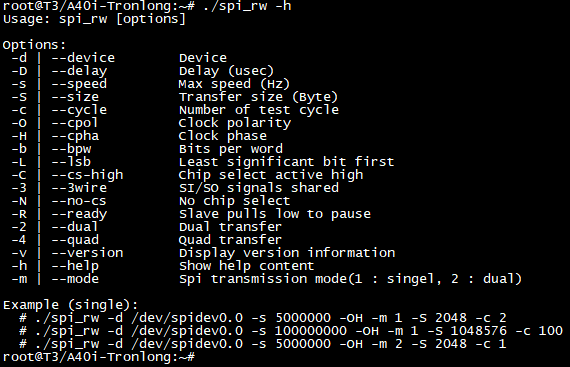

执行如下命令查询程序命令参数。

Target#./spi_rw -h

图13

1 SPI单线模式

1.1 功能测试

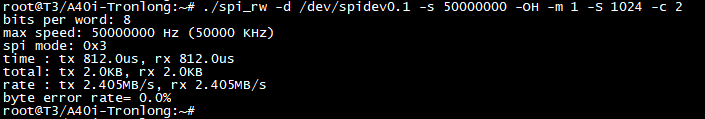

执行如下命令运行程序,ARM通过SPI总线写入1KByte随机数据至FPGA DRAM,然后读出数据、进行数据校验,同时打印SPI总线读写速率和误码率,最终实测写速率为2.405MB/s,读速率为2.405MB/s,误码率为0。如下图所示。

Target#./spi_rw -d /dev/spidev0.1 -s 50000000 -OH -m 1 -S 1024 -c 2

参数解析:

-d:设备节点;

-s:设置通信时钟频率(Hz),本次测试设置SPI总线通信时钟频率为50MHz,则SPI单线模式理论通信速率为:(50000000 / 1024 / 1024 / 8)MB/s ≈ 5.96MB/s;

-O:空闲状态时,SCLK为高电平(CPOL=1);

-H:从第二个跳变沿开始采样(CPHA=1);

-m:选择模式传输模式(1表示单线模式,2表示双线模式);

-S:设置传输数据大小,单位为Byte;

-c:循环传输数据包的次数。

图14

1.2 性能测试

(1)基于50MHz时钟频率

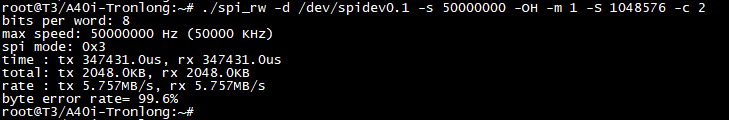

执行如下命令运行程序,基于50MHz时钟频率、增大读写数据量测试SPI总线最高传输速率。ARM通过SPI总线写入1MByte随机数据至FPGA DRAM,然后读出数据,不做数据检验,最后打印SPI总线读写速率和误码率,如下图所示。

备注:本案例设计一次读写1KByte随机数据至FPGA DRAM,因此误码率较高。

Target#./spi_rw -d /dev/spidev0.1 -s 50000000 -OH -m 1 -S 1048576 -c 2

图15

本次测试设置SPI总线通信时钟频率为50MHz,则SPI单线模式理论通信速率为:(50000000 / 1024 / 1024 / 8)MB/s ≈ 5.96MB/s。从上图可知,本次实测写速率为5.757MB/s,读速率为5.757MB/s,接近理论通信速率。

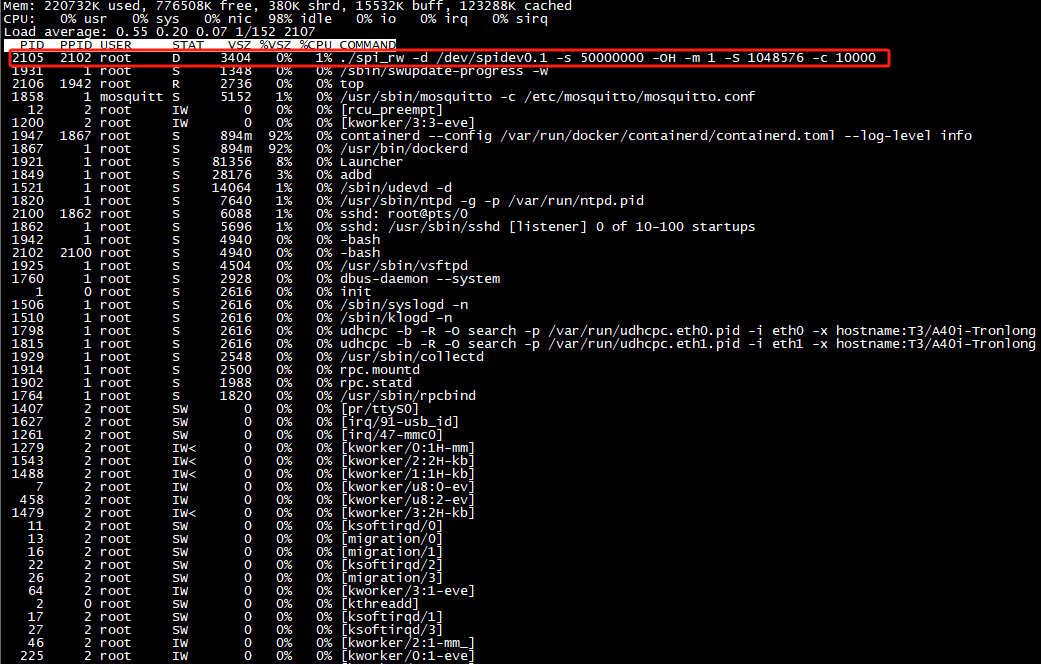

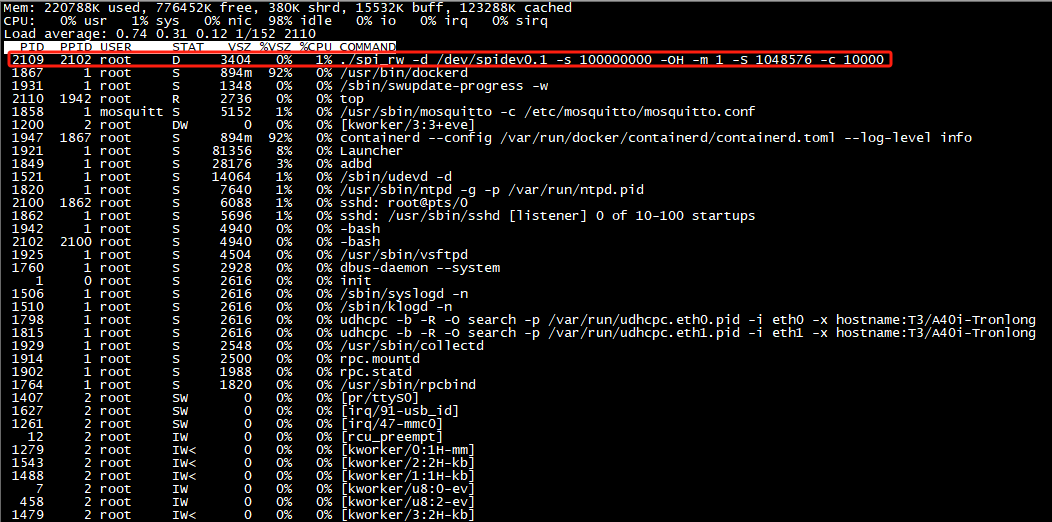

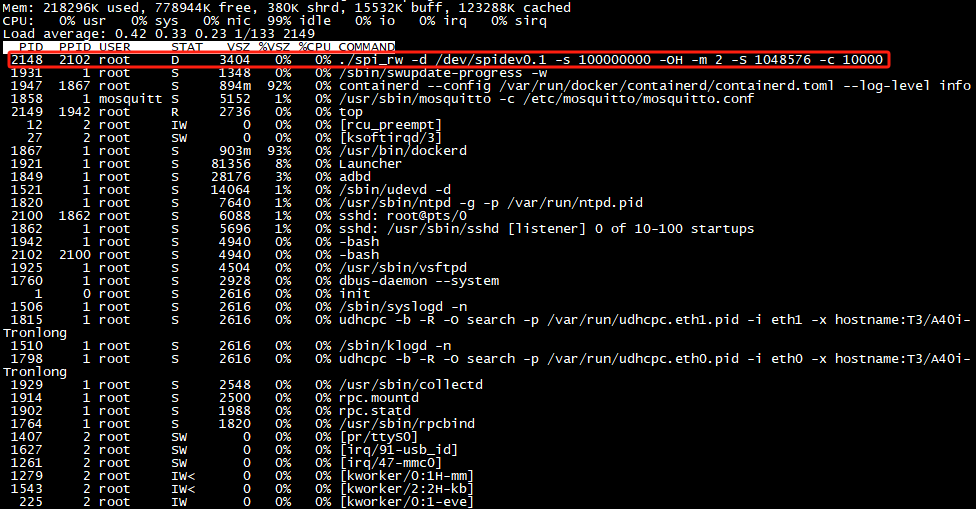

本次测试SPI使用了DMA传输,测得CPU的占用率约为1%,如下图所示。

图16

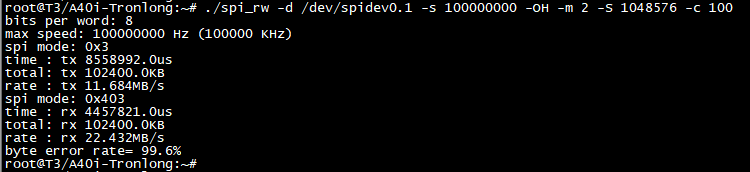

(2)基于100MHz时钟频率

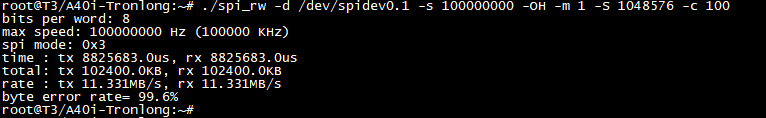

执行如下命令运行程序,测试基于100MHz时钟频率的SPI单线模式的最高通信带宽。ARM通过SPI总线写入1MByte随机数据至FPGA DRAM并读出数据,不做数据检验,最后打印SPI总线读写速率和误码率,如下图所示。

备注:本次测试旨在测试SPI的最高传输速率,目前SPI速率最大支持50MHz时钟频率,当时钟频率配置到最大100MHz时速率会出现时序问题,现象是整体往右移了1bit。例如发送10000000,实际接收到01000000,并在测试中出现误码。

Target#./spi_rw -d /dev/spidev0.1 -s 100000000 -OH -m 1 -S 1048576 -c 100

图17

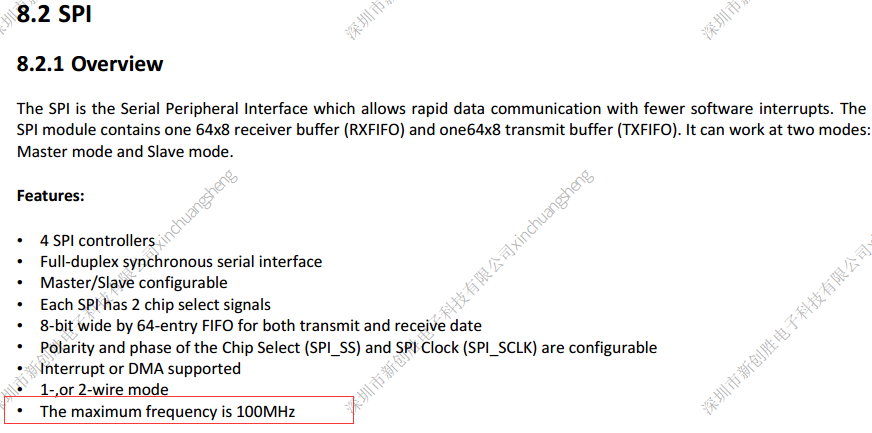

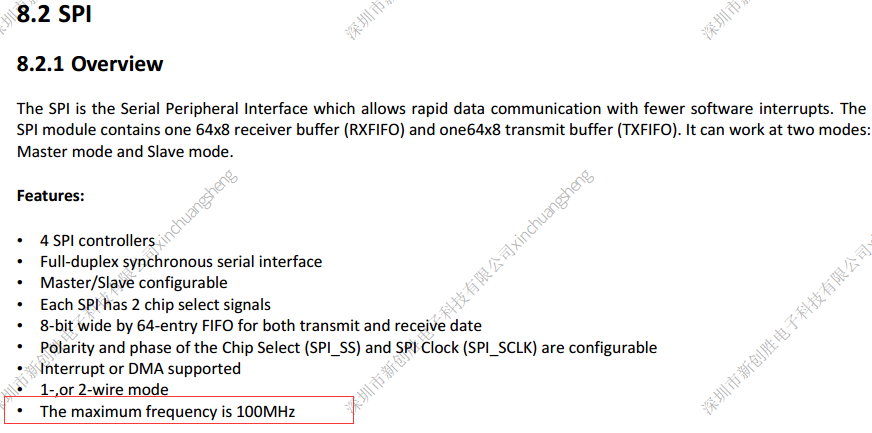

根据官方数据手册(如下图),SPI总线通信时钟频率理论值最大为100MHz。本次测试设置SPI总线通信时钟频率为最大值100MHz,则SPI单线模式理论速率为:(100000000 / 1024 / 1024 / 8)MB/s ≈ 11.92MB/s。从上图可知,在100MHz下实测SPI单线模式写速率为:11.331MB/s,SPI单线模式读速率为:11.331MB/s,接近理论通信速率。

图18

本次测试SPI使用了DMA传输,测得CPU的占用率约为1%,如下图所示。

图19

2 SPI双线模式

2.1 功能测试

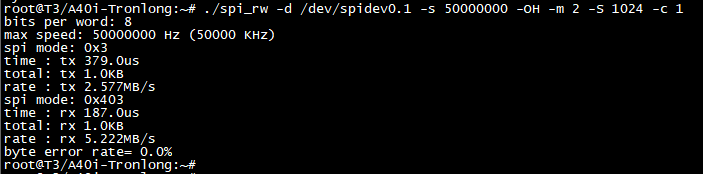

执行如下命令运行程序,ARM通过SPI总线写入1KByte随机数据至FPGA DRAM,然后读出数据、进行数据校验,同时打印SPI总线读写速率和误码率,如下图所示。

Target#./spi_rw -d /dev/spidev0.1 -s 50000000 -OH -m 2 -S 1024 -c 1

参数解析:

-d:设备节点;

-s:设置通信时钟频率(Hz),本次测试设置SPI总线通信时钟频率为50MHz,则SPI双线模式理论通信速率为:(50000000 / 1024 / 1024 / 4)MB/s ≈ 11.92MB/s;

-O:空闲状态时,SCLK为高电平(CPOL=1);

-H:从第二个跳变沿开始采样(CPHA=1);

-m:选择模式传输模式(1表示单线模式,2表示双线模式);

-S:设置传输数据大小,单位为Byte;

-c:循环传输数据包的次数。

图20

从上图可知,本次实测写速率为2.577MB/s,读速率为5.222MB/s,误码率为0。

2.2 性能测试

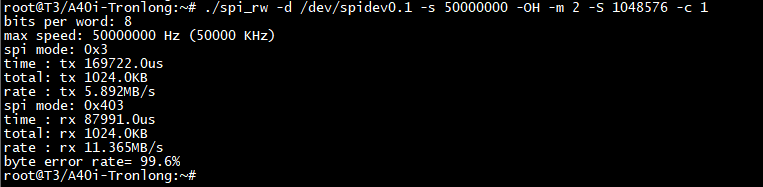

(1)基于50MHz时钟频率

执行如下命令运行程序,基于50MHz时钟频率、增大读写数据量测试SPI总线最高传输速率。ARM通过SPI总线写入1MByte随机数据至FPGA DRAM,然后读出数据,不做数据检验,最后打印SPI总线读写速率和误码率,最终本次实测写速率为5.892MB/s,读速率为11.365MB/s。如下图所示。

备注:本案例设计一次读写1KByte随机数据至FPGA DRAM,因此误码率较高。

Target#./spi_rw -d /dev/spidev0.1 -s 50000000 -OH -m 2 -S 1048576 -c 1

图21

本次测试设置SPI总线通信时钟频率为50MHz,则SPI单线模式理论通信速率为:(50000000/1024/1024/8)MB/s ≈ 5.96MB/s;SPI双线模式理论通信速率为:(50000000 / 1024 / 1024 / 4)MB/s ≈ 11.92MB/s。

本次测试SPI使用了DMA传输,测得CPU的占用率约为0%,如下图所示。

图22

(2)基于100MHz时钟频率

执行如下命令运行程序,测试基于100MHz时钟频率的SPI双线模式的最高通信带宽。ARM通过SPI总线写入1MByte随机数据至FPGA DRAM并读出数据,不做数据检验,最后打印SPI总线读写速率和误码率,最终在100MHz下实测SPI双线模式写速率为:11.684MB/s,SPI双线模式读速率为:23.432MB/s。如下图所示。

备注:本次测试旨在测试SPI的最高传输速率,目前SPI速率最大支持50MHz时钟频率,当时钟频率配置到最大100MHz时速率会出现时序问题,现象是整体往右移了1bit。例如发送10000000,实际接收到01000000,并在测试中出现误码。

Target#./spi_rw -d /dev/spidev0.1 -s 100000000 -OH -m 2 -S 1048576 -c 100

图23

根据官方数据手册(如下图),SPI总线通信时钟频率理论值最大为100MHz。本次测试设置SPI总线通信时钟频率为最大值100MHz,则SPI单线模式理论通信速率为:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s;SPI双线模式理论速率为:(100000000 / 1024 / 1024 / 4)MB/s ≈ 23.84MB/s。

图24

本次测试SPI使用了DMA传输,测得CPU的占用率约为0%,如下图所示。

图25

基于Linux-RT的SPI通信案例

案例功能:基于Linux-RT实时系统,演示T3(ARM Cortex-A7)与FPGA之间的SPI通信功能。本案例通信数据量少、带宽低,但实时性高,适用于对通信带宽要求不高,但通信实时性有严格要求的工控场合。

ARM端案例源码为"4-软件资料\Demo\module-demos\rt_spi_rw",实现SPI Master功能,具体如下:

(1)打开SPI设备节点。如:/dev/spidev0.1。

(2)使用ioctl配置SPI总线。如SPI总线极性和相位、通信速率、数据字长度等。

(3)创建实时线程。

(4)发送数据至SPI总线,以及从SPI总线读取数据。

(5)打印发送、接收的速率和传输耗时。

校验数据,然后打印读写速率、误码率。

FPGA端案例源码为"4-软件资料\Demo\fpga-demos\dram_spi",实现SPI Slave功能,具体如下:

(1)将SPI Master发送的数据保存至DRAM。

SPI Master发起读数据时,FPGA从DRAM读取数据并通过SPI总线传输至SPI Master。

图26 ARM端程序流程图

**案例测试:**由于我司默认使用是的Linux内核,因此需参考Linux系统使用手册文档中的"替换内核、内核模块"章节将Linux系统启动卡替换为Linux-RT系统。

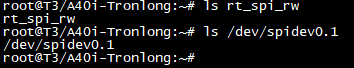

评估板上电,请先加载运行FPGA端可执行程序。将ARM端可执行文件rt_spi_rw拷贝至评估板文件系统任意目录下,执行如下命令,查看新生成的spidev设备节点。

**Target#**ls /dev/spidev0.1

图27

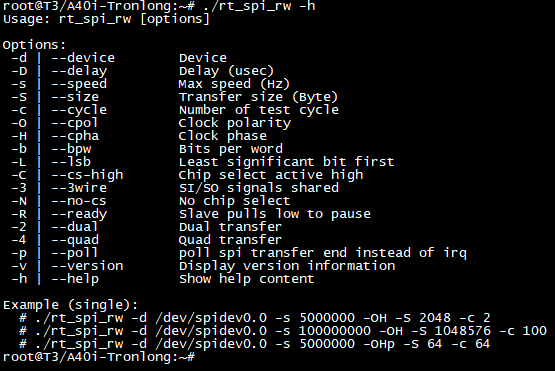

执行如下命令,查询程序命令参数。

Target#./rt_spi_rw -h

图28

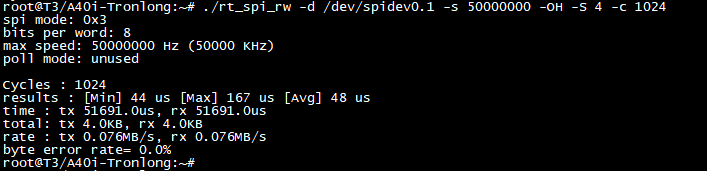

1 非轮询方式

执行如下命令运行程序,ARM通过SPI总线写入随机数据至FPGA DRAM,然后读出数据、进行数据校验,同时打印SPI总线读写速率、传输耗时和误码率,最终实测最小耗时为44us,最大耗时为167us,平均耗时为48us;写速率为0.076MB/s,读速率为0.076MB/s,误码率为0。如下图所示。

Target#./rt_spi_rw -d /dev/spidev0.1 -s 50000000 -OH -S 4 -c 1024

参数解析:

-d:设备节点;

-s:设置通信时钟频率(Hz),本次测试设置SPI总线通信时钟频率为50MHz,则理论通信速率为:(50000000 / 1024 / 1024 / 8)MB/s ≈ 5.96MB/s;

-O:空闲状态时,SCLK为高电平(CPOL=1);

-H:从第二个跳变沿开始采样(CPHA=1);

-S:设置传输数据大小,单位为Byte;

-c:循环传输数据包的次数。

图29

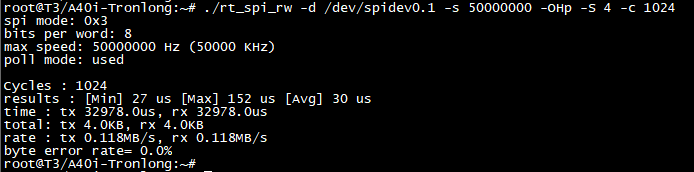

2 轮询方式

执行如下命令运行程序,ARM通过SPI总线写入4Byte随机数据至FPGA DRAM,读出数据、进行数据校验,同时打印SPI总线读写速率、传输耗时和误码率,最终实测最小耗时为27us,最大耗时为152us,平均耗时为30us;写速率为0.118MB/s,读速率为0.118MB/s,误码率为0。如下图所示。

Target#./rt_spi_rw -d /dev/spidev0.1 -s 50000000 -OHp -S 4 -c 1024

参数解析:

-d:设备节点;

-s:设置通信时钟频率(Hz),本次测试设置SPI总线通信时钟频率为50MHz,则理论通信速率为:(50000000 / 1024 / 1024 / 8)MB/s ≈ 5.96MB/s;

-O:空闲状态时,SCLK为高电平(CPOL=1);

-H:从第二个跳变沿开始采样(CPHA=1);

-p:SPI发送端采用轮询方式(每次发送数据量≤64Byte);

-S:设置传输数据大小,单位为Byte;

-c:循环传输数据包的次数。

图30