System Generator

流程

工具包:

VIVADO 2017.3

Matlab 2017a

图 1‑1 system generator 版本要对应才能打开

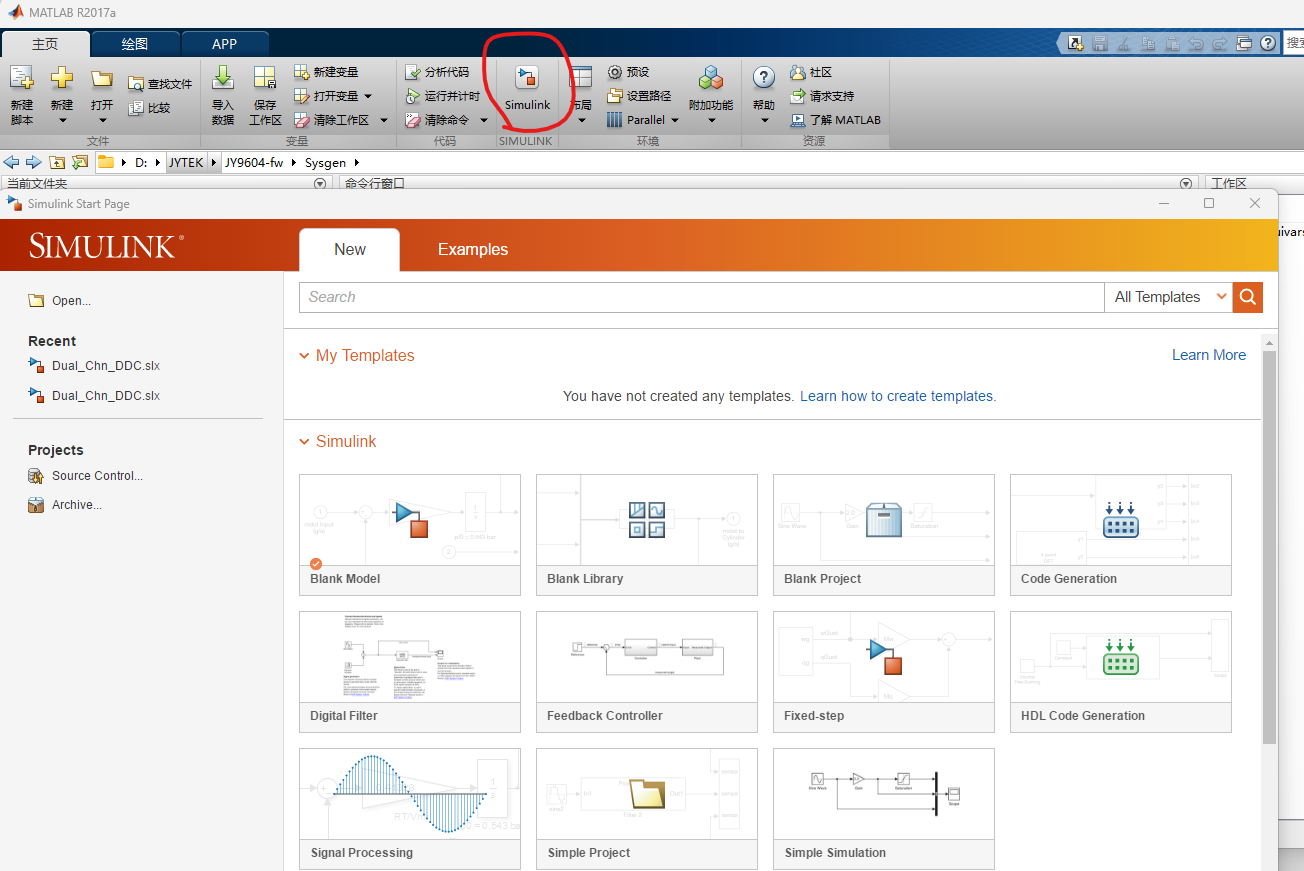

新建simulink

打开system generator, 创建simulink 文件

图 1‑2 创建simulink文件

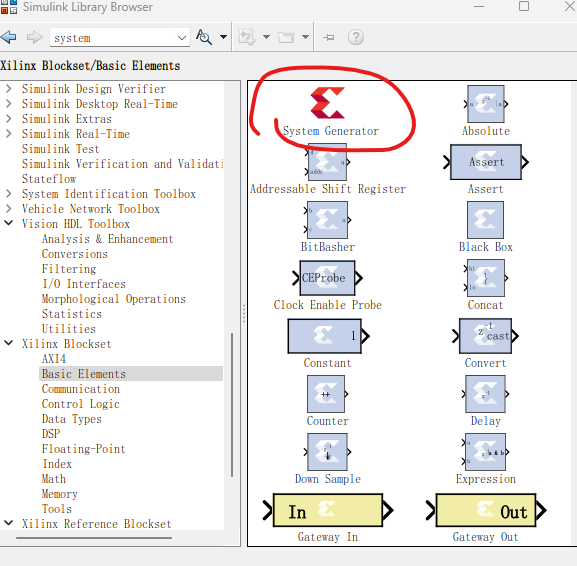

添加system generator

图 1‑3 创建文件 打开库模型

图 1‑4 添加基础模型 工具就知道要用到xilinx 设计中去

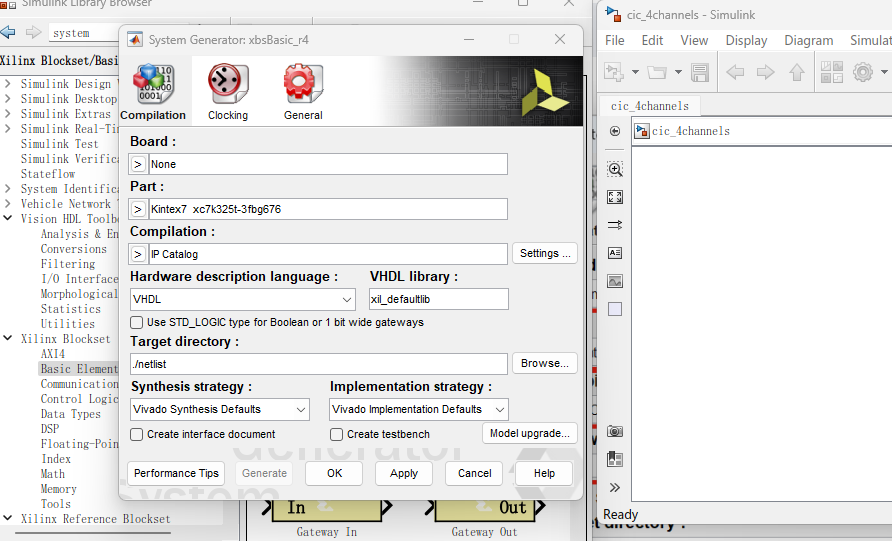

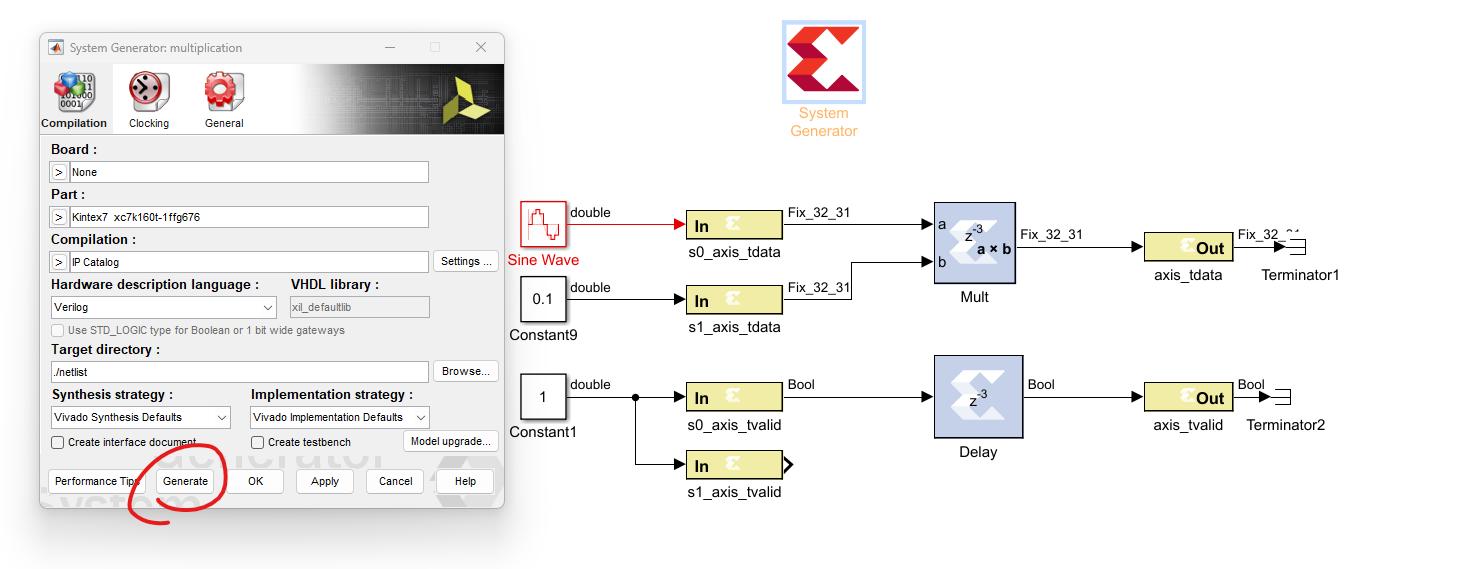

图 1‑5 双击设置 选择实际要用的器件

生成的硬件描述语言根据个人喜好,习惯verilog 就选verilog.

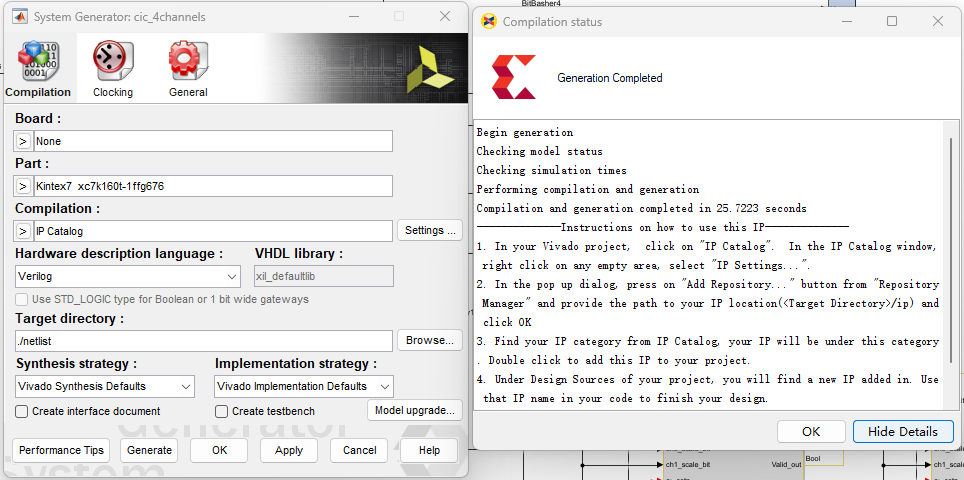

图 1‑6 编译完成如何使用IP

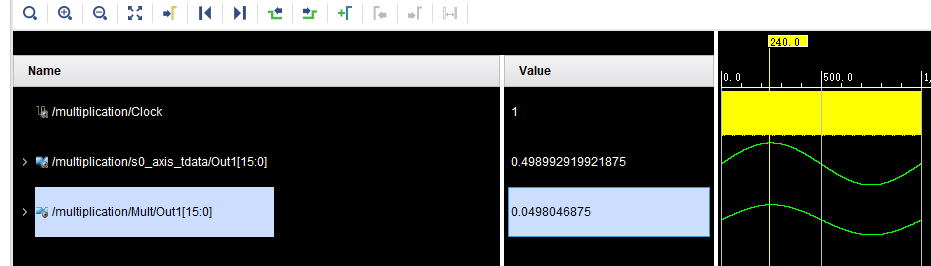

乘法示例

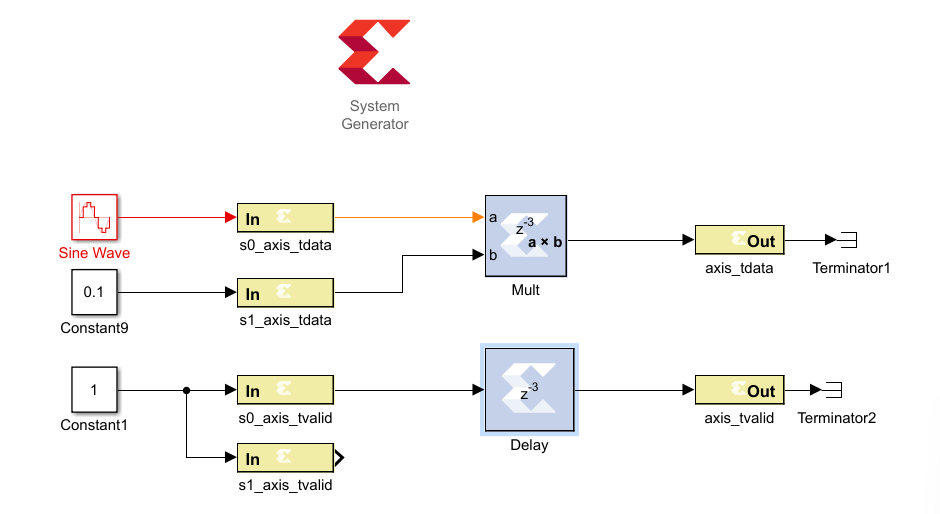

图 1‑7 乘法示例

其中输入数据认为是0-1之间的数据,16bit,输出数据也截断到0-1之间。

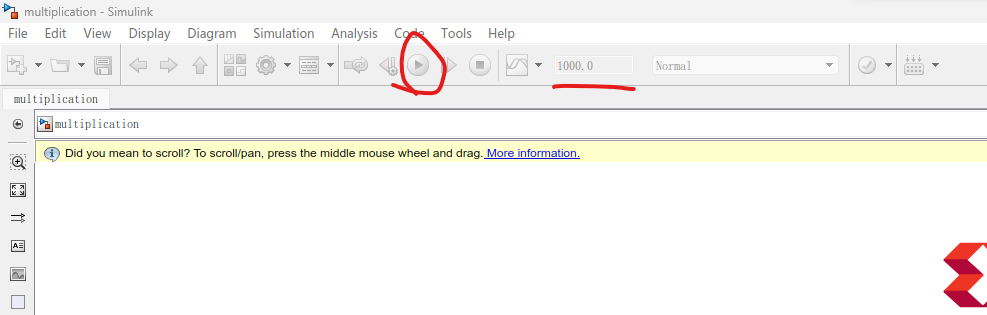

仿真

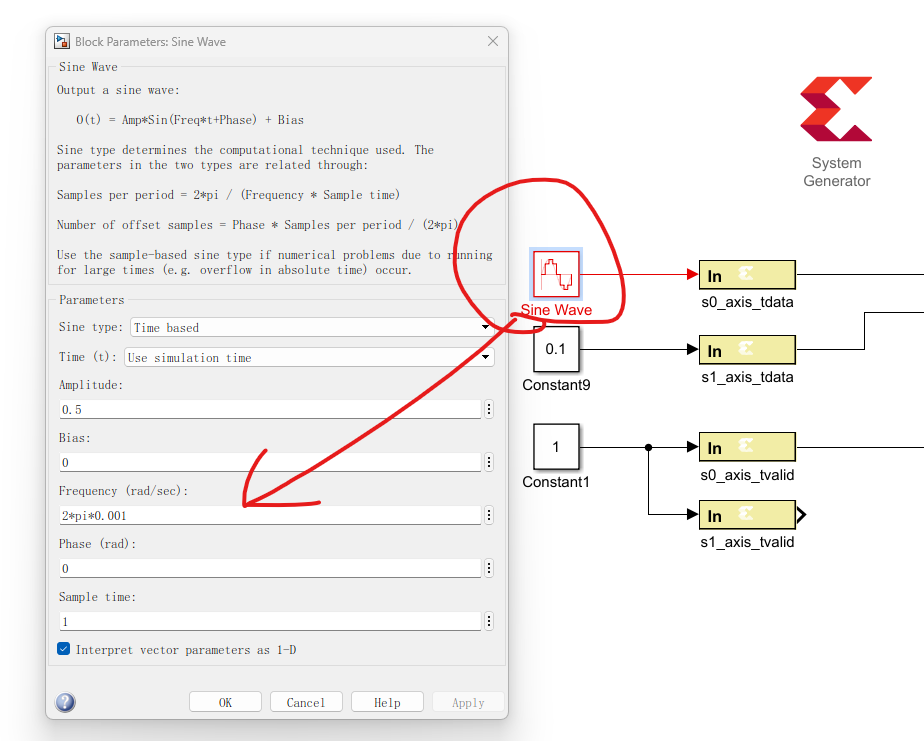

图 1‑8 仿真波形输入

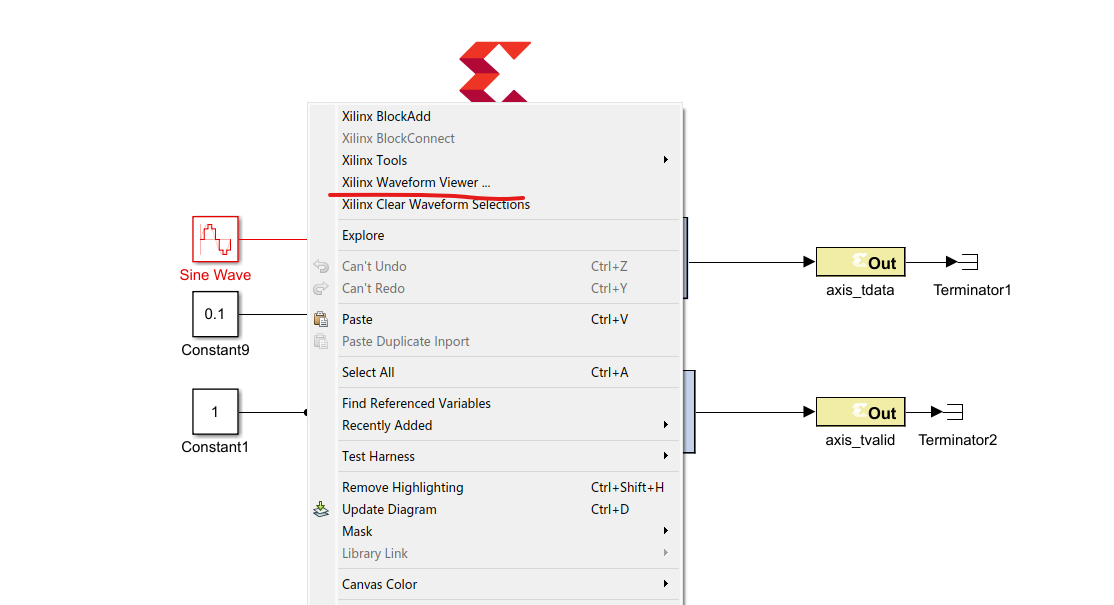

图 1‑9 打开波形查看器 右键添加所需查看的数据

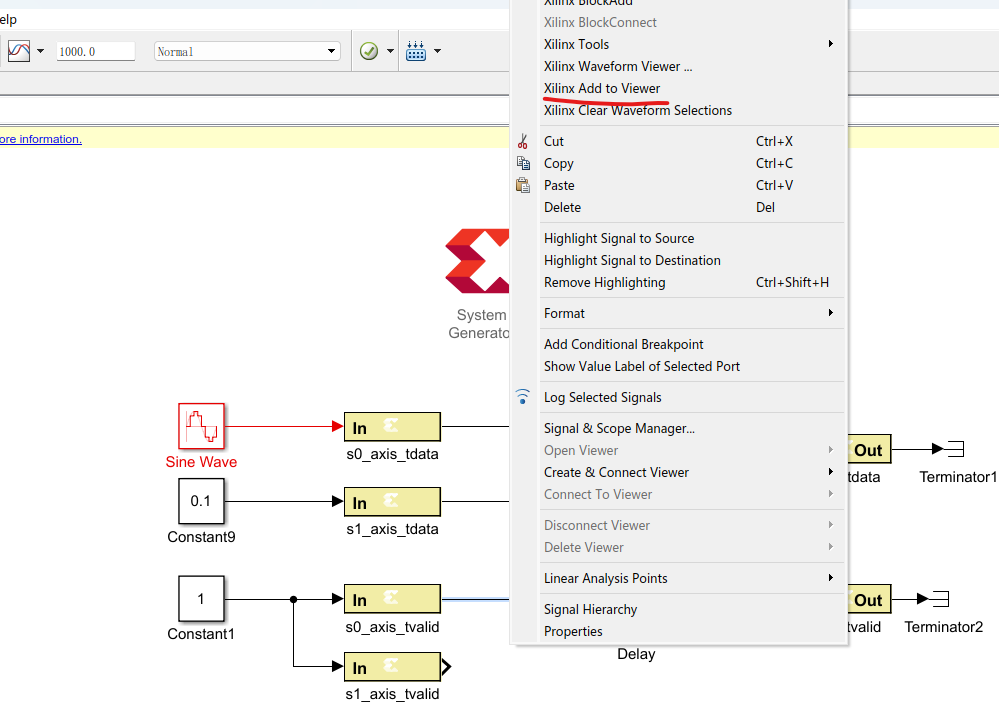

图 1‑10 添加待观测信号到波形查看器

图 1‑11 指定波形长度运行仿真

图 1‑12 仿真波形

输出IP

图 1‑13 双击system generator 生成IP

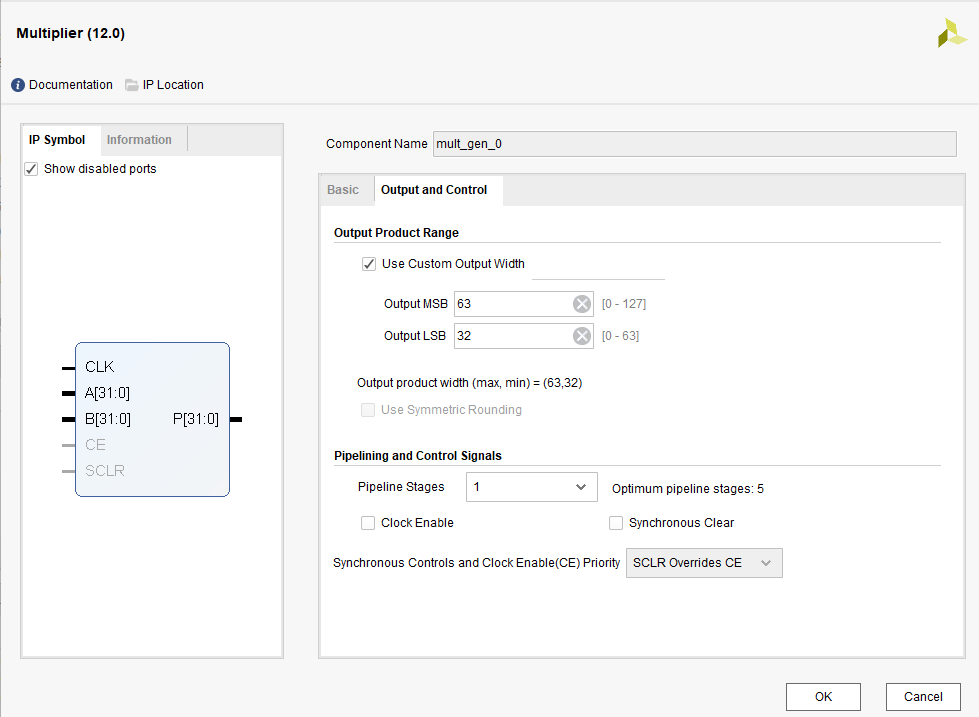

与FPGA资源对比

图 1‑14 FPGA乘法