步骤4:使用约束编辑器

1.在"综合设计"部分下的"流导航器"中单击"编辑定时约束"。

Vivado IDE显示"定时约束"窗口。

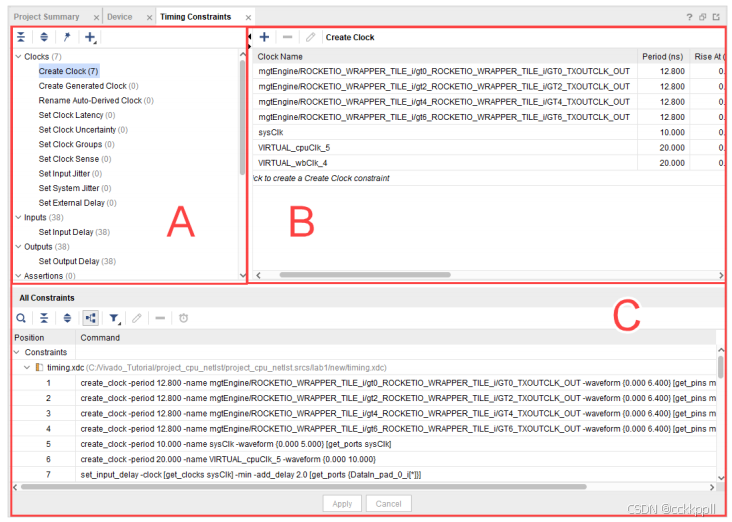

定时约束窗口有三个部分,如上图所示:

•约束树视图:标记为A部分。此部分显示标准计时

约束,按类别分组。双击此部分中的约束会打开一个表单

以帮助您定义所选约束。

•约束电子表格:标记为B部分。此部分显示以下时间约束

当前在"约束"树视图中选择的类型。如果你愿意,你可以用它来

直接定义或编辑约束,而不是使用约束向导。

•所有约束:标记为C节。本节显示了所有时间约束

目前存在于设计中。

定时约束向导可识别丢失的时钟、I/O延迟和时钟域

交叉异常,但它不处理一般的时间异常。您将使用

时序约束编辑器,用于创建此设计中存在的异常。

首先,您将在GTPRESET_IN输入上设置一个假路径。这是输入

通过在"计时"的输入延迟页面上取消选中它而跳过的约束

约束向导。GTPRESET_IN信号是一个异步复位,正确

设计内部同步。有关错误路径的更多信息,请参阅

Vivado设计套件用户指南:使用约束(UG903)。

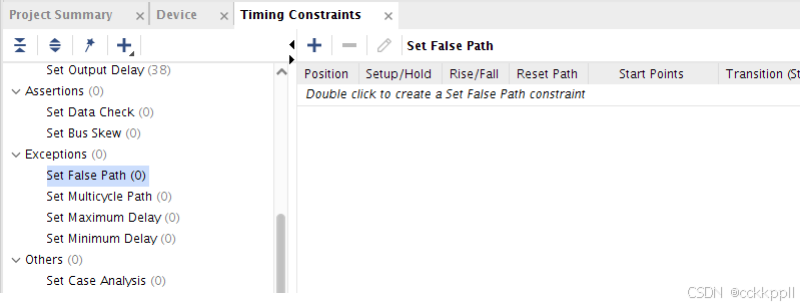

2.在约束树视图中,向下滚动到例外类别,如下所示

图。

3.双击"设置假路径"。

4.在"开始"文本框的右侧,单击"选择起点"按钮。

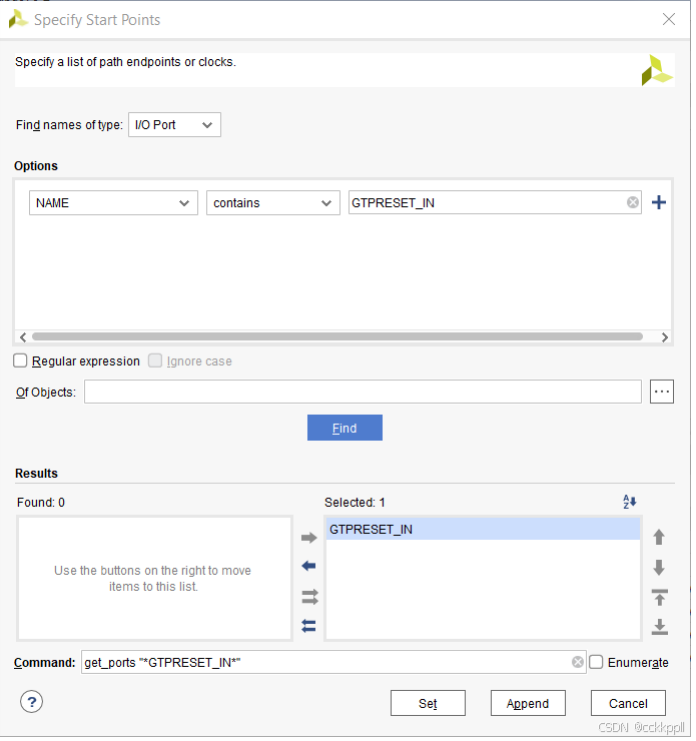

此时会出现"指定起点"对话框。

5.从查找类型名称下拉列表中,选择I/O端口,如下图所示。

6.在"选项"下,选择"名称"、"包含",然后在搜索模式文本框中输入

GTPRESET_IN。

7.单击查找按钮。

8.在查找结果文本框中选择GTPRESET_IN,然后按向右箭头将其移动到

"选定名称"文本框。

提示:您也可以双击GTPRESET_IN,将其从"查找结果"列表移动到"选定"

名单。

请注意,对话框底部显示的"命令"字段会随着您的更改而更改

执行这些不同的操作。get_ports命令更改为:

get_ports "*GTPRESET_IN*"

9.在"指定起点"对话框中单击"设置"。

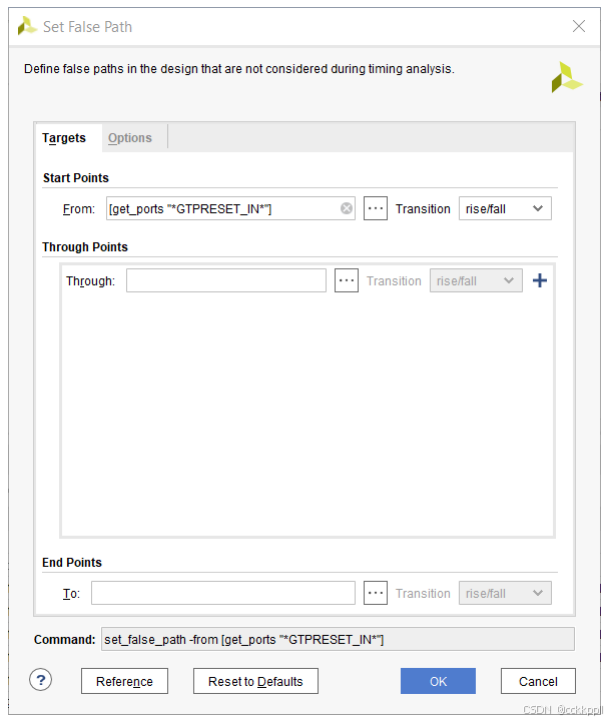

已完成的"设置假路径"对话框如下图所示。请注意

对话框底部"命令"字段中的以下命令文本:

set_false_path-来自[get_ports"*GTPRESET_IN*"]

Vivado IDE显示通过对话框创建的所有约束的Tcl命令形式

你的评论。这对于学习Tcl命令语法和验证最终的

在添加约束之前。

10.单击"确定"关闭"定时约束编辑器"。

Vivado创建了false路径异常。