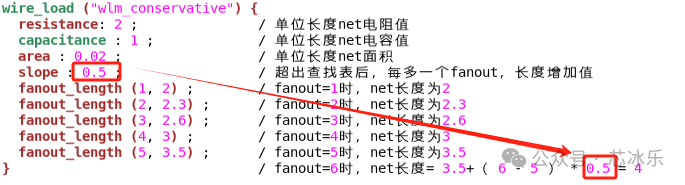

在PR阶段,互连线的延迟可以通过抽取net的rc值计算得到。而在综合阶段,因为没有实际的布局布线,便无法去抽取net上的rc值。那么,线负载模型(wire load model)便派上用场了。

所谓线负载模型,就是根据fanout的数量去估算net的长度,然后根据长度便能估算出net的电阻电容和面积。

那么,根据上述计算方法,假设一个buffer后面drive了5个cell,那么fanout就是5,根据查找表便可以计算得到net长度为3.5,电阻为3.5*2=7,电容为3.5*1=3.5,面积为0.02*3.5=0.07。有了上面的计算值,也便得到了net的RC。

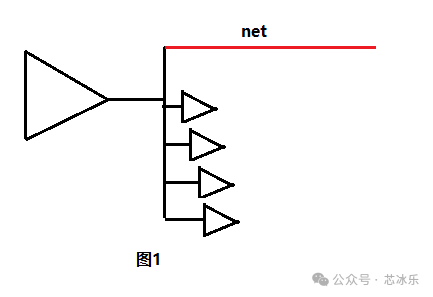

但是,有了net RC依然没法去计算delay。因为,drive cell和被drive cell之间的连接结构会影响着delay大小。一般,互连线的连接结构有以下三种模型,为了方便理解,图中红色的线代表的net其含有RC,黑色的线的R&C为0。

1、 最佳情况树(best-case tree):即drive cell和drived cell距离很近,他们之间没有线电阻,其结构如下图1所示。

2、 平衡树(balanced tree):即drive cell和drived cell之间的net被等分,每个drived cell之前都包含有等分net的RC,如图2所示。

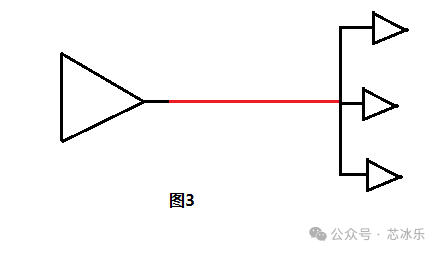

3、 最差情况树(worst-case tree):在这种情况下,drived cell之前包含有整个net的RC,其结构图如图3所示。

因此,选择不同的互连线模型,便会得到不同的delay值。

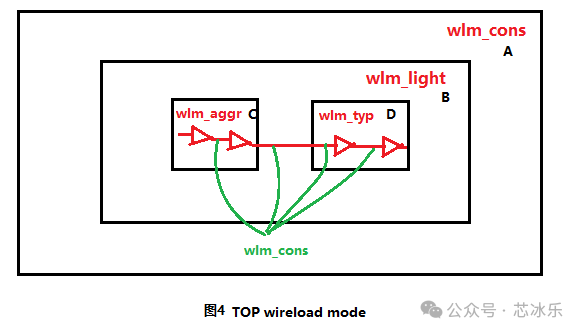

另外,线负载模型也可以指定不同hierarchy下采用不同的wire load model,主要分三种:top、enclosed、segmented,通过set_wire_load_mode来进行设置。

top:该模式下,所有hierarchy下的net都应采用top module下的wire load model,具体如图4所示。

命令如下:set_wire_load_mode top

set_wire_load_model A --name wlm_cons --library lib_stdcell

set_wire_load_model B --name wlm_light --library lib_stdcel

set_wire_load_model C --name wlm_aggr --library lib_stdcel

set_wire_load_model D --name wlm_typ --library lib_stdcel

enclosed:如果此模块完整包含了某个net,那么该net就采用该模块的wire load model,如图5所示。

命令如下:set_wire_load_mode enclosed

set_wire_load_model A --name wlm_cons --library lib_stdcell

set_wire_load_model B --name wlm_light --library lib_stdcel

set_wire_load_model C --name wlm_aggr --library lib_stdcel

set_wire_load_model D --name wlm_typ --library lib_stdcel

segmented: net采用其所在模块的wire load mode,如图6所示。

命令如下:set_wire_load_mode segmented

set_wire_load_model A --name wlm_cons --library lib_stdcell

set_wire_load_model B --name wlm_light --library lib_stdcel

set_wire_load_model C --name wlm_aggr --library lib_stdcel

set_wire_load_model D --name wlm_typ --library lib_stdcel

#小编是一个入行多年的数字后端工程师,本身对编程方面比较感兴趣,在数字后端的脚本、flow上比较擅长,可以为大家提供答疑咨询服务。如有需求,可打开星球芯冰乐,获取更多知识干货分享与答疑服务。