引言

如何快速便捷的完成巨型原型验证系统的组网,并监测系统的连通性及稳定性?

如何将用户设计快速布局映射到参与组网的原型验证系统的每一块 FPGA?

随着用户设计规模的日益增大,传统基于单片 FPGA 或单块电路板的原型验证系统已经远远不能满足用户的设 计验证需求,设计团队常需以灵活组网的方式,将数十甚至上百台原型验证系统"组装"为一个完整的巨型原 型验证系统。鉴于此,以上两个问题成为了亟需解决的问题。

本次思尔芯白皮书《基于组网分割的超大规模设计 FPGA原型验证解决方案》阐述了S2C对客户超大型设计的原型验证,从硬件系统的组建,FPGA 互连组网,外设接口的可扩展性,时钟及复位等 全局信号同步性处理,到基于 RTL 或 netlist 的设计分割算法,系统级静态时序分析,增量式设计分割版本迭代的等新挑战的解决思路。

核心内容

基于组网的人工可干预聚类分割

如何快速完成硬件组网并正确将用户设计分割映射到每一片 FPGA?欢迎下载了解以下内容:

-

硬件组网资源

-

组网拓扑定义

-

基于 RTL 级的聚类分割方案

-

基于 netlist 级的 TDM 模块插入

-

半自动化工具库

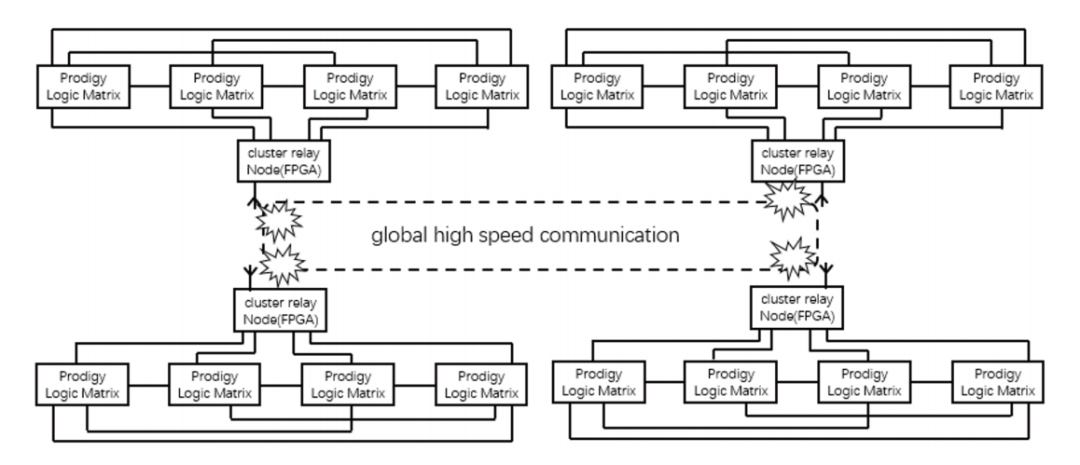

图为常见标准组网

组网聚类分割后的系统静态时序分析与仿真

如何保证分割后设计运行时的稳定性,并优化设计的运行速度?欢迎下载了解以下内容:

-

系统级静态时序分析 SSTA

-

STA的限制和不足

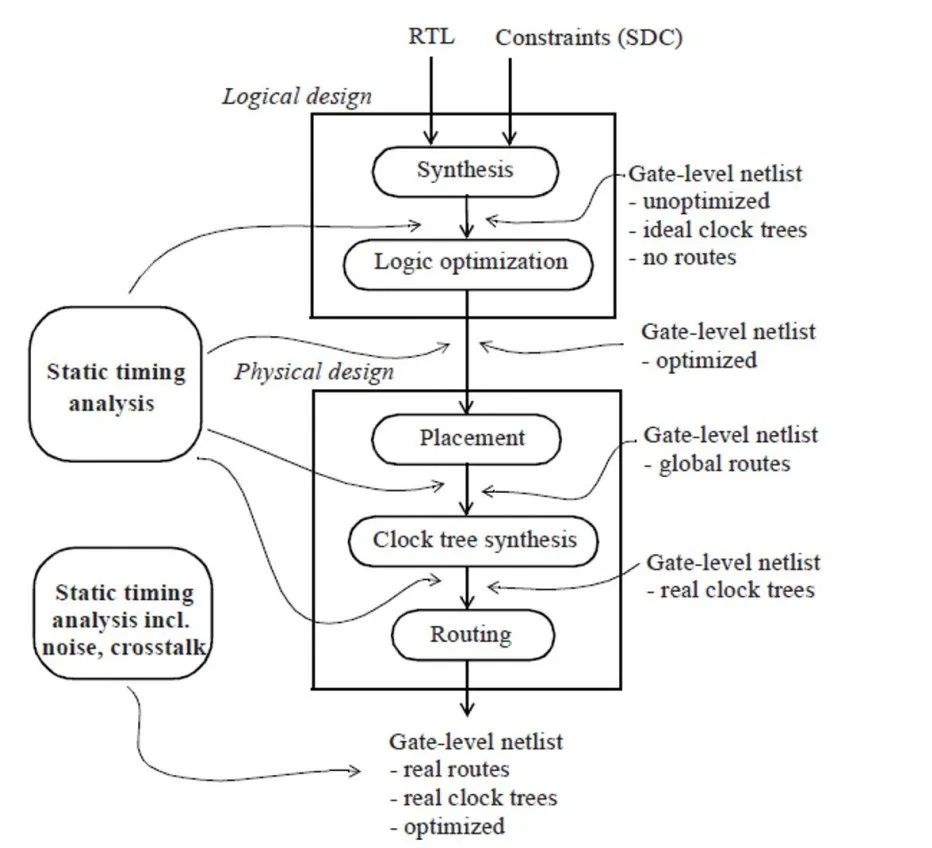

图为数字电路设计中的静态时序分析

站内下载链接:数字芯片设计与验证需要哪些参考资料白皮书?-思尔芯 | S2C

欲了解思尔芯更多信息,请点击:https://www.s2ceda.com