目录

[1 ADC模块标定](#1 ADC模块标定)

[1.1 功能介绍](#1.1 功能介绍)

[1.2 软件程序校准ADC](#1.2 软件程序校准ADC)

[1.2.1 标定步骤](#1.2.1 标定步骤)

[1.2.2 标定时序框图](#1.2.2 标定时序框图)

[1.3 软件程序重新注入校准因子到ADC](#1.3 软件程序重新注入校准因子到ADC)

[1.3.1 标定步骤](#1.3.1 标定步骤)

[1.3.2 更新ADC校准因子](#1.3.2 更新ADC校准因子)

[1.4 用单个ADC转换单端和差分模拟输入](#1.4 用单个ADC转换单端和差分模拟输入)

[1.4.1 标定流程](#1.4.1 标定流程)

[1.4.2 混合单端和差分通道](#1.4.2 混合单端和差分通道)

[2 通道可编程采样时间(SMPR1, SMPR2)](#2 通道可编程采样时间(SMPR1, SMPR2))

[2.1 采样时间介绍](#2.1 采样时间介绍)

[2.2 计算采样时间方法](#2.2 计算采样时间方法)

[2.3 采样约束](#2.3 采样约束)

[2.3.1 对采样时间的约束](#2.3.1 对采样时间的约束)

[2.3.2 灯泡取样模](#2.3.2 灯泡取样模)

[2.3.3 灯泡模式时序图](#2.3.3 灯泡模式时序图)

[3 采样时间控制触发方式](#3 采样时间控制触发方式)

[4 ADC时序](#4 ADC时序)

概述

本文主要介绍STM32G4系列MCU ADC采样标定的功能,包括功能介绍,标定ADC模块的类型,标定步骤,还介绍了ADC采样时间的相关内容。

1 ADC模块标定

1.1 功能介绍

每个ADC提供一个自动校准程序,驱动所有校准 序列,包括ADC的上/下电序列。在此过程中,ADC 计算一个校准因子,该因子为7位宽,并在ADC内部应用于 ,直到下一次ADC断电。在校准过程中,应用程序不得使用 ADC,必须等待校准完成。

校准是任何ADC操作的基础。它消除了可能因工艺或带隙变化而从芯片到芯片变化 的偏移误差。

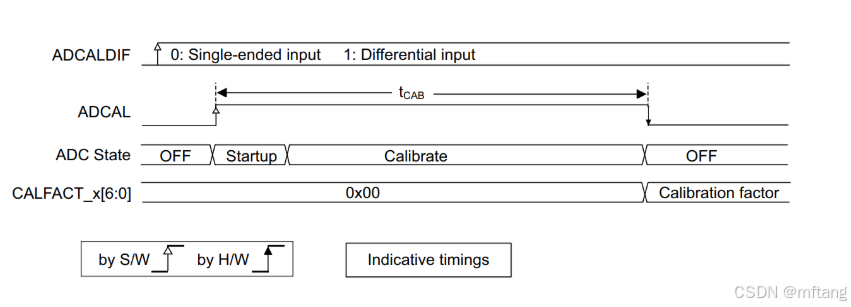

用于单端输入转换的校准因子与用于差分输入转换的 因子不同:

1) 在启动要应用于单端输入转换的校准之前,写入ADCALDIF = 0。

2) 在启动要应用于差分输入转换的校准之前,写入ADCALDIF = 1。

然后通过设置位ADCAL = 1由软件启动校准。校准只能在禁用ADC (ADEN = 0)时 启动,在所有 校准序列中ADCAL位保持为1。然后,一旦校准完成,硬件就会清除它。在 这个时候,相关的校准因子存储在模拟ADC内部,也存储在 位CALFACT_S[6:0]或CALFACT_D[6:0]的ADC_CALFACT寄存器(取决于 单端或差分输入校准)

如果禁用ADC (ADEN = 0),则保留内部模拟校准。但是,如果 ADC长时间禁用,则建议在重新启用ADC之前运行一个新的校准周期 。

每次拔掉ADC的电源(例如,当产品进入待机或VBAT模式时, )都会丢失内部模拟校准。在这种情况下,为了避免花费时间 重新校准ADC,可以在不重新校准的情况下将校准因子重新写入ADC_CALFACT 寄存器中,假设软件先前已保存了先前校准期间提供的 校准因子。

如果ADC开启但未转换(ADEN = 1, ADSTART = 0, JADSTART = 0),则可以写入校准因子,然后在下一次转换开始时,将校准因子 自动注入模拟ADC。这种加载是透明的,不会 在转换开始时增加任何周期延迟。当VREF+电压变化超过10%时,建议重新校准 。

1.2 软件程序校准ADC

1.2.1 标定步骤

1) 确保DEEPPWD = 0, ADVREGEN = 1,并且ADC稳压器启动时间已经过去。

2) 确保ADEN = 0。

3) 通过设置ADCALDIF = 0(单端输入)或ADCALDIF = 1(差分输入)来选择此校准的输入模式。

4) 设置ADCAL。

5) 等待直到ADCAL = 0。

6)校准因子可以从ADC_CALFACT寄存器中读取。

1.2.2 标定时序框图

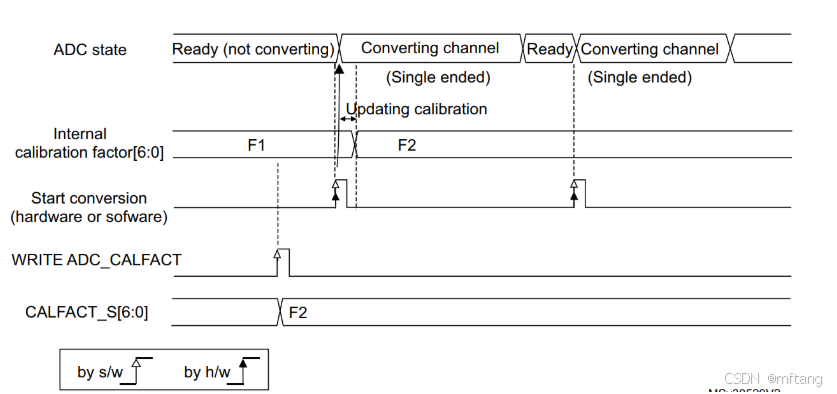

1.3 软件程序重新注入校准因子到ADC

1.3.1 标定步骤

-

确保ADEN = 1, ADSTART = 0和JADSTART = 0(启用ADC并且没有 转换正在进行)。

-

用新的校准因子编写CALFACT_S和CALFACT_D。

-

当转换启动时,只有当内部模拟校准因子与存储在单端输入通道 CALFACT_S或差分输入 通道CALFACT_D位中的校准因子不同时,才会将校准因子注入模拟ADC 。

1.3.2 更新ADC校准因子

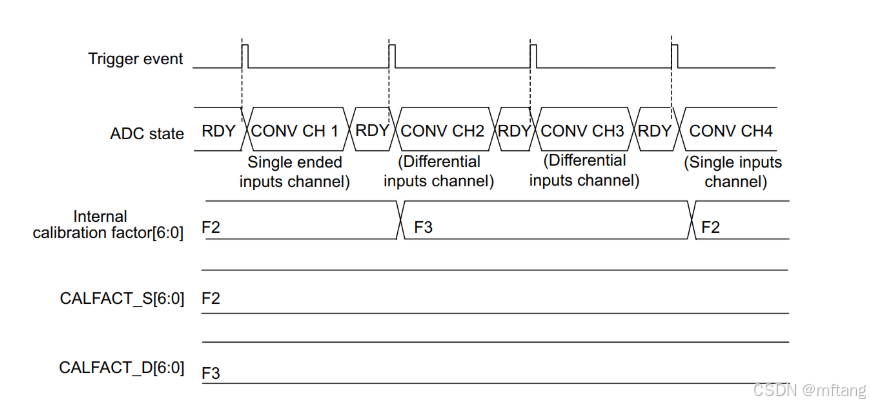

1.4 用单个ADC转换单端和差分模拟输入

1.4.1 标定流程

如果ADC要转换差分和单端输入,则必须执行两次校准 ,一次是ADCALDIF = 0,另一次是ADCALDIF = 1。步骤如下 :

1) 关闭ADC

2) 在单端输入模式下校准ADC (ADCALDIF = 0)。这将更新 寄存器CALFACT_S[6:0]。

3) 在差分输入模式下校准ADC (ADCALDIF = 1)。这将更新 寄存器CALFACT_D[6:0]。

4) 启用ADC,配置通道并启动转换。每次 从单端到差分输入通道切换(反之亦然)时, 校准会自动注入模拟ADC。

1.4.2 混合单端和差分通道

2 通道可编程采样时间(SMPR1, SMPR2)

2.1 采样时间介绍

在开始转换之前,ADC必须在被测电压源 和ADC的嵌入式采样电容之间建立直接连接。这个 采样时间必须足以使输入电压源将嵌入式 电容器充电到输入电压水平。

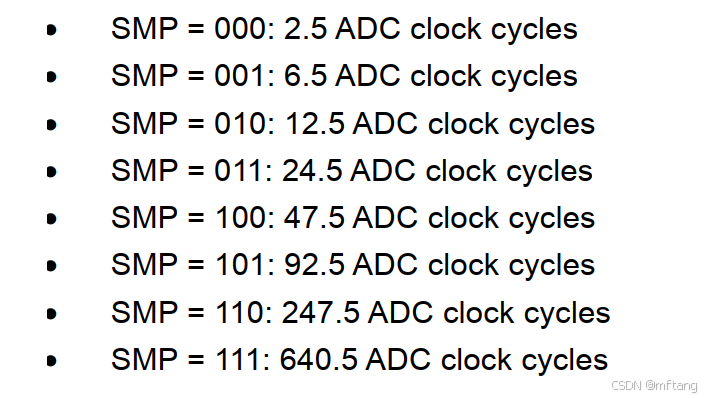

每个通道可以用不同的采样时间进行采样,这是可编程的,使用 ADC_SMPR1和ADC寄存器中的SMP[2:0]位。因此,可以在以下采样时间值中选择 :

总转换时间计算如下:

2.2 计算采样时间方法

一个实例:

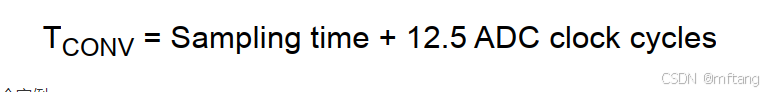

如果采样时间配置为: 2.5 ADC clock cycles ,ADC的模块的工作频率为30M Hz,其总体的采样时间为:T= (2.5 + 12.5) ADC clock cycles = 15 ADC clock cycles

换算为时间:

ADC通过设置状态位EOSMP(仅用于 常规转换)来通知采样阶段的结束。

2.3 采样约束

2.3.1 对采样时间的约束

对于每个通道,必须对SMP[2:0]位进行编程,使其符合数据手册中ADC特性部分规定的最小采样时间

2.3.2 灯泡取样模

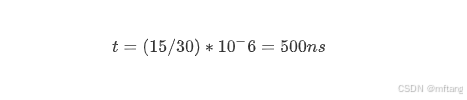

当在ADC寄存器中设置BULB位时,采样周期在 最后一次ADC转换后立即开始。在ADC_SMPR1寄存器中编程采样 时间后,硬件或软件触发器开始转换。在 启用ADC后,执行第一次ADC转换,并以SMP位编程采样时间。灯泡 模式从第二次转换开始生效。

最大采样时间是有限的(参考 数据表的ADC特性部分)

灯泡模式既不兼容连续转换模式,也不兼容 注入通道转换。

当设置了BULB位时,ADC_CFGR2中不允许设置SMPTRIG位。

2.3.3 灯泡模式时序图

3 采样时间控制触发方式

当设置SMPTRIG位时,通过SMPx位编程的采样时间不适用 。采样时间由触发信号边缘控制。

当选择硬件触发器时,触发信号的每个上升沿开始 采样周期。下降沿结束采样周期并开始转换。 EXTEN[1:0]位必须设置为01。没有定义上升和下降 边的硬件触发器(一个脉冲事件)不能在灯泡模式下使用。

当选择软件触发器时,软件触发器不是ADC_CR 中的ADSTART位,而是SWTRIG位。必须设置SWTRIG位才能开始采样周期,必须清除 SWTRIG位才能结束采样周期并开始转换。EXTEN[1:0]位必须设置为00。

最大采样时间是有限的(参考 数据表的ADC特性部分)。

该模式既不兼容连续转换模式,也不兼容注入 通道转换。

设置SMPTRIG bit时,不允许设置BULB bit。

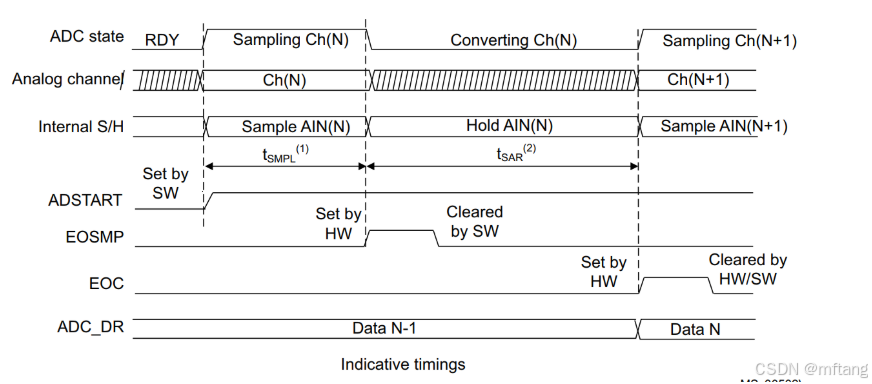

4 ADC时序

转换开始和转换结束之间所经过的时间是 配置的采样时间加上取决于数据分辨率的连续近似时间的总和:

模数转换时间: