如约介绍源码构建 Infinite-ISP 项目,其实大家等的是源码,所以中间过程简洁略过,可以直接翻到文末获取链接。

构建工程

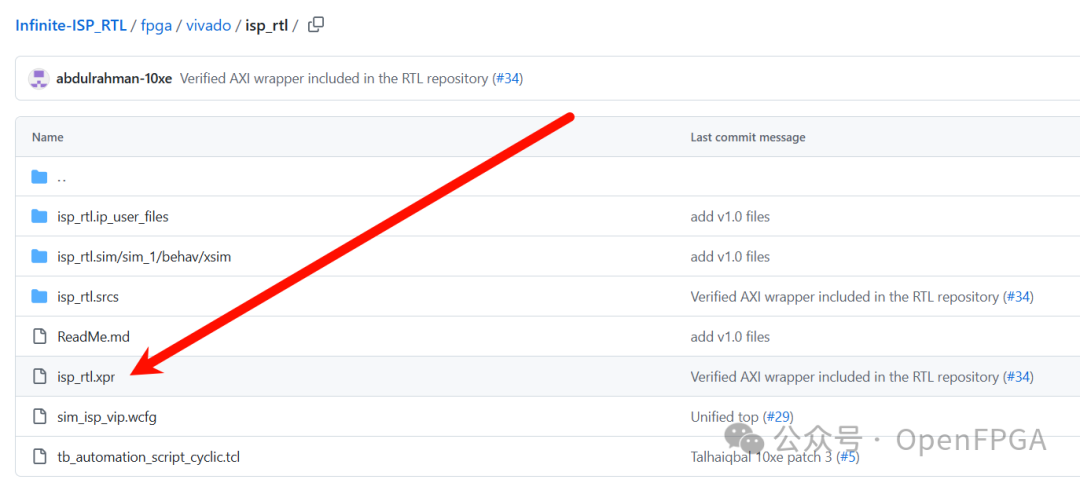

第一步,从文末或者下面链接获取源码

第二步,直接打开工程即可

再介绍以下配置:

-

Vivado版本:2024.1

-

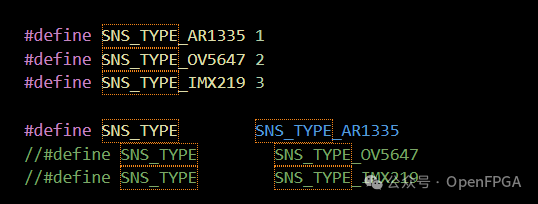

Sensor:Onsemi AR1335 或者 Omnivision OV5647 或者 Sony IMX219

不同版本的驱动需要再Vitis里进行设置:

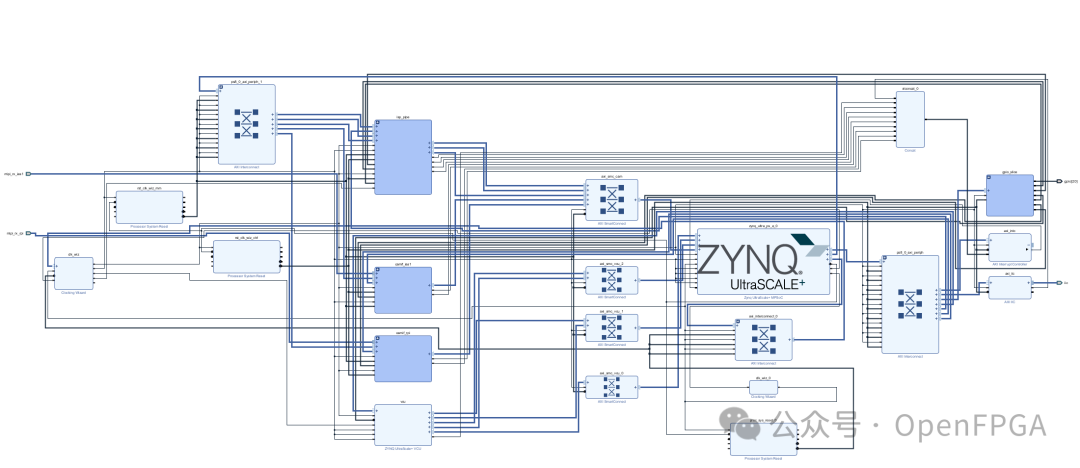

整个数据流比较简单,从MIPI输入RAW数据,通过DDR缓存后进入ISP进行数据处理,处理好的数据进行DDR进行后续显示或者编解码输出。

源码

源码来源:

通过百度网盘分享的文件:Infinite-ISP 链接:https://pan.baidu.com/s/1u5wY25ciIxWogeKqKmHlMQ?pwd=open

后续工程更新及最新版本文件以GITHUB为主,本链接失效或者工程变动不在更新~

总结

本篇文章内容没什么东西,这里说一下这个开源项目,这个开源项目其实是在之前《优秀的 Verilog/FPGA开源项目介绍(二十六)- ISP (图像信号处理)》文章中介绍的几个项目的基础上发展而来,这就是开源的魅力,减少了很多不必要的工作量。

本工程因为要测试ISP的工作流程,所以略显臃肿,后续我们将以ZYNQ7020+OV5647为硬件基础,简化工程后再进行详细的设计,包括每个IP的设计及算法介绍。