SZ901最高支持JTAG 53MHz的时钟频率,下载bit文件和固化程序的速度提升非常明显。

首先设置参数

1,将JTAG0 分频系数修改为3

2,设置参数,更新参数。(完成)

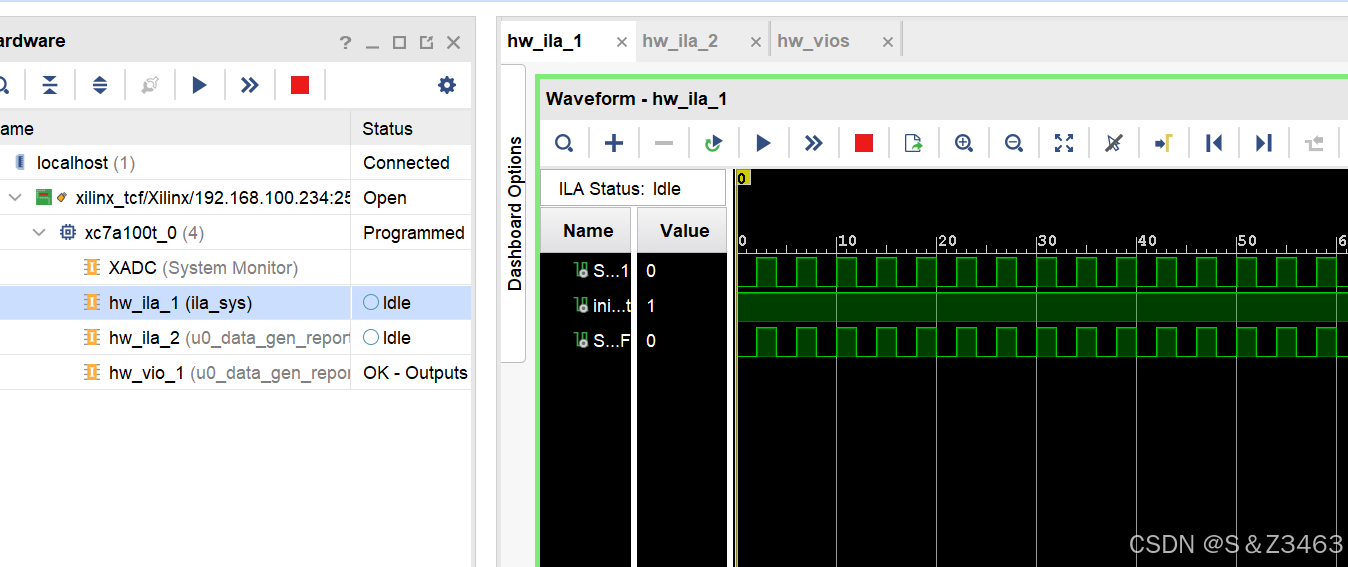

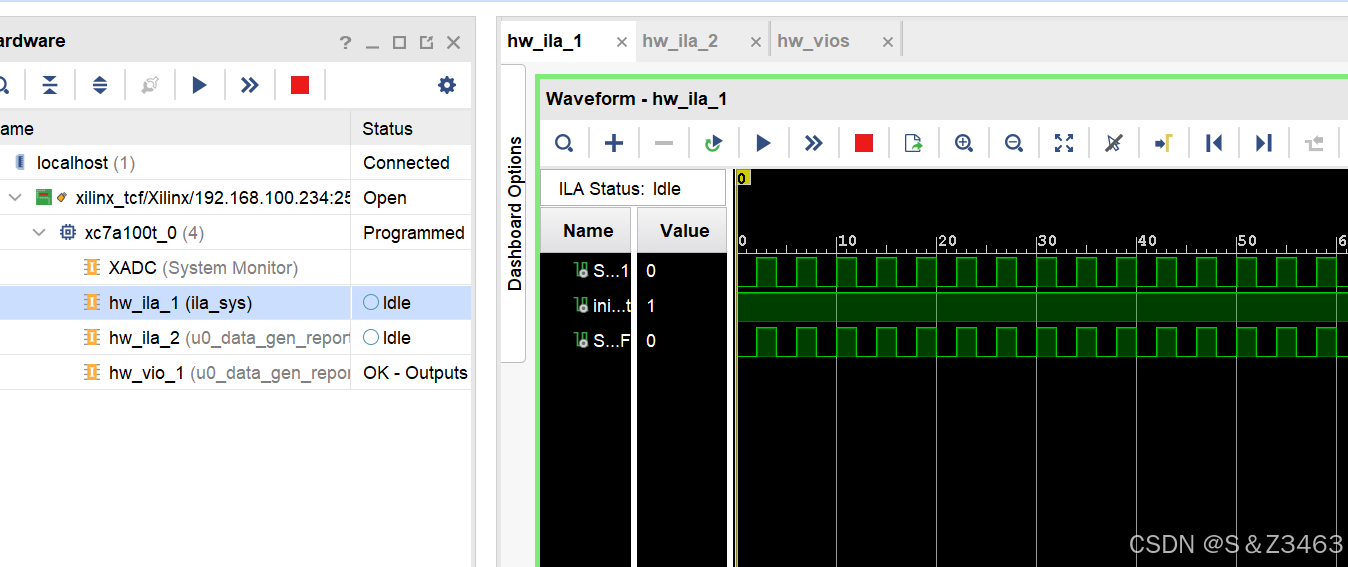

打开VIVADO

VIVADO 正常识别FPGA,速度高达52.6M。

下载bit文件

fpga 正常工作

注意哦,JTAG速度很快,ila的时钟不要太慢哦。

SZ901 已上架淘宝,搜素"SZ901"哦

SZ901最高支持JTAG 53MHz的时钟频率,下载bit文件和固化程序的速度提升非常明显。

首先设置参数

1,将JTAG0 分频系数修改为3

2,设置参数,更新参数。(完成)

打开VIVADO

VIVADO 正常识别FPGA,速度高达52.6M。

下载bit文件

fpga 正常工作

注意哦,JTAG速度很快,ila的时钟不要太慢哦。

SZ901 已上架淘宝,搜素"SZ901"哦