在使用mcu+cpld联合编程之前,请确认已经熟练掌握mcu的使用方法,并且对cpld编程(verilog语言)有一定的基础。

另外,对AHB总线也需要有一定的了解。

这个章节分为两部分:

第一部分,展示联合编程中各种概念和操作流程;

第二部分,从具体案例出发,由浅到深来描述各种常用的编程技巧。

.

以下描述为第一部分(概念和流程)。如要查看实例讲解,请参考第二部分。

.

一、前述

在AG32芯片(所有型号)中,都有内嵌2K的逻辑门,可供fpga/cpld来使用。

也就是说,使用AG32的芯片时,有三种选择:

- 只使用mcu部分;

- 只使用cpld部分;

- 同时使用mcu和cpld(即:mcu和cpld联合编程);

如果:

用于1(仅用做mcu),不必关注此文档。

用于2(仅用做cpld),硬件设计和操作流程,请跳转到"纯粹cpld编程",也不必关注此文档。

用于3(mcu和cpld联合编程):请按照该文档的描述,先完整走一个流程。

.

二、基础了解

- AG32整颗芯片包含两部分:mcu和cpld。

这两部分是相互独立的(各自编译、各自下载),但又可以相互连通起来(信号连通)。

芯片要把这两部分的bin都烧录进去,才能运行起来。

- mcu和cpld到外部Pin脚的连通,是通过VE文件来配置的。

跟ST芯片每个Gpio对应某个固定Pin脚不同,在AG32中,所有的Gpio/大部分的外设,对外引脚并不是定死的。而是需要在VE文件中指定对应。

VE中,除了配置Gpio到Pin的关联,还可以配置mcu到cpld之间的信号关联。

- Mcu+cpld联合编程时,cpld工程是由vscode的"prepare LOGIC"命令自动生成的。

注意:联合编程时,cpld工程不能手工通过supra建立。

cpld的对外接口,也是依托于vscode工程来的,不再是孤立的。

cpld中的top module的信号输入,是关联到mcu工程的(由VE配置出来)。

- cpld在联合编程中的定位:

整颗芯片运行时,需要两个bin:mcu的bin和cpld的bin。

如果芯片中只使用mcu不使用cpld:

此时,VE文件里只配置mcu用到的Pin脚即可。

这种情况下,vscode工程中点"upload LOGIC"时,会自动生成默认logic(该logic中"用户逻辑"为空而已),并编译出bin并烧录。

整个过程中,logic部分对开发者来说是无感的。

如果芯片中同时使用mcu和cpld:

那么要把工程配置成"自定义logic"。

此时VE文件里需要配置用到的mcu和pin之间、mcu和cpld之间、cpld和pin之间,三种情况下的信号关联。

这种情况下,VSCode下点"prepare LOGIC"按钮,会为开发者生成cpld的框架工程。**开发者需要在这个框架下完成cpld逻辑的编写。**这个编写调试中,开发者持有主动权。等全部开发完成,并编译出bin,烧录就又回到VSCode去烧录。

这个过程,除了logic需要用户自己编写编译外,从更外层的视角看,整个流程还是跟"默认Logic"是相同的。

.

三、安装软件

mcu需要使用到的VSCode前边已经安装过了。

fpga/cpld需要使用Supra和Altera Quartus II两个软件来编程。

其中:

Supra.exe软件在安装完SDK后,已经在SDK路径下了,可直接使用(无需额外安装Supra)。

(注:如果在SDK路径下没有找到Supra.exe,可进入安装路径\AgRV_pio\packages\tool-agrv_logic\bin\去找到。同时建议手工新建一个快捷方式到SDK路径下以方便后续使用)

Altera Quartus II软件需要用户自行安装,安装后再安装对应的器件库。

(注意:Quartus不能使用Lite版本,需要使用Full版本。最好使用版本:Quartus II 64-Bit Version 13.0.1 Build 232 06/12/2013 SJ Full Version)

在这两个软件中,

Quartus工具用来编写vlog代码并导出vo文件,Supra工具使用vo文件来生成最终的bin。

.

四、CPLD使用流程

从使用角度来说,整体需要4个步骤:

- 1.在VE文件里配置引脚关系;

- 2.建立cpld空工程(使用prepare LOGIC命令)并编写逻辑;

- 3.Quartus下进行工程转换(和综合);

- 4.Supra下编译出最终的logic.bin;

下边进入详细描述。

1.在VE里定义引脚和信号关系

这部分和MCU使用是相仿的。

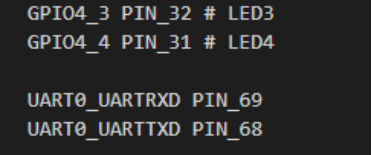

在mcu里,都是mcu信号直接到PIN脚的映射。比如:

那么,在使用cpld里,除了上述的**"mcu信号到Pin脚"** 关联外,还允许**"mcu信号到cpld信号"** 和**"cpld信号到Pin脚"**的两种关联。这里描述的三种关联,是常见的三种信号关联方式。详细使用方法,后续会介绍。

这里需要知道的是,每次VE文件修改完以后,都要重新走一遍整个流程(从prepare LOGIC开始)。

其实不光修改完VE需要重新走一遍流程,有时修改platformio.ini也需要重新走一遍流程(比如,修改管脚数量)。

如果是第一次试验example例程,可以不用修改,使用默认的VE文件即可。

2.生成空的cpld工程

仍然以example(路径:...\AgRV_pio\platforms\AgRV\examples\example)为例建立工程。

在example样例程序中,默认是没有打开自定义ip的。

首先,要通过配置打开自定义ip

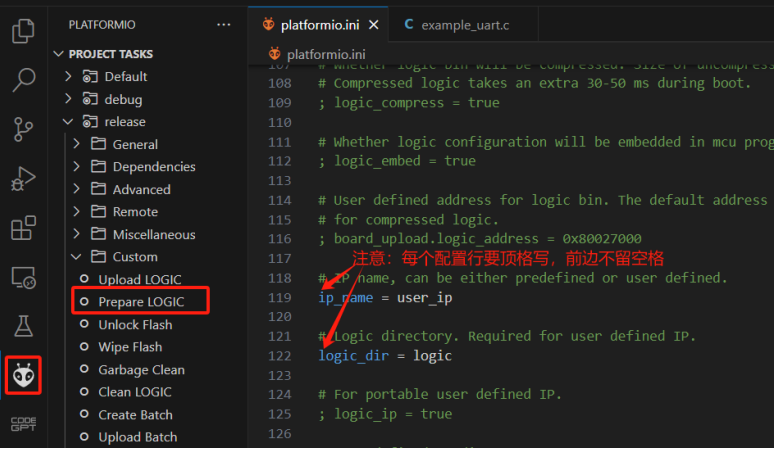

方法:在platformio.ini中打开以下两项:

ip_name = analog_ip

logic_dir = logic

注意:这两行去掉注释的时候,前边不要留空格。要顶格写。

打开以上两项并保存文件后,才能在左边栏看到创建logic框架工程的选项(prepare LOGIC):

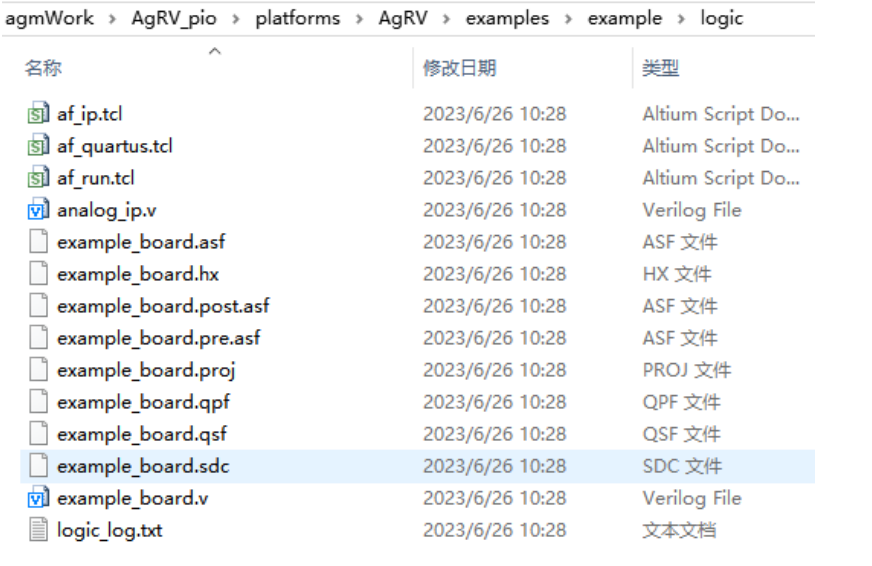

点击该功能【Prepare LOGIC】后,可以看到在example工程目录下生成一个logic文件夹,自动生成的文件如下图:

这里生成的logic文件夹,就是空的cpld工程。也是后续编写cpld的模板工程(后续代码在这个基础上添加)。

关于改写文件名:

这里的文件名字,是根据platformio.ini里边的配置项来的:

board_logic.ve = example_board.ve

ip_name = analog_ip

logic_dir = logic

如果想改文件名字,可先在platformio.ini中更改名字,更改后再点生成按钮来自动生成。可更改的名字,就是上边的三项:

board_logic.ve 对应logic文件夹内example_board.v的名字

Ip_name 对应logic文件夹内analog_ip.v的名字

Logic_dir 对应文件夹logic的文件夹名字

在生成后的文件夹内,注意其中的两个.v文件:analog_ip.v和example_board.v。

这两个文件是vlog的源码文件。

其中:

analog_ip.v是一份空的模板,用户自己要实现的功能,就在这个空模板上展开;这个空的模板里边,主要就是module analog_ip的接口定义。

example_board.v是根据工程中example_board.ve里的pin配置,Logic prepare时自动转换出来的v源码,也是supra工程的top module。这部分不要手工改动。

到这里,cpld空工程建立完毕。

注意:

后期修改完VE的配置后,Prepare LOGIC时,会重新生成 cpld工程模板,这个模板文件都仍然存到logic文件夹下,且仍然是这两个.v文件。

只不过analog_ip.v对应新增出analog_ip_tmpl.v文件,而example_board.v则是直接覆盖。

由于analog_ip.v是用户程序的入口,用户程序会从这里开始写。这个文件一定是会修改的。所以,每次prepare LOGIC时,这个文件会对应生成 analog_ip_tmpl.v文件,而不是覆盖。

生成出analog_ip_tmpl.v后,用户要根据自己的情况,把新接口手动合并到analog_ip.v去。

注:这里只是以example来举例。实际应用中,在导出空工程前,需要先配置好platformio.ini的其他项和example_board.ve所需要的引脚。包括:board_logic.device配置32/48/64/100脚。也就是第一步要做的内容。

3. Quartus下进行工程转换

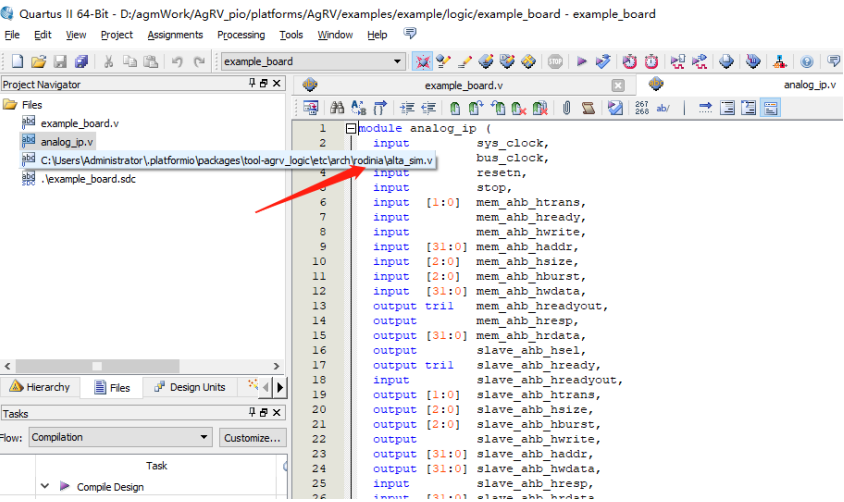

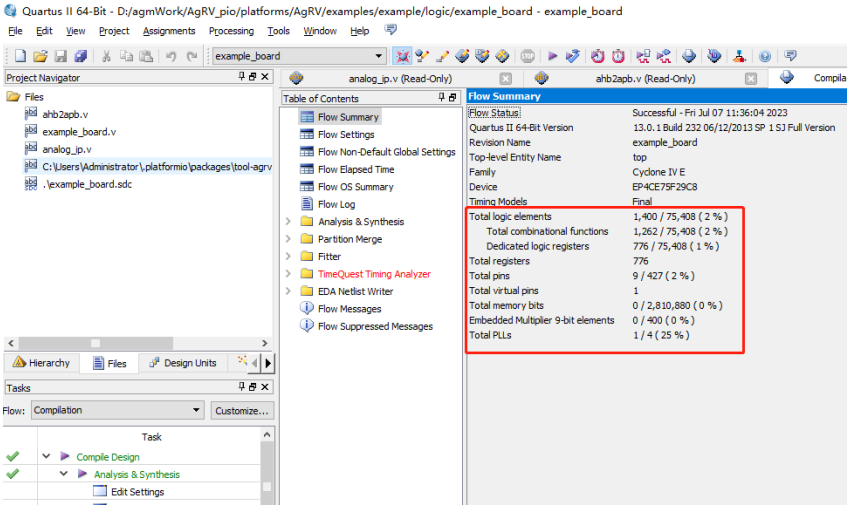

使用前边安装过的Quartus II软件,打开\example\logic\的工程文件。打开后如图:

这里除了example_board.v和analog_ip.v外,还有个系统的alta_sim.v,这个文件是提供芯片系统的功能,类似函数库,可不用关注。

此时,这个工程是个空的工程,用户要根据需求在analog_ip.v中实现功能。

再次回顾下3个.v文件:

- analog_ip.v:用户自定义logic的入口。用户logic实现在这里展开;

- example_board.v:整个logic的top module。会关联analog_ip的module和atla_sim下的各module。不要修改该文件。

- alta_sim.v:封装过的跟AG32相关的各module。不要修改该文件。

接下来进行空工程的转换和编译。

注意:如果不是很熟练,这里的空工程最好不要马上添加自己的代码。而是应该首先工程转换。

工程转换的目的,是把cpld模板工程真正转换成quartus实际运行的状态。

操作步骤:

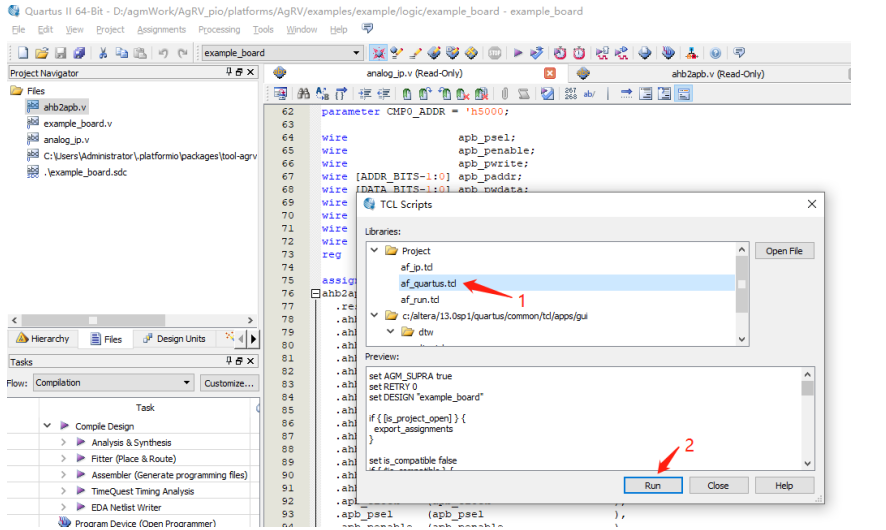

打开Quartus的tools->TCL Scripts,如下图所示:

【Run】运行成功后,可以看到该logic占用的资源数量。

这个转换的过程,顺便进行了cpld工程的编译。

上图中斜杠前边标识的大小就是所占的逻辑单元数(后续使用中逻辑单元不能超过2K,严格讲,是2112个逻辑单元)

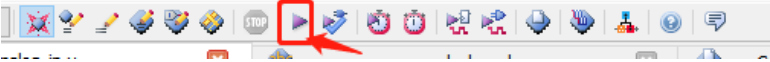

注意:第一次导入工程,必须执行上图的方式来转换。后续编写和修改cpld代码后,可以仍然执行上图方式,也可以直接点下图的"编译"按钮来编译。

执行到这里,会在logic下生成vo文件出来(在\logic\simulation\modelsim下)。

如果用户有自己的逻辑,可以在这时,把逻辑加入到analog_ip.v中去,并点上图的三角号重新编译。

到这里,Quartus工具的任务也完成了。

接下来打开Supra来继续生成bin文件。

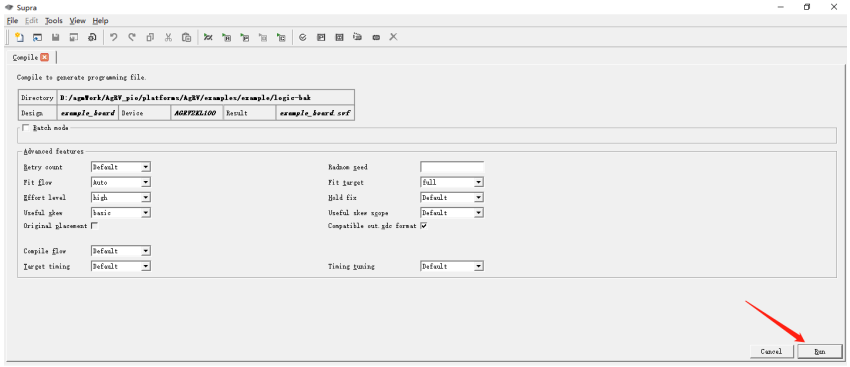

4.Supra下编译出最终的bin

在Supra工具里,打开该工程(\example\logic\)。

然后,点击【左上角Tool】->【Compile】,在弹出的画面中点右下角的【run】。

编译成功后,画面会有提示。

Compile design example_board done with code 0

然后在logic路径下可以看到新编译出来的bin。

这个bin就是要烧录到芯片的cpld.bin。

到这里,supra工具的任务完成。

.

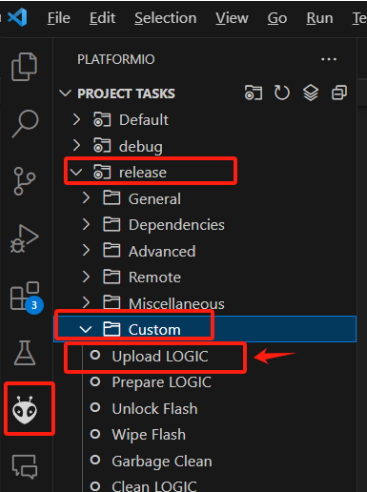

至于烧录,重新回到VSCode下烧录logic即可。如下图:

到这里,新建一个空工程、转换、编译、烧录的整个流程描述完毕。

强调:

后续如果在VE里修改过配置,则需要走一个全过程:vscode下prepare LOGIC再生成一遍cpld模板、合并analog_ip_tmpl.v到analog_ip.v中去、启动quartus去转换、supra下编译,回到vscode下烧录logic。

后续如果只是在quartus下编写cpld代码,需要走的几步:quartus下编译、supra下编译、回到vscode下烧录logic。

.

五、上述过程中的说明

上述流程中涉及两个比较关键的点:

1. 自定义模块的命名

自定义的逻辑,自定义文件名必须与自定义模块名相同,就是在platformio.ini中设置的ip_name的名字。

这个对应关系,在上述流程点prepare LOGIC自动生成代码时,会自动完成。

如果是手工编辑的逻辑代码,或者对这里的命名进行过改动,会出现后续Quartus中使用的异常。

2. Ve中定义的信号关联

在AG32中,mcu和cpld和外部引脚,三者是相互独立的。

- mcu用的IO,在ve里,可以关联到外部引脚Pin_xx;

- cpld用的IO,在ve里,可以关联到外部引脚pin_xx;

- mcu的某一路信号又可以直接和cpld的某一路信号,在ve里,关联起来;

所以,ve是很关键的一个桥梁。

在ve中定义好以后,运行prepare LOGIC会自动产生cpld的顶层模块的输入输出接口,这些接口就是cpld和mcu与外部引脚关联的信号通路。

这里着重描述下3种情况在VE文件里的定义。

A. mcu和外部引脚的关联

比如,定义gpio到外部引脚:GPIO4_3 PIN_32

比如,定义串口0到外部引脚:UART0_UARTRXD PIN_31

定义格式为:mcu的FunctionName + 空格 + Pin脚ID 。

这部分在 mcu 使用里描述的很多了,不再赘述。

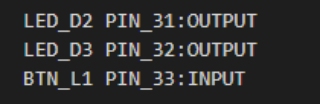

B. cpld和外部引脚的关联

比如,定义led到外部引脚:LED_D3 PIN_32:OUTPUT

定义格式为:cpld信号名称 + 空格 + Pin脚ID:方向

其中,

cpld 信号名称,是自定义名称,这个名称随后可以在 cpld 中引用;

方向,有 3 种:OUTPUT、INPUT 和 INOUT(这个方向是 cpld 对外部引脚来说的)。

方向是可选的,可加可不加。如果不加,则是默认的 INOUT(双向)。

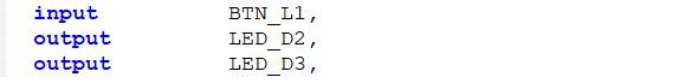

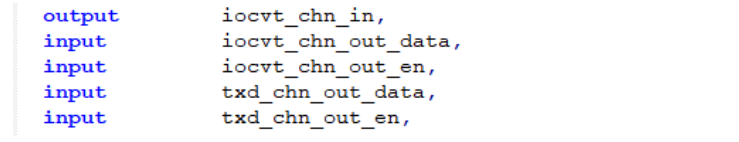

上述定义在 ve 里添加后,执行 prepare LOGIC 命令,在自动生成的 cpld 工程中,可以看到输出到 cpld 顶层模块接口中的 item 如下:

那么,

input BTN_L1 : 是 pin 到 cpld 的信号;

output LED_D2 : 是 cpld 到 pin 的信号;

output LED_D3 : 是 cpld 到 pin 的信号;

然后在 cpld 代码中操作 LED_D3 这个信号的高低,最终操作的 PIN_32 管脚的高低。

(注:VE 里每行最后定义的方向是可选的)

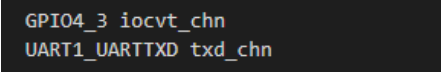

C. mcu和cpld之间的关联

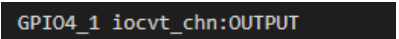

比如,定义 gpio 信号到 cpld:GPIO4_1 iocvt_chn

比如,定义串口 1 的 tx 信号到 cpld:UART1_UARTTXD txd_chn

定义格式为:MCU的FunctionName + 空格 + cpld信号名称

其中,

这里的 FunctionName,同 1 中的 FunctionName,就是 mcu 里的通路定义。更多定义参考《AGRV2K_逻辑设置.pdf》,里边有全部的 mcu 端可用的 FunctionName 列表。

除了 mcu 的 FunctionName(映射到引脚)外,mcu 对 cpld 还开放出更多的内核级通路接口,如:mem_ahb_各通道,dma 各通道,mcu 的 reset 和 stop 等信号,具体定义也参考《AGRV2K_逻辑设置.pdf》。

这里定义后,执行 prepare LOGIC 命令,在自动生成的 cpld 工程中,可以看到输出到cpld顶层模块接口的 item 如下:

对于 iocvt_chn 来说,对应的是没有指定方向的普通 gpio(GPIO4_3)口,则这里生成的信号同时包含有输入 和输出 两种。

注:这里的输入和输出,是相对于 cpld 端来说的。蓝色的 input/output,就是该信号的方向。比如:

output iocvt_chn_in:是 cpld 输出到 mcu 的信号;

input iocvt_chn_out_data:是 mcu 输出到 cpld 的信号;

input iocvt_chn_out_en:是 mcu 输出到 cpld 的信号(en 信号很少用,一般可忽略);

对于 txd_chn 来说,由于 mcu 的串口 TX 是定义好方向的,是 mcu 的 output 方向。所以在 cpld 里只有两个 item 项:

input txd_chn_out_data:是 mcu 输出到 cpld 的信号;

input txd_chn_out_en:是 mcu 输出到 cpld 的信号(en 信号很少用,一般可忽略);

如果对普通 GPIO 也设置了方向,则导出到 cpld 的方向也就只有对应方向的信号了。

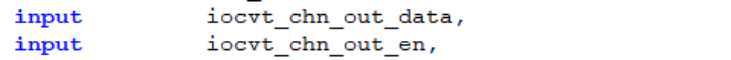

如:VE 里设置 GPIO4_1 iocvt_chn 为 mcu 的输出:

则prepare LOGIC后生成的item只有input的两项。如下:

注意:在mcu和cpld信号连接中,mcu的output就是cpld的input。

.

到这里,第一部分(mcu+cpld使用的概念和流程)描述完毕。

下个章节,第二部分,将以样例为基础,描述mcu+cpld在具体使用中怎么体现。