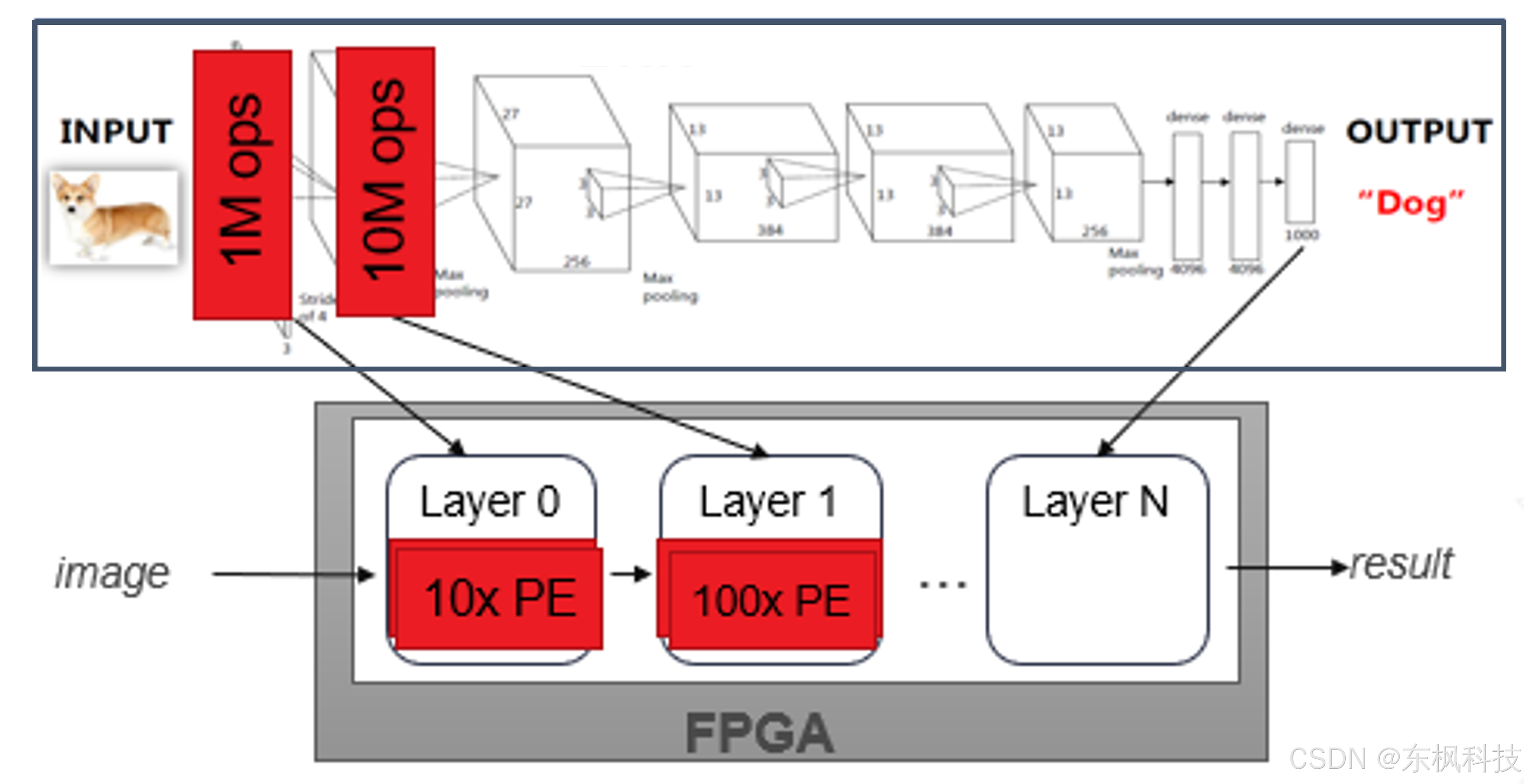

FINN 是 AMD 研究与高级开发部门综合通信和人工智能实验室开发的机器学习框架。它为在 FPGA 上探索和实施量化神经网络推理解决方案提供了端到端流程。FINN 生成数据流架构作为空间中实施的自定义网络的物理表示。它不是通用的 DNN 加速解决方案,而是依赖于协同设计和设计空间探索来进行量化和并行化调整,从而根据资源和性能要求优化解决方案。

特征

- 模板化的 Vitis HLS 和 RTL 流组件库: FINN 附带 HLS 和 RTL 模块库,可将神经网络层实现为流组件。

- 通过数据流实现超低延迟和高性能:通过为每一层组合流式传输组件,FINN 可以生成能够以亚微秒延迟对图像进行分类的加速器。

- 许多端到端示例设计:我们提供的示例从训练量化神经网络开始,一直到在硬件上运行的加速设计。这些示例涵盖了一系列数据集和网络拓扑。

- 快速设计生成的工具流: FINN 工具流支持自动或手动为每层分配单独的计算资源,并生成完整的设计以供综合。这样可以快速探索设计空间。

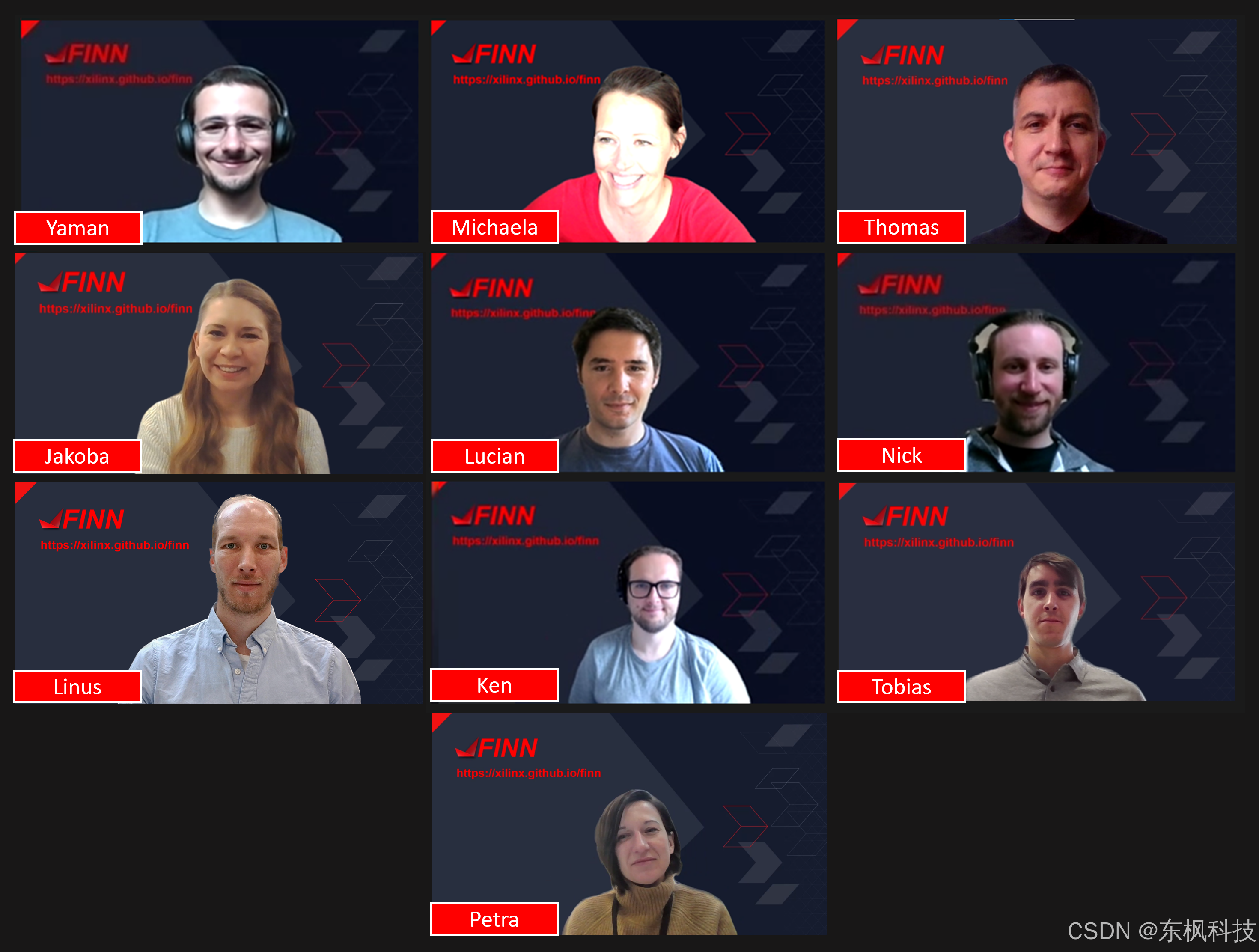

FINN 团队由 Ralph Wittig 领导的 AMD 研究成员(AMD 研究与高级开发部)以及 Allen Chen 领导的定制与战略工程部成员组成,与 Pynq 团队密切合作。

从左上到右下:Yaman Umuroglu、Michaela Blott、Thomas Preusser、Jakoba Petri-Koenig、Lucian Petrica、Nicholas Fraser、Linus Witschen、Ken O'Brien、Tobias Alonso Pugliese、Petra Hrg

从左上到右下:Eamonn Dunbar、Kasper Feurer、Aziz Bahri、John Monks、Mirza Mrahorovic