1.目的:

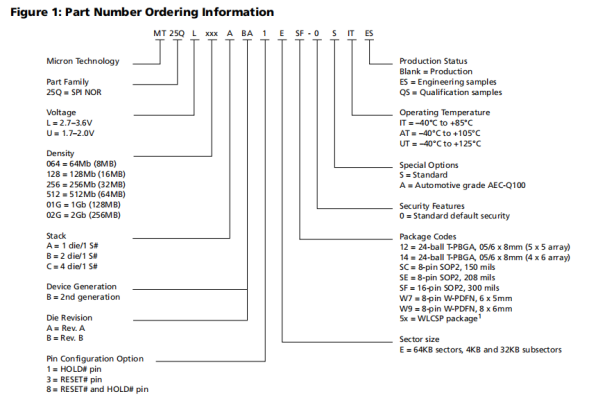

基于Vivado平台,通过对MT25QL256 SPI FLASH进行在线烧写,实现FPGA程序在线更新升级。

2.MT25QL256 SPI FLASH描述

2.1.Features

- spi兼容串行总线接口

- Single and double transfer rate (STR/DTR)

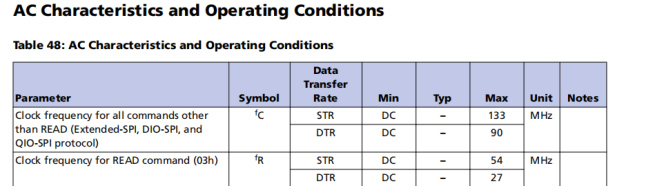

- Clock frequency

- 133 MHz (MAX) for all protocols in STR

- 90 MHz (MAX) for all protocols in DTR

- Dual/quad I/O command将吞吐量提高到90 MB/s

- 支持协议: Extended, Dual and Quad I/O both STR and DTR

- Execute-in-place (XIP)

- PROGRAM/ERASE SUSPEND 操作

- Volatile and nonvolatile 配置设置

- Software reset

- 针对特定产品型号的额外reset 引脚

- 3-byte and 4-byte address modes-允许超过128Mb的内存访问

- 主存储器外的专用64-byte OTP区域

- 可读且用户可锁定

- 使用PROGRAM OTP 命令永久锁定

- 擦除功能

- Bulk erase

- Sector erase 64KB

- Subsector erase 4KB, 32KB

- 擦除性能:400KB/秒(64KB扇区)

- 擦除性能:80KB/秒(4KB子扇区)

- 编程性能:2MB/秒

- 安全性和写保护

- 每个64KB扇区的Volatile and nonvolatile锁定和软件写保护

- Nonvolatile配置锁定

- 密码保护

- 硬件写保护:nonvolatile bits (BP[3:0] and TB) 确定保护区的大小

- 上电期间的编程/擦除保护

- CRC检测对原始数据的意外更改

- 电子签名

- JEDEC标准3-byte签名(BA19h)

- Extended device ID:另外两个字节用于标识设备的生产厂商选项

- JESD47H-compliant

- 每个扇区最少可擦除100,000次

- 数据保留:20年(TYP)

- 每个扇区最少可擦除100,000次

2.2.Signal Descriptions

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | Type | Description |

| S# | Input | Chip select:当s#被驱动为高时,设备将进入待机模式,除非内部PROGRAM、ERASE或WRITE STATUS REGISTER周期正在进行中。所有其他输入引脚被忽略,输出引脚是高阻态的。然而,对于提供的专用配置引脚RESET#,即使在s#为高时,RESET#输入引脚仍保持活跃状态。 驱动s# 为低启用设备,将其置于活跃模式。 在通电后,在任何command开始之前,都需要在s#上有一个下降沿。 |

| C | Input | Clock:提供串行接口的时序。Command输入锁存在时钟的上升沿上。在STR command或protocol中,address and data输入锁存在时钟的上升沿,而data输出在时钟的下降沿。在DTR command或protocol中,address and data输入锁存在时钟的两个沿,data输出在时钟的两个沿。 |

| RESET# | Input | RESET#:当RESET#被驱动为低电平时,设备复位,所有输出为高阻。当内部进行WRITE, PROGRAM, or ERASE操作时,如果RESET#驱动为低,data可能丢失。使用nonvolatile configuration register bit4 或者enhanced volatile config bit4 禁用RESET#功能。对于与RESET#共享DQ3引脚的引脚配置,在QIO-SPI模式下禁用RESET#功能。 |

| HOLD# | Input | HOLD: 暂停与设备的串行通信,而不取消选择或重置设备。所有输出为高阻,输入被忽略。使用nonvolatile configuration register bit4 或者enhanced volatile config bit4 禁用HOLD#功能。 对于与HOLD#共享DQ3引脚的引脚配置,在QIO-SPI模式或启用DTR操作时禁用HOLD#功能。 |

| W# | Input | Write protect: 冻结status register和status register的enable/disable bit。当status register的enable/disable位设置为1并且w#信号被驱动为LOW时,status register的nonvolatile bit变为只读并且WRITE STATUS REGISTER将不执行操作。在使用QOFR和QIOFR指令的extended-SPI协议期间,以及使用QIO-SPI协议时,该引脚作为DQ2的输入/输出。这个信号没有内部上拉,它不能保持浮动,必须被驱动,即使没有使用w# /DQ2功能 |

| DQ[3:0] | I/O | Serial I/O: 双向DQ信号传输address, data, and command信息,在extended I/O协议(XIO-SPI)中使用legacy(x1) SPI命令时,DQ0是输入,DQ1是输出。不使用DQ[3:2]。 当在XIO-SPI中使用dual commands或在DIO-SPI中使用dual commands时,DQ[1:0]是I/O。不使用DQ[3:2]。 当在XIO-SPI中使用quad commands或在QIO -SPI中使用quad commands时,DQ[3:0]时I/O。 |

2.3.Status Register

Status register bits可以通过"READ STATUS REGISTER"命令或"WRITE STATUS REGISTER"命令进行读取或写入操作。当status registe的enable/ disable位(bit 7)设置为1,W#被驱动为低时,status registe的nonvolatile bits变为只读,WRITE STATUS REGISTER操作将不能执行。退出这种硬件保护模式的唯一方法是驱动W#为高。

|-------------|--------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------|

| Bit | Name | Settings | Description | Notes |

| 7 | Status register write enable/disable | 0 = Enabled(Default) 1 = Disabled | Nonvolatile control bit:与w#一起使用,用于启用或禁用对状态寄存器的写入。 | |

| 5 | Top/bottom | 0 = Top (Default) 1 = Bottom | Nonvolatile control bit:确定由块保护位定义的受保护内存区域是从内存数组的顶部还是底部开始。 | |

| 6,4:2 | BP[3:0] | See Protected Area tables | Nonvolatile control bit:定义了受软件保护以防编程或擦除操作的存储器。当一个或多个块保护位被设置为 1 时,指定的存储器区域将受到保护,防止编程和擦除操作。 | 1 |

| 1 | Write enable latch | 0 = Clear (Default) 1 = Set | Volatile control bit:设备上电时此位被清除,以防止无意的WRITE、PROGRAM或ERASE操作,要使能这些操作,必须先执行WRITE ENABLE操作来设置该位。 | |

| 0 | Write in progress | 0 = Ready (Default) 1 = Busy | Volatile control bit:指示以下命令是否正在执行: WRITE STATUS REGISTER WRITE NONVOLATILE CONFIGURATION REGISTER PROGRAM ERASE | 2 |

2.4.flag status register

Flag status register bits通过READ FLAG STATUS REGISTER命令来读取。所有bit都是易失的,上电后复位为零。

Status bits由内部控制器自动设置和复位。Error bits必须通过CLEAR STATUS REGISTER命令清除。

|-------------|-----------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Bit | Name | Settings | Description |

| 7 | Program or erase controller | 0 = Busy 1 = Ready | Status bit:指示是否有以下命令正在执行: WRITE STATUS REGISTER WRITE NONVOLATILE CONFIGURATION REGISTER PROGRAM ERASE |

| 6 | Erase suspend | 0 = Clear 1 = Suspend | Status bit:指示ERASE操作是否已经挂起或即将挂起。 |

| 5 | Erase | 0 = Clear 1 = Failure or protection error | Error bit:指示ERASE操作是成功还是失败。 |

| 4 | Program | 0 = Clear 1 = Failure or protection error | Error bit:指示PROGRAM操作是成功还是失败。它还指示CRC检查是否成功或失败。 |

| 3 | Reserved | 0 | Reserved |

| 2 | Program suspend | 0 = Clear 1 = Suspend | Status bit:指示PROGRAM操作是否已挂起或即将挂起。 |

| 1 | Protection | 0 = Clear 1 = Failure or protection error | Error bit:指示是否有ERASE或PROGRAM操作试图修改受保护的阵列扇区,或者是否有PROGRAM操作试图访问锁定的OTP空间。 |

| 0 | Addressing | 0 = 3-byte addressing 1 = 4-byte addressing | Status bit:指示启用3-byte address mode还是4-byte address mode。 |

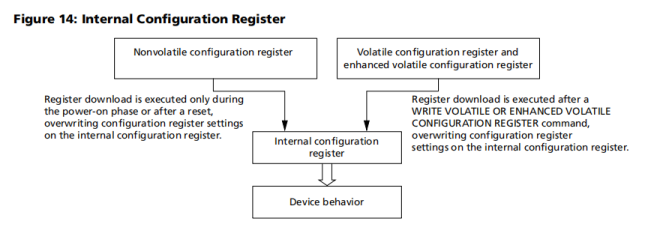

2.5.Internal Configuration Register

内存配置是由用户不能直接访问的internal configuration register来设置的。

用户可以在上电时使用WRITE NONVOLATILE CONFIGURATION REGISTER来更改默认配置,来自nonvolatile configuration register的信息在上电期间或复位后覆盖internal configuration register。

用户可以通过WRITE VOLATILECONFIGURATION REGISTER or the WRITE ENHANCED VOLATILE CONFIGURATION REGISTER commands更改配置,在WRITE命令完成后,来自volatile configuration register的信息会立即覆盖internal configuration register。

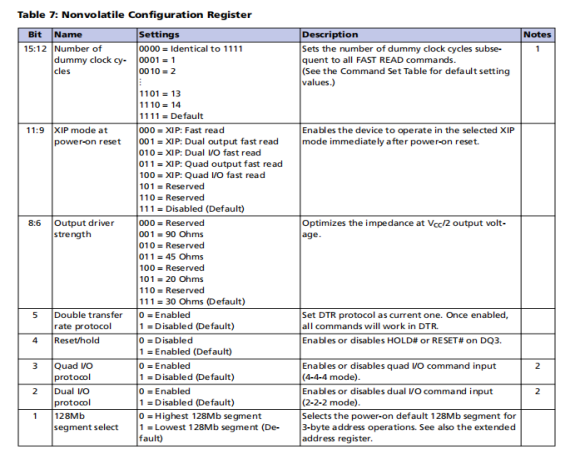

2.6.Nonvolatile Configuration Register

这个寄存器通过READ NONVOLATILE CONFIGURATION REGISTER and the WRITE NONVOLATILE CONFIGURATION REGISTER commands分别控制读写。在上电期间或重置后执行寄存器下载,覆盖决定设备行为的internal configuration register配置。

Note:

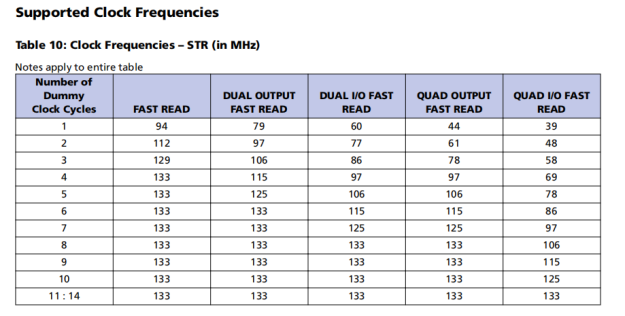

1.周期数必须设置为与时钟频率一致,时钟频率根据FAST READ命令的类型而不同(See Supported Clock Frequencies table)。工作频率的dummy clock周期不足会导致内存读取错误数据。

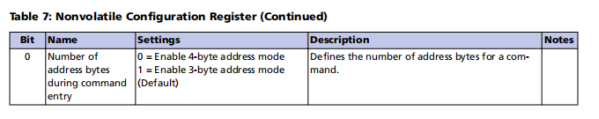

2.7.Volatile Configuration Register

这个寄存器读写分别通过READ VOLATILE CONFIGURATION REGISTER and the WRITE VOLATILE CONFIGURATION REGISTER commands,在这些命令之后执行寄存器下载,覆盖决定设备内存行为的internal configuration register配置。

Note:

1.周期数必须设置为与时钟频率一致,时钟频率根据FAST READ命令的类型而不同(See Supported Clock Frequencies table)。工作频率的dummy clock周期不足会导致内存读取错误数据。

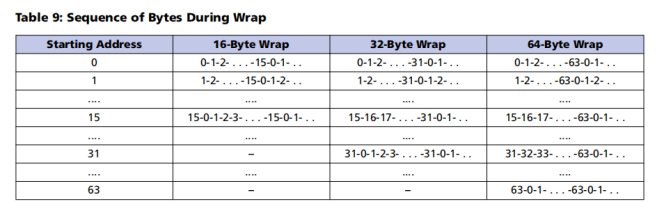

2.See the Sequence of Bytes During Wrap table

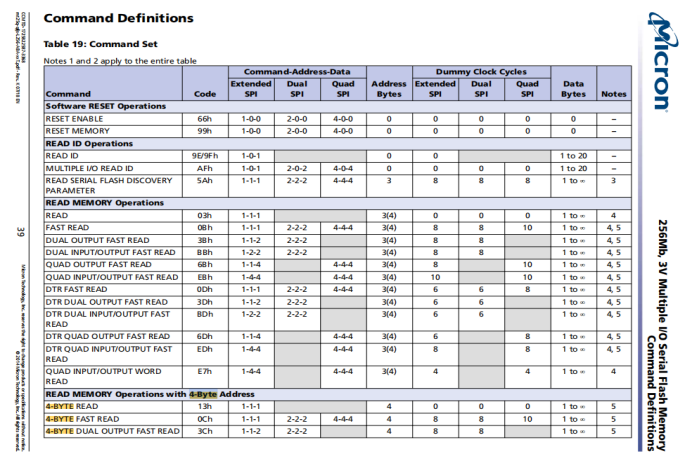

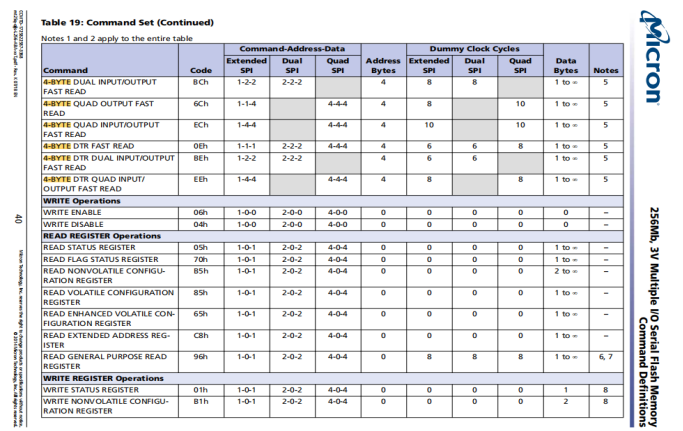

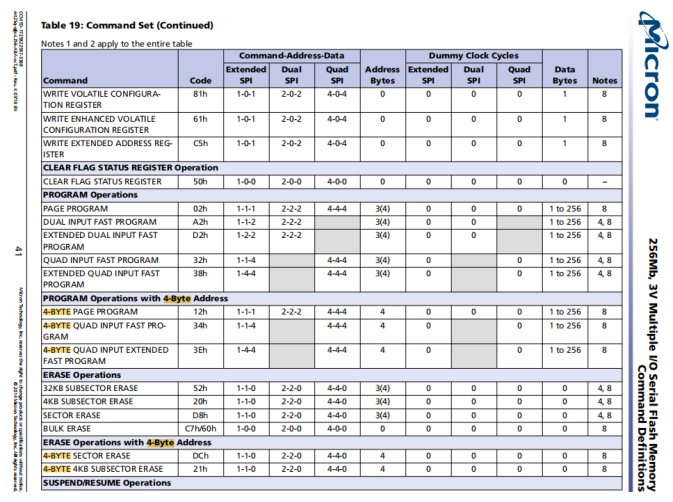

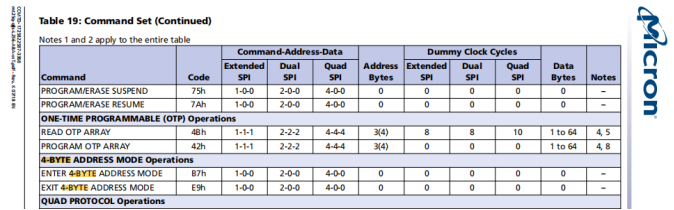

2.8.Command Definitions(部分)

Note:

1.Extended SPI 协议是一种具有附加command的standard SPI 协议,这些附加command扩展了功能,并使能够在多个 DQn 线路上进行地址或数据传输。

2.command code会根据standard, dual, or quad协议分别在 DQn = 1、2 或 4 的几条线上进行传输。然而,一个command也可能不受协议限制地在多条 DQn 线上同时传输address and data。协议列显示了指令使用多少条 DQn 线来传输command、address and data,如以下示例所示:command - address - data = 1 - 1 - 1,或 1 - 2 - 2,或 2 - 4 - 4,等等。

5.出厂时所需的虚拟时钟周期数。用户可以通过nonvolatile configuration register and the volatile configuration register修改dummy clock 周期数。

8.执行该操作前,必须先下发WRITE ENABLE command。

3.命令操作

由描述内容"3-byte and 4-byte address modes-允许超过128Mb的内存访问"可知,超过128Mb的内存访问需要使用4-byte address模式,由于我们使用的是256Mb内存的flash,那么要进行全部内存访问,就要将使用4-byte address模式。通过Command Definitions来看,在4-byte address 模式下有专属的command。

为了简单快捷,我们选定Extended SPI-STR协议来实现功能。那这些command是如何使用的呢?

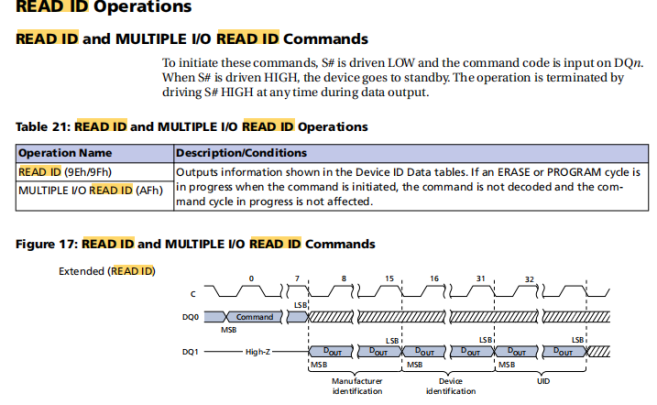

3.1.READ ID Operations (只讲述READ ID(9E/9F)操作)

为了发起命令,s#被驱动为LOW,command code被输入到DQn上。当s#被驱动为HIGH时,设备进入待机状态。在数据输出期间的任何时间,s#驱动为 HIGH都会终止操作。

输出为Device ID Data tables中的信息,如果命令启动时正在进行ERASE或PROGRAM周期,则该命令不被解码,也不影响正在进行的命令周期。

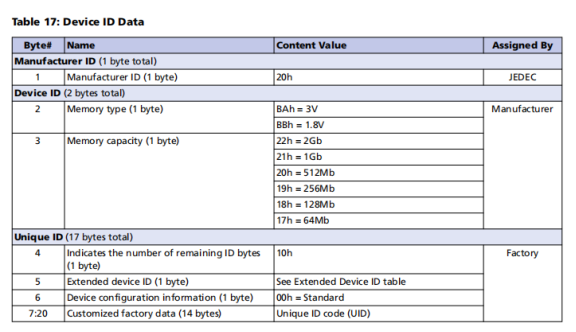

下图为Device ID Data tables,由表可知可读取的ID信息最大为20 bytes。我们一般只需读取前3个byte来确定Device ID。

由下图可知,MT25QL256 SPI flash的Device ID应该为24'h20BA19。

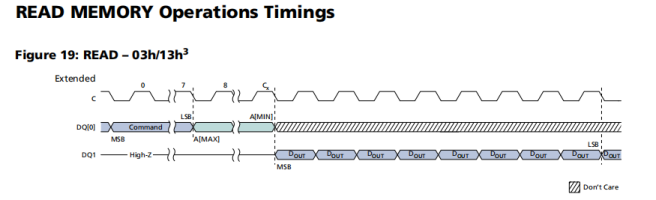

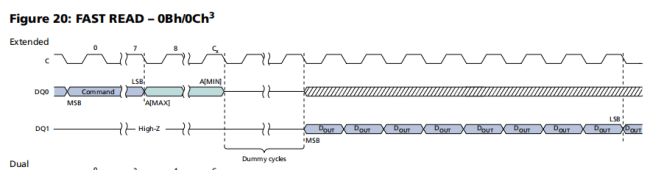

3.2.READ MEMORY Operations (只讲述READ (03h)、FAST READ (0Bh)、4-BYTE READ (13h)、4-BYTE FAST READ (0Ch)操作)

为了发起命令,s#被驱动为LOW,command code被输入到DQn上。然后在DQn上输入address。在数据输出期间的任何时间,s#驱动为 HIGH都会终止操作。

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation Name | Description/Conditions |

| READ (03h) | 设备支持3-byte address (默认),在address周期中输入A[23:0]。在执行任何READ command之后,该设备将从选定的地址输出数据。到达边界后,设备将重新开始读取。 在时钟上升沿期间,每个地址位被锁存。所读取的字节可以位于任何位置,而且地址会随着每次数据字节的输出而自动递增至下一个地址;因此,只需一个指令即可读取整个芯片的数据。 FAST READ可以在更高的频率(fC)下工作。 |

| FAST READ (0Bh) | 设备支持3-byte address (默认),在address周期中输入A[23:0]。在执行任何READ command之后,该设备将从选定的地址输出数据。到达边界后,设备将重新开始读取。 在时钟上升沿期间,每个地址位被锁存。所读取的字节可以位于任何位置,而且地址会随着每次数据字节的输出而自动递增至下一个地址;因此,只需一个指令即可读取整个芯片的数据。 FAST READ可以在更高的频率(fC)下工作。 |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation Name | Description/Conditions |

| 4-BYTE READ (13h) | READ MEMORY操作可以扩展到4-byte address范围,在地址周期内输入[A31:0]。选择3-byte address或4-byte address的地址范围有两种方式:通过 nonvolatile configuration register 或者通过 ENABLE 4-BYTE ADDRESS MODE/EXIT 4-BYTE ADDRESS MODE commands。 在时钟上升沿期间,每个地址位被锁存。所读取的字节可以位于任何位置,而且地址会随着每次数据字节的输出而自动递增至下一个地址;因此,只需一个指令即可读取整个芯片的数据。 FAST READ可以在更高的频率(fC)下工作。 |

| 4-BYTE FAST READ (0Ch) | READ MEMORY操作可以扩展到4-byte address范围,在地址周期内输入[A31:0]。选择3-byte address或4-byte address的地址范围有两种方式:通过 nonvolatile configuration register 或者通过 ENABLE 4-BYTE ADDRESS MODE/EXIT 4-BYTE ADDRESS MODE commands。 在时钟上升沿期间,每个地址位被锁存。所读取的字节可以位于任何位置,而且地址会随着每次数据字节的输出而自动递增至下一个地址;因此,只需一个指令即可读取整个芯片的数据。 FAST READ可以在更高的频率(fC)下工作。 |

由以上内容可知,READ和FAST READ区别在于FAST READ可以用更高的速率读取数据,而且在读取的过程中需要Dummy cycles。

由下表得知,在STR协议下READ最快速率是54MHz。

根据下表,结合在Command Definitions中的FAST READ command code和Note5得知,flash芯片出厂默认的Dummy cycles为8,FAST READ最快速率达到133MHz。在Command Definitions的Note5中得知,nonvolatile configuration register 和 volatile configuration register可以修改dummy clock 周期数。

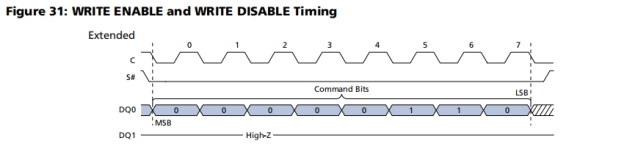

3.3.WRITE ENABLE/DISABLE Operations

为了发起命令,s#被驱动为低电平并保持低电平,直到command code的第8 bit被锁存,之后它必须被驱动为高电平。对于extended spi、dual spi和quad spi协议,分别在DQ0、DQ[1:0]和DQ[3:0]上输入command code。如果在command code锁存之后s#没有被驱动为HIGH,则命令不执行,flag status register error bits不设置,并且Write enable latch保持为其默认设置0,提供对错误数据修改的保护。

|------------------------|------------------------------------------------------------------------------------------------------|

| Operation Name | Description/Conditions |

| WRITE ENABLE(06h) | 在每个PROGRAM, ERASE和WRITE命令之前设置 Write enable latch bit。 |

| WRITE DISABLE(04h) | 清除Write enable latch bit。在保护错误的情况下,WRITE DISABLE不会清除该位。相反,必须发出一个CLEAR FLAG STATUS REGISTER命令来清除两个标志。 |

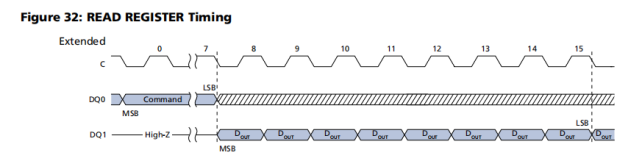

3.4.READ REGISTER Operations(只讲述READ STATUS REGISTER (05h)和READ FLAG STATUS REGISTER (70h))

为了发起命令,s#被驱动为LOW。对于extended SPI协议,输入在DQ0上,输出在DQ1上。对于dual SPI协议,输入/输出在DQ[1:0]上,对于quad SPI协议,输入/输出在DQ[3:0]上。在数据输出期间的任何时间,s#驱动为 HIGH都会终止操作。

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Operation Name | Description/Conditions |

| READ STATUS REGISTER (05h) | 可以连续读取,且可在任何时间进行读取,包括在PROGRAM, ERASE, or WRITE操作期间。如果正在进行其中任何一项操作,则在执行命令之前,建议先检查write in progress bit or P/E controller bit。 |

| READ FLAG STATUS REGISTER (70h) | 可以连续读取,且可在任何时间进行读取,包括在PROGRAM, ERASE, or WRITE操作期间。如果正在进行其中任何一项操作,则在执行命令之前,建议先检查write in progress bit or P/E controller bit。 |

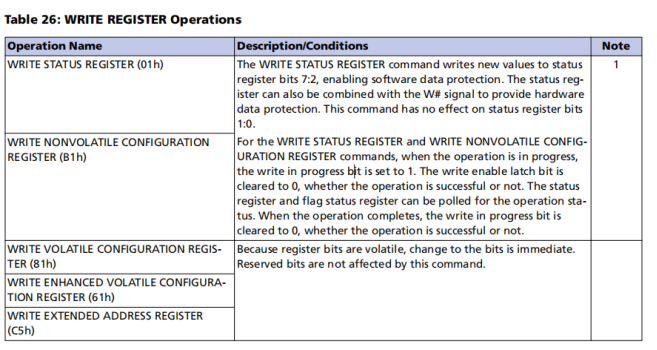

3.5.WRITE REGISTER Operations

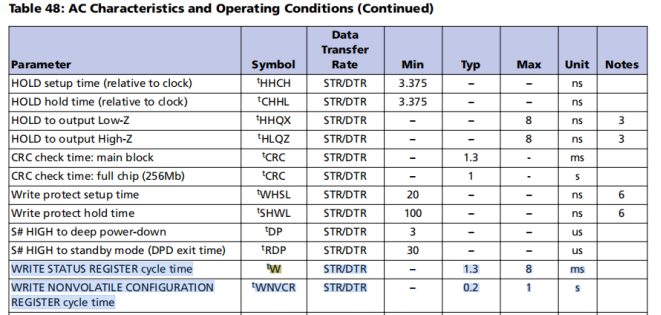

在执行WRITE REGISTER命令之前,必须执行WRITE ENABLE命令将write enable latch bit设置为1。为发起命令,需要驱动s#低并保持低,直到最后一个data字节的第8位被锁存,之后它必须被驱动为高;对于WRITE NONVOLATILE CONFIGURATION REGISTER命令,s#保持低电平,直到最后一个data字节的第16位被锁存。对于extended spi、dual spi和quad spi协议,输入分别在DQ0, DQ[1:0], and DQ[3:0]上,后面跟随data bytes。如果s#没有被驱动为HIGH,则命令不执行,flag status register error bits不设置,并且Write enable latch保持为1。该操作是自定时的,WRITE STATUS REGISTER的操作持续时间为 tW,WRITE NONVOLATILE CONFIGURATION REGISTER的操作持续时间为 tNVCR。

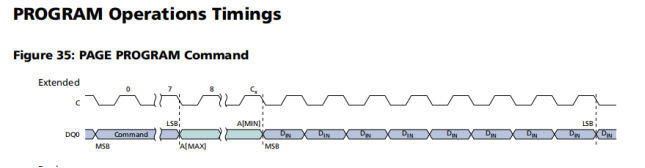

3.6.PROGRAM Operations (只讲述PAGE PROGRAM (02h)和4-BYTE PAGE PROGRAM (12h))

在启动PROGRAM命令之前,必须执行WRITE ENABLE命令将write enable latch bit设置为1,为发起命令,需要驱动s#低并保持低,直到最后一个data字节的第8位被锁存,之后它必须被驱动为高;如果s#没有被驱动为HIGH,则命令不执行,flag status register error bits不设置,并且Write enable latch保持为1。每个address bit被锁存在时钟上升沿期间。当command被应用到受保护扇区时,该命令不被执行,write enable latch bit保持为1,flag status register bit1和bit4被设置。如果操作超时,write enable latch bit被复位,program fail bit置为1。

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation Name | Description/Conditions |

| PAGE PROGRAM (02h) | 当操作正在进行时,write in progress bit置为1。无论操作是否成功,write enable latch bit都被清除为0。The status register and flag status register能够查询当前操作状态。当操作完成后,write in progress bit被清除为0。可以使用PROGRAM/ERASE SUSPEND或PROGRAM/ERASE RESUME命令暂停或恢复操作。 如果最末位地址(即起始地址)的各bit并非全为零,那么超出当前page范围的所有传输数据都将从本page的起始地址进行编程。如果发送到设备的字节数超过最大page大小,则先前存储的数据将被丢弃,而本page内仅保证最后最大页page大小数量的数据字节能够正确编程。如果发送到设备的字节数少于最大page大小,则它们将在指定地址正确编程,而不会对本page的其他字节产生任何影响。 |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation Name | Description/Conditions |

| 4-BYTE PAGE PROGRAM (12h) | PROGRAM操作可以被扩展到一个4-byte address范围,用 [A31:0]在address周期中输入。 选择3-byte address或4-byte address的地址范围有两种方式:通过 nonvolatile configuration register or 通过 ENABLE 4-BYTE ADDRESS MODE/EXIT 4-BYTE ADDRESS MODE commands。 |

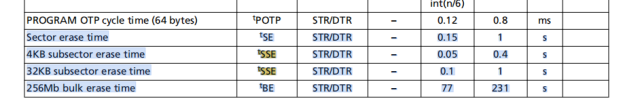

3.7.ERASE Operations

在启动任何ERASE命令之前,必须执行WRITE ENABLE命令将write enable latch bit设置为1;否则,设备将忽略该命令,并且不设置错误位表示操作失败。s#被驱动为低电平并保持低电平,直到最后一个数据字节的第8位被锁存,之后它必须被驱动为高电平。操作自定时,根据命令不同,时长为tSSE、tSE或tBE。

如果s#没有被驱动为HIGH,则不执行该命令,不设置flag status register error bits,并且write enable latch bit仍然设置为1。对受保护子区域所施加的命令并未被执行。write enable latch bit仍保持为 1,且flag status register的bit1 和bit5 被设置。

当操作正在进行时,the program or erase controller bit of the flag status register is set to 0。同时,write in progress bit设置为1。当操作完成后,write in progress bit被清除为0。无论操作是否成功,write enable latch bit都被清除为0。如果操作超时,write enable latch bit复位,erase error bit置1。

status register 和 flag status register能够查询当前操作状态。当操作完成时,这些寄存器位被清除。

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Operation Name | Description/Conditions |

| SUBSECTOR ERASE (52h/20h) | 将选择的subsector or sector bits设置为FFh。subsector内的任何地址都可以有效输入。每个address bit被锁存在时钟上升沿,这个操作可以分别通过PROGRAM/ERASE SUSPEND和PROGRAM/ERASE RESUME命令暂停和恢复。 |

| SECTOR ERASE (D8h) | 将选择的subsector or sector bits设置为FFh。subsector内的任何地址都可以有效输入。每个address bit被锁存在时钟上升沿,这个操作可以分别通过PROGRAM/ERASE SUSPEND和PROGRAM/ERASE RESUME命令暂停和恢复。 |

| BULK ERASE (C7h/60h) | Sets the device bits to FFh. 如果有sector被锁定,则不执行该命令。write enable latch bit仍然被设置为1,并且flag status register bit1和bit5被设置。 |

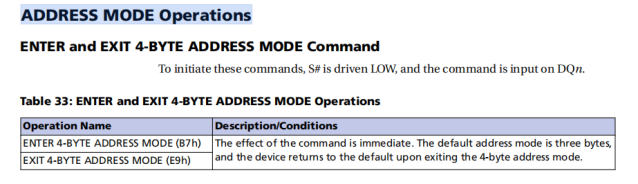

3.8.ADDRESS MODE Operations

该命令立即生效。默认的3-byte address mode,退出4-byte address mode后,设备将恢复到默认的address mode。

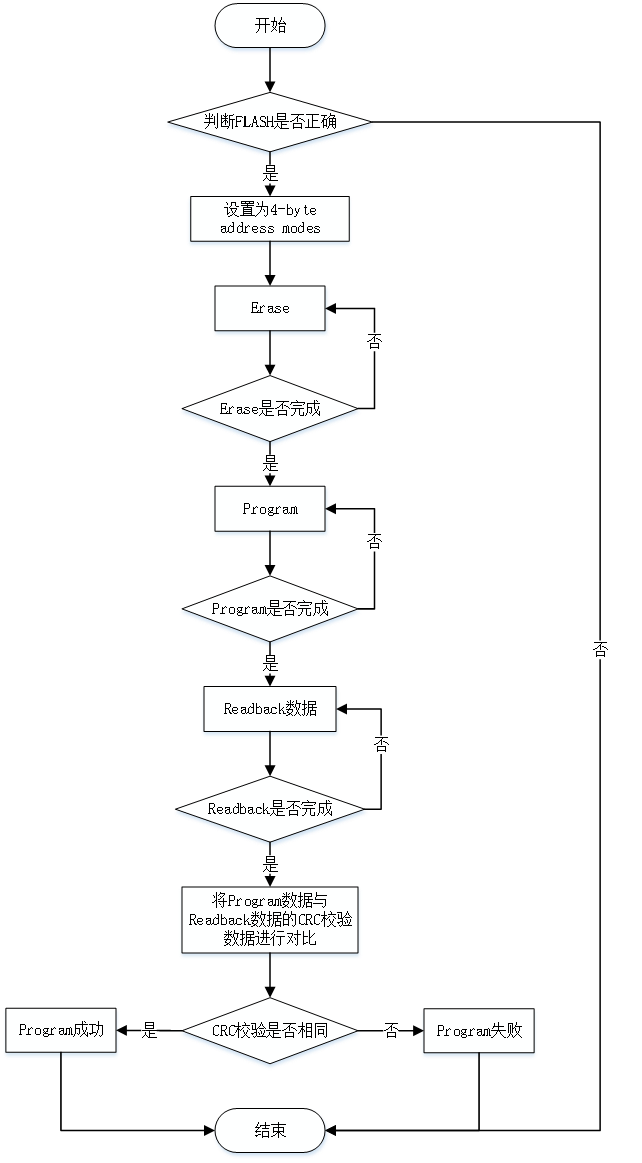

**4.**结论

通过对以上内容的了解,对整个程序烧写流程做以下规划:

5.STARTUPE2原语

当对flash进行在线操作时,需要使用STARTUPE2原语为CCLK引脚提供时钟,也相当于为flash Clock引脚提供时钟。

STARTUPE2 #(

.PROG_USR("FALSE"), // Activate program event security feature. Requires encrypted bitstreams.

.SIM_CCLK_FREQ(0.0) // Set the Configuration Clock Frequency(ns) for simulation.

)

STARTUPE2_inst (

.CFGCLK(), // 1-bit output: Configuration main clock output

.CFGMCLK(), // 1-bit output: Configuration internal oscillator clock output

.EOS(), // 1-bit output: Active high output signal indicating the End Of Startup.

.PREQ(), // 1-bit output: PROGRAM request to fabric output

.CLK(0), // 1-bit input: User start-up clock input

.GSR(0), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port name)

.GTS(0), // 1-bit input: Global 3-state input (GTS cannot be used for the port name)

.KEYCLEARB(1), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM)

.PACK(1), // 1-bit input: PROGRAM acknowledge input

.USRCCLKO(outSpiClk), // 1-bit input: User CCLK input

// For Zynq-7000 devices, this input must be tied to GND

.USRCCLKTS(0), // 1-bit input: User CCLK 3-state enable input

// For Zynq-7000 devices, this input must be tied to VCC

.USRDONEO(1), // 1-bit input: User DONE pin output control

.USRDONETS(1) // 1-bit input: User DONE 3-state enable output

);|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------|

| 引脚名称 | 类型 | 描述 |

| CLK | 输入 | 用户启动时钟引脚。来自驱动设备启动序列时钟的FPGA逻辑的输入。为启动序列提供用户定义的CCLK。Spartan 7 7S6和7S15设备不支持启动序列的用户定义CCLK(ITSTREAM.STARTUP.STARTUPCLK属性的UserClk值)。 |

| GSR | 输入 | 一般将其设置为低电平表示禁用 |

| GTS | 输入 | 全局三态引脚,作用是将配置库以外的用户I/O都配置成高阻态,一般情况将其设置为低电平。 |

| KEYCLEARB | 输入 | 从电池支持的RAM中清除AES解密器秘钥。FPGA结构的低电平输入。当数据表中的TPROGRAM延时保持低电平时,该引脚会从电池备份RAM(BBRAM)中擦除解密秘钥的内容。 |

| PACK | 输入 | PROGRAM_B或JPROGRAM确认。FPGA逻辑的输入,用于"确认"PROGRAM_B信号的断言,并允许PROGRAM_B状态机的其余部分继续重置FPGA。仅当设置了PROG_USR属性时,此引脚才启用。 |

| PREQ | 输出 | FPGA逻辑需要PROGRAM_B脉冲或JPROGRAM。FPGA逻辑的输出。此引脚是PROGRAM_B状态机重置设备的"请求",允许PROGRAM_B请求被门控,直到设计处于可以完成重置的状态。仅当设置了PROG_USR属性时,此引脚才启用。 |

| USRCCLKO | 输入 | CCLK引脚。配置后,FPGA逻辑的输入,将定制的逻辑生成时钟频率驱动到FPGA CCLK引脚上。可用于外部配置后访问SPI闪存设备。更多详细信息请参见USRCCLKO。 |

| USRCCLKTS | 输入 | 用户CCLK三态启用CCLK引脚。FPGA逻辑的高电平输入,在配置后使用时将FPGA CCLK引脚置于高Z状态。对于大多数应用,此引脚应系低。 |

| USRDONEO | 输入 | 完成引脚输出值。连接到FPGA DONE引脚的FPGA逻辑的输入。 |

| USRDONETS | 输入 | 用户完成了DONE引脚的三态启用。FPGA逻辑的高电平输入,使DONE进入高阻状态。通常设置为低电平用来启用DONE。 |

| CFGCLK | 输出 | 配置逻辑主时钟输出。FPGA逻辑的输出。从专用内部环形振荡器输出时钟信号,其中典型频率由比特流配置速率选项定义。输出仅在配置期间以及启用持久性的主模式下处于活动状态。 |

| CFGMCLK | 输出 | 配置内部振荡器时钟输出。FPGA逻辑的输出。从专用内部环形振荡器输出典型频率为65 MHz的时钟信号。 |

| EOS | 输出 | 启动结束。高电平输出将EOS标志回声到FPGA逻辑中。可以用作指示FPGA已准备好运行的复位信号。 |