1. 概述

在高速数据采集和通信系统中,如何将接收到的高速串行数据 转换为FPGA内部可以处理的并行数据 ,是一个关键挑战。Xilinx 7系列FPGA提供的ISERDESE2(Input Serial-to-Parallel Logic Resources - 输入串并转换逻辑资源)正是为解决这一问题而设计的专用硬件资源。

ISERDESE2是一个专用的串并转换器 ,具备特定的时钟和逻辑特性,旨在便于实现高速源同步应用。它避免了在FPGA架构中设计解串器时遇到的额外时序复杂性问题,使得工程师能够轻松实现Gbps级别的数据接收。

2. ISERDESE2的核心特性

ISERDESE2具备丰富的特性,使其成为高速接口设计的理想选择:

2.1 灵活的串并转换能力

-

支持SDR(单数据速率)和DDR(双数据速率)模式

-

SDR模式:可生成2-8位宽的并行数据

-

DDR模式 :单个ISERDESE2可生成4、6、8位并行数据;两个级联时可生成10或14位并行数据

2.2 Bitslip子模块

这个子模块允许设计人员对进入FPGA架构的并行数据流的顺序进行重新排序,是实现字对齐的关键功能。

2.3 多种接口类型支持

ISERDESE2支持MEMORY(内存接口) 、NETWORKING(网络接口) 、**OVERSAMPLE(过采样)**等多种工作模式,可灵活应用于不同场景。

3. ISERDESE2原语详解

3.1 原语模板

在Vivado中,可以通过获取原语模板来实例化ISERDESE2:

ISERDESE2 #(

.DATA_RATE("DDR"), // DDR, SDR

.DATA_WIDTH(4), // Parallel data width (2-8,10,14)

.DYN_CLKDIV_INV_EN("FALSE"), // Enable DYNCLKDIVINVSEL inversion (FALSE, TRUE)

.DYN_CLK_INV_EN("FALSE"), // Enable DYNCLKINVSEL inversion (FALSE, TRUE)

// INIT_Q1 - INIT_Q4: Initial value on the Q outputs (0/1)

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.INIT_Q3(1'b0),

.INIT_Q4(1'b0),

.INTERFACE_TYPE("MEMORY"), // MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE

.IOBDELAY("NONE"), // NONE, BOTH, IBUF, IFD

.NUM_CE(2), // Number of clock enables (1,2)

.OFB_USED("FALSE"), // Select OFB path (FALSE, TRUE)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

// SRVAL_Q1 - SRVAL_Q4: Q output values when SR is used (0/1)

.SRVAL_Q1(1'b0),

.SRVAL_Q2(1'b0),

.SRVAL_Q3(1'b0),

.SRVAL_Q4(1'b0)

)

ISERDESE2_inst (

.O(O), // 1-bit output: Combinatorial output

// Q1 - Q8: 1-bit (each) output: Registered data outputs

.Q1(Q1),

.Q2(Q2),

.Q3(Q3),

.Q4(Q4),

.Q5(Q5),

.Q6(Q6),

.Q7(Q7),

.Q8(Q8),

// SHIFTOUT1, SHIFTOUT2: 1-bit (each) output: Data width expansion output ports

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.BITSLIP(BITSLIP), // 1-bit input: The BITSLIP pin performs a Bitslip operation synchronous to

// CLKDIV when asserted (active High). Subsequently, the data seen on the Q1

// to Q8 output ports will shift, as in a barrel-shifter operation, one

// position every time Bitslip is invoked (DDR operation is different from

// SDR).

// CE1, CE2: 1-bit (each) input: Data register clock enable inputs

.CE1(CE1),

.CE2(CE2),

.CLKDIVP(CLKDIVP), // 1-bit input: TBD

// Clocks: 1-bit (each) input: ISERDESE2 clock input ports

.CLK(CLK), // 1-bit input: High-speed clock

.CLKB(CLKB), // 1-bit input: High-speed secondary clock

.CLKDIV(CLKDIV), // 1-bit input: Divided clock

.OCLK(OCLK), // 1-bit input: High speed output clock used when INTERFACE_TYPE="MEMORY"

// Dynamic Clock Inversions: 1-bit (each) input: Dynamic clock inversion pins to switch clock polarity

.DYNCLKDIVSEL(DYNCLKDIVSEL), // 1-bit input: Dynamic CLKDIV inversion

.DYNCLKSEL(DYNCLKSEL), // 1-bit input: Dynamic CLK/CLKB inversion

// Input Data: 1-bit (each) input: ISERDESE2 data input ports

.D(D), // 1-bit input: Data input

.DDLY(DDLY), // 1-bit input: Serial data from IDELAYE2

.OFB(OFB), // 1-bit input: Data feedback from OSERDESE2

.OCLKB(OCLKB), // 1-bit input: High speed negative edge output clock

.RST(RST), // 1-bit input: Active high asynchronous reset

// SHIFTIN1, SHIFTIN2: 1-bit (each) input: Data width expansion input ports

.SHIFTIN1(SHIFTIN1),

.SHIFTIN2(SHIFTIN2)

);3.2 关键参数解析

| 参数名 | 说明 | 注意事项 |

|---|---|---|

| DATA_RATE | 定义数据速率模式 | SDR(单数据速率)或DDR(双数据速率),默认DDR |

| DATA_WIDTH | 并行数据宽度 | 与INTERFACE_TYPE和DATA_RATE相关 |

| INTERFACE_TYPE | 接口类型 | MEMORY、NETWORKING、OVERSAMPLE等 |

| IOBDELAY | 输入路径选择 | 决定使用D还是DDLY作为输入 |

| SERDES_MODE | 主从模式 | 位宽扩展时使用,MASTER或SLAVE |

DATA_RATE:定义了输入数据流是作为单数据速率(SDR)还是双数据速率(DDR)进行处理。此属性允许的值为 SDR 和 DDR。默认值为 DDR。

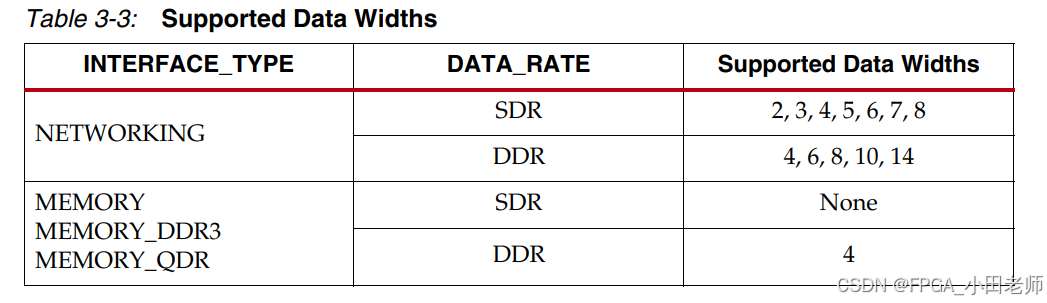

DATA_WIDTH:定义了串并转换器的并行数据输出宽度。该属性的可能取值取决于 INTERFACE_TYPE 和 DATA_RATE 属性。有关支持的数据宽度,请参阅表 3 - 3。

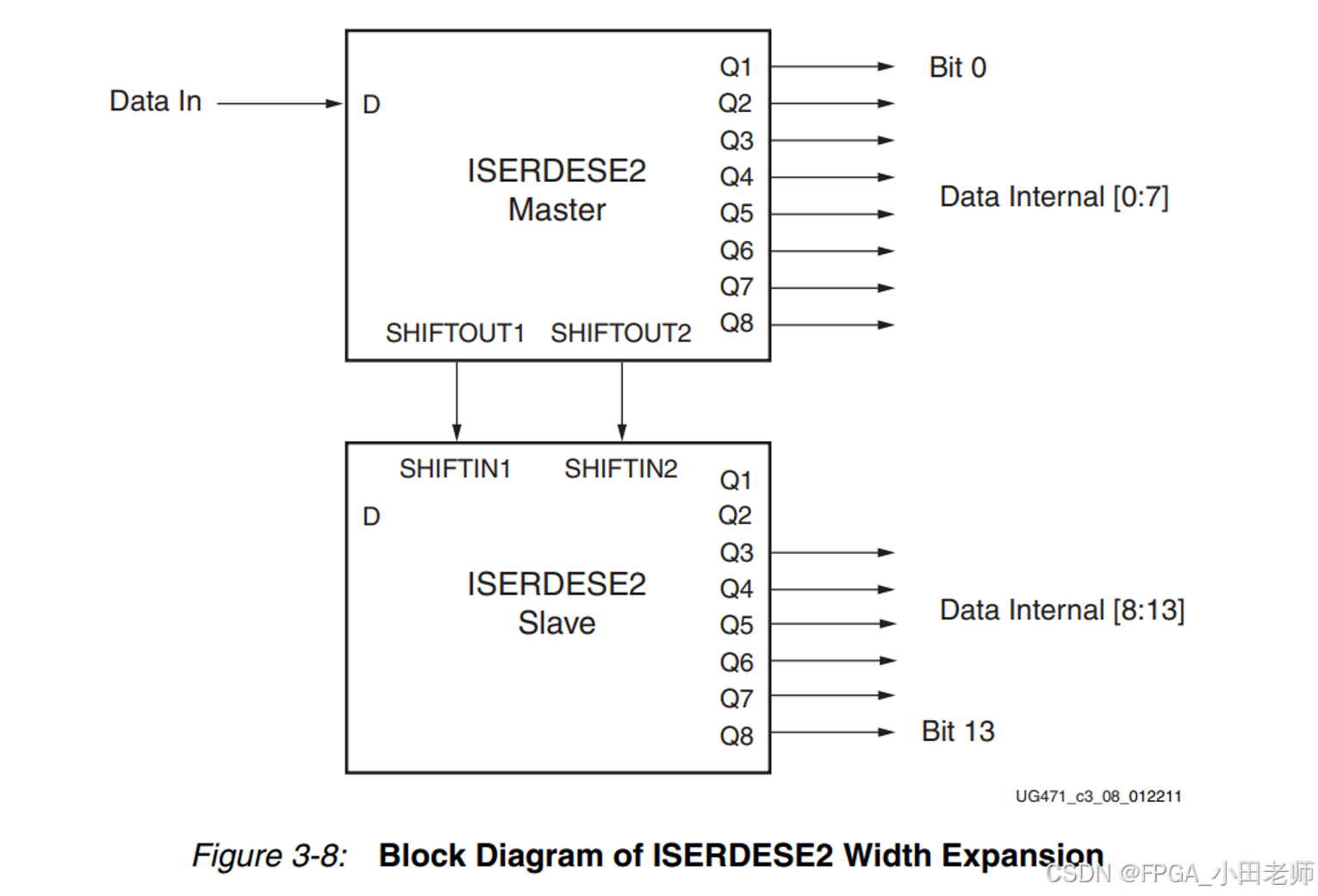

当 DATA_WIDTH 设置为大于 8 的位宽时,必须将一对 ISERDESE2 配置为主从配置。请参阅 ISERDESE2 位宽扩展 。在内存模式下不允许进行位宽扩展。

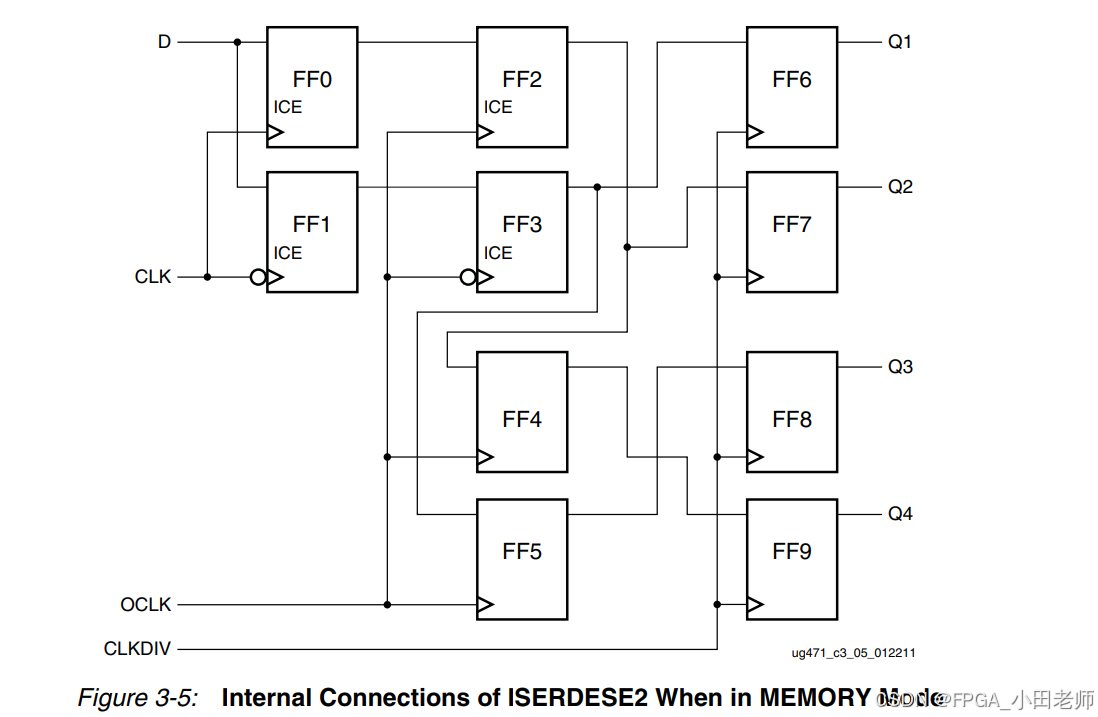

INTERFACE_TYPE:决定了 ISERDESE2 是配置为内存模式还是网络模式。该属性允许的值为 MEMORY、MEMORY_DDR3、MEMORY_QDR、OVERSAMPLE 或 NETWORKING。默认模式为 MEMORY。 图 3 - 5 展示了 ISERDESE2 在 MEMORY 模式下的内部连接情况。

NUM_CE:定义了所使用的时钟使能信号(CE1 和 CE2)的数量。可能的值为 1 和 2(默认值 = 2)

SERDES_MODE :定义了在使用宽度扩展时,ISERDESE2 模块是主模块还是从模块。可能的值为 MASTER(主)和 SLAVE(从)。默认值为 MASTER(主)。请参阅 ISERDESE2 宽度扩展。

4. 核心功能详解

4.1 数据输入路径选择

ISERDESE2提供两个串行数据输入端口:

-

D端口:直接连接到IOB(输入输出块),来自FPGA引脚的信号

-

DDLY端口 :连接到IDELAYE2的输出,可对输入信号进行精细的延迟调整

通过配置IOBDELAY参数,用户可以灵活选择数据路径,实现对输入时序的精确控制。

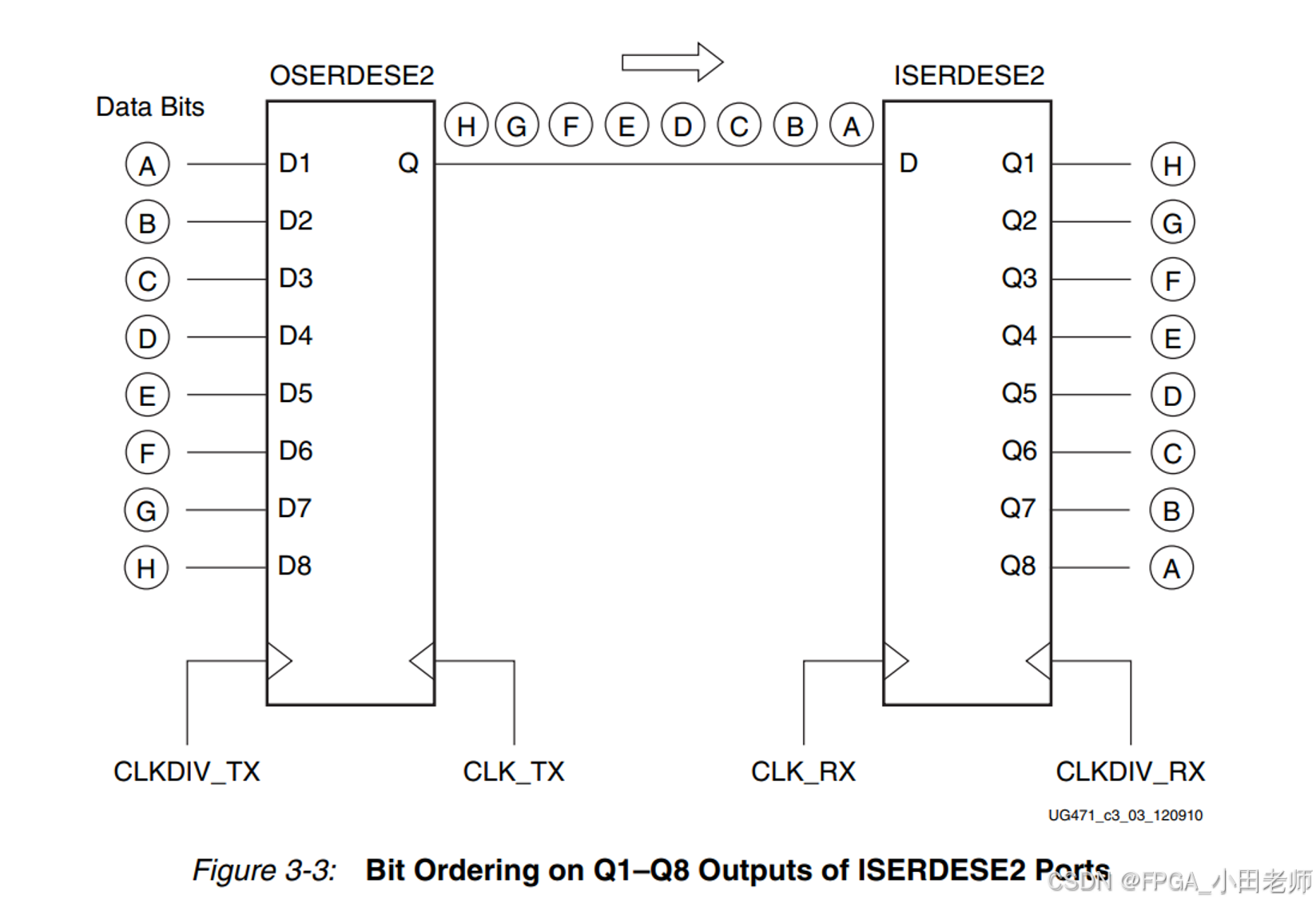

4.2 位序规则

输出端口 Q1 至 Q8 是 ISERDESE2 模块的寄存输出,一个 ISERDESE2 模块最多可支持 8 位(即 1:8 解串),位宽大于 8(最高可达 14)时,仅支持 DDR 模式。请参阅 ISERDESE2 位宽扩展。

理解ISERDESE2的位序对于正确设计至关重要:

-

输入端:最先到达的串行数据位是最低位

-

输出端 :最先接收的位出现在Q8输出端

如图 3 - 3 所示,OSERDESE2 输入端的位序与 ISERDESE2 模块输出端的位序相反。例如,字 FEDCBA 的最低有效位 A 被置于 OSERDESE2 的 D1 输入端,但相同的位 A 从 ISERDESE2 模块的 Q8 输出端输出。换句话说,D1 是 OSERDESE2 的最低有效输入,而 Q8 是 ISERDESE2 模块的最低有效输出。使用位宽扩展时,发送端 OSERDESE2 的 D1 是最低

4.3 Bitslip子模块------字对齐的利器

Bitslip 是ISERDESE2中最关键也最容易让人困惑的功能模块,主要用于字对齐 。由于上电初始化时间不确定,串并转换模块可能从串行数据流的任意位置开始转换,导致输出的并行数据错位。

4.3.1 Bitslip的工作原理

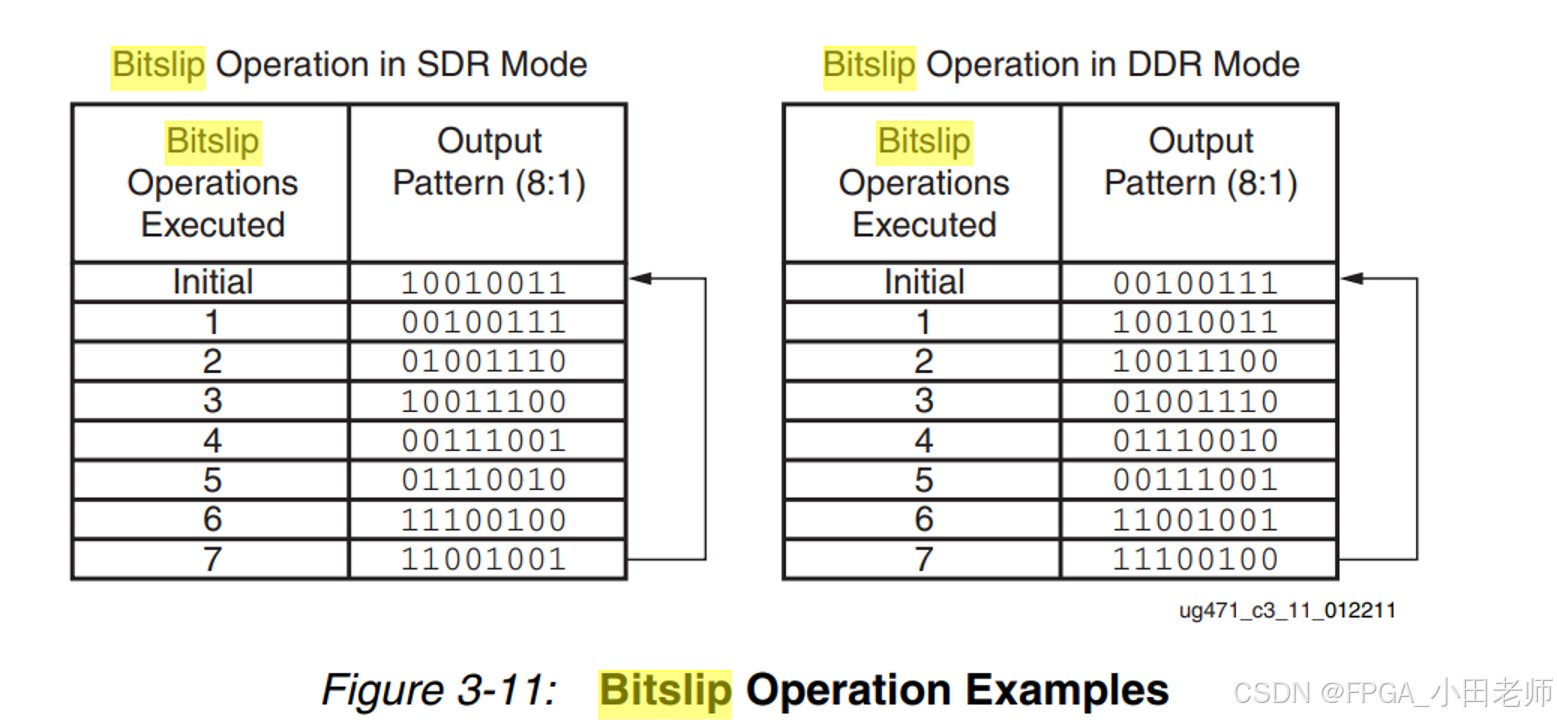

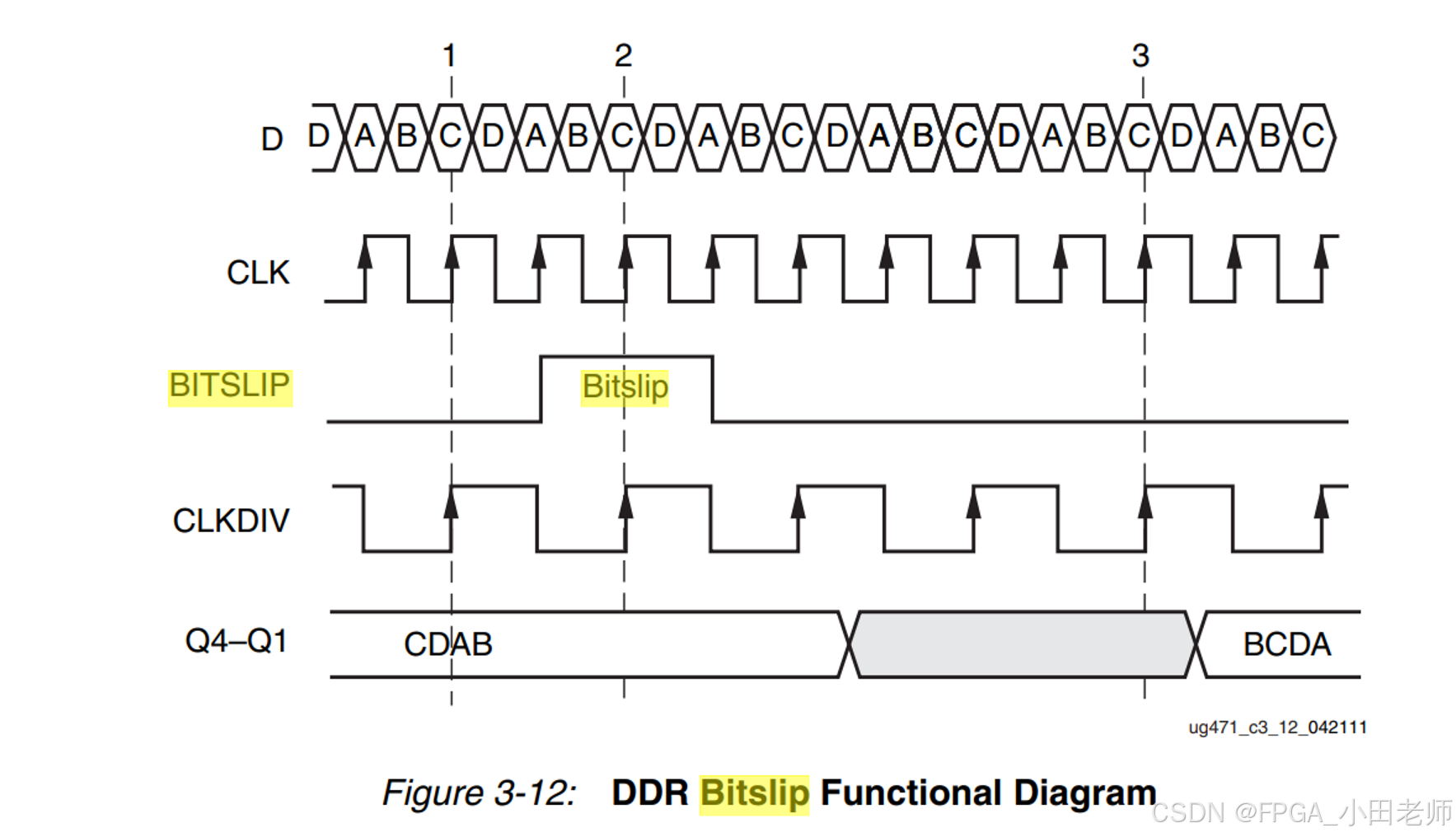

通过拉高BITSLIP引脚(与CLKDIV同步),可以调整并行数据的输出顺序,如图3所示:

-

SDR模式 :每次Bitslip操作使输出模式左移1位

-

DDR模式 :每次Bitslip操作在右移1位 和左移3位之间交替进行

执行8次Bitslip操作后,输出模式会恢复到初始状态,完成一个循环。

4.3.2 实际应用方法

在实际应用中,通常采用训练序列进行字对齐:

-

发送端发送已知的训练序列(如ABCD)

-

接收端检查ISERDESE2的输出是否与预期一致

-

如果不一致,拉高BITSLIP一个CLKDIV周期

-

等待2-3个CLKDIV周期后检查新的输出

-

重复步骤2-4直到获得正确的输出

这种方法通过不断调整转换起始位置,最终找到正确的字边界。

如下,DDR模式下

时钟事件 1 :整个第一个字 CDAB 已被采样到 ISERDESE2 的输入侧寄存器中。位滑动(Bitslip)引脚未置位;该字在 ISERDESE2 中传播,无需任何重新对齐。

时钟事件 2:位滑动引脚置位,这会使位滑动控制器将所有位在内部向右移动一位。位滑动信号在一个(仅一个)CLKDIV 周期内保持高电平。

时钟事件 3:在位滑动引脚置位三个 CLKDIV 周期后,位滑动操作完成,新的移位数据以 BCDA 的形式出现在输出端。

4.3.3 使用注意事项

-

BITSLIP只能在NETWORKING模式下使用

-

BITSLIP必须拉高一个CLKDIV周期,不能连续两个周期拉高

-

两次Bitslip操作之间必须至少间隔一个CLKDIV周期

-

在SDR模式下,每次Bitslip后需等待至少2个CLKDIV周期 再检查数据;DDR模式下需等待至少3个周期

4.4 时钟方法

ISERDESE2的时钟设计对系统性能至关重要:

4.4.1 时钟要求

-

CLK和CLKDIV必须相位对齐

-

CLK是高速串行时钟,与输入数据速率匹配

-

CLKDIV是分频时钟,与并行数据速率匹配

4.4.2 推荐的时钟配置

对于NETWORKING模式:

-

方案1:CLK由BUFIO驱动,CLKDIV由BUFR驱动

-

方案2:CLK和CLKDIV由同一个MMCM/PLL 的不同输出驱动,并使用相同类型的缓冲器(同为BUFG或同为BUFIO/BUFR)

对于MEMORY模式:

-

CLK和OCLK可以由BUFIO驱动,CLKDIV由BUFR驱动

-

或者全部由MMCM/PLL驱动

-

OCLK和CLKDIV必须相位对齐,但CLK和OCLK之间不需要相位关系

5. 位宽扩展技术

当需要大于8位的并行数据时,可以使用两个ISERDESE2进行级联:

5.1 级联配置方法

-

将主ISERDESE2的SERDES_MODE设置为"MASTER",从模块设置为"SLAVE"

-

将主模块的SHIFTOUT1/SHIFTOUT2 连接到从模块的SHIFTIN1/SHIFTIN2

-

两个模块必须处于NETWORKING模式

5.2 位宽支持

-

1:10配置:使用从模块的Q3-Q4输出作为高两位

-

1:14配置:使用从模块的Q3-Q8输出作为高六位

6. 复位与初始化

ISERDESE2的复位设计需要特别注意:

-

RST为高电平异步复位,将CLK和CLKDIV域中大多数触发器异步置低

-

复位应与CLKDIV同步撤销,由内部逻辑重新同步到CLK

-

复位信号宽度应至少为两个CLKDIV脉冲

-

复位撤销后,输出需要经过两个CLKDIV周期才有效

7. 实际应用场景

7.1 LVDS接口接收

在LVDS高速接口应用中,ISERDESE2通常与IDELAYE2配合使用:

-

LVDS数据通过IBUFDS转换为单端信号

-

信号进入IDELAYE2进行精细延迟调整

-

调整后的数据送入ISERDESE2的DDLY端口

-

ISERDESE2完成串并转换

-

通过Bitslip训练实现字对齐

7.2 过采样应用

在7系列FPGA中,ISERDESE2还支持过采样模式(OVERSAMPLE):

-

使用0°和90°相移的时钟对输入数据进行4倍过采样

-

通过数据恢复单元(DRU)从过采样数据中恢复出原始数据

-

可实现最高1.25Gbps的异步数据接收

8. 设计注意事项与常见陷阱

8.1 常见设计错误

-

时钟相位未对齐:CLK和CLKDIV必须相位对齐,这是最常见的问题

-

复位处理不当:复位撤销时序错误导致数据输出无效

-

Bitslip使用不当:连续拉高Bitslip或未等待足够周期就检查数据

-

位序理解错误:混淆Q1和Q8的优先级

8.2 性能优化建议

-

使用IDELAYE2调整输入数据与时钟的相位关系

-

确保CLK和CLKDIV使用同类型时钟缓冲器

-

对于差分输入,主ISERDESE2必须位于差分输入对的正(_P)引脚侧

-

仔细规划复位时序,确保所有ISERDESE2同步退出复位

结语

ISERDESE2是7系列FPGA中实现高速源同步接口的核心资源,其灵活的配置、强大的Bitslip对齐机制以及可扩展的位宽支持,使其成为各种高速接口设计的理想选择。掌握ISERDESE2的正确使用方法,特别是理解其时钟要求和Bitslip操作机制,对于成功实现Gbps级别的数据接收至关重要。

通过本文的详细解析,相信读者能够对ISERDESE2有一个全面的认识,并在实际设计中灵活运用这一强大的硬件资源。