我们知道PS通过内存映射方式方式用户的IP,具体是将用户的逻辑做成AXI_LITE_SALVE外设,PS做为AXI_LITE_MASTER去控制。

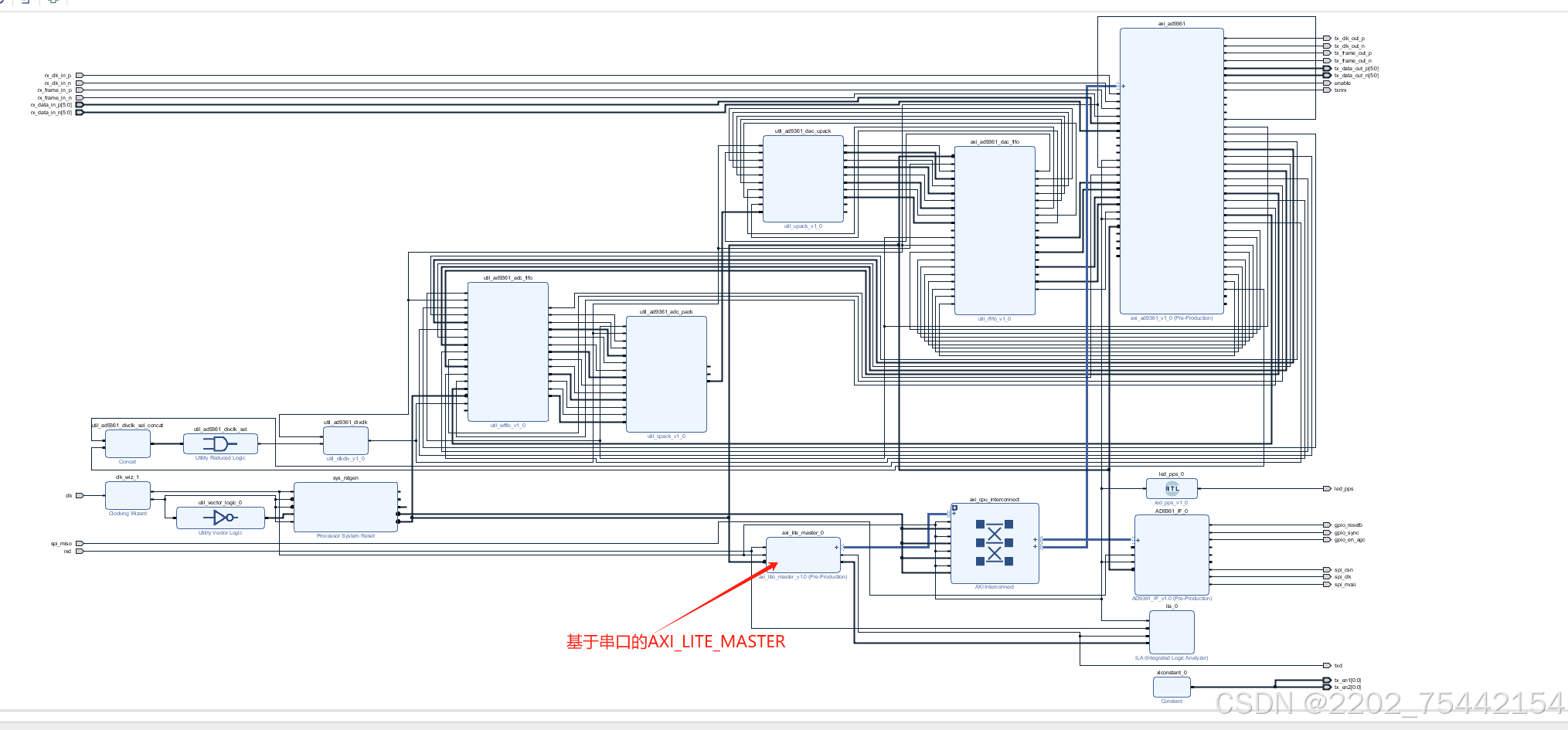

在ZYNQ系统中存在PS所以这个架构和思路很流行,ADI出的配置软件无线电子板的DEMO基本都是基于这样的架构。比如下图【上截图】。

但是在纯FPGA里面没有PS我们要实现这些软件有C语言代码,硬件有AXI_LITE_MASTER功能的就显得更加实用了。我们分别考虑这两个方面:

1,c语言的实现可以使用PC机或者单片机(STM32这样C编译器比较好的单片机)。

2,AXI_LITE_MASTER我们可以自己写一个,跟单片机或者上位机通过串口进行通讯。

这样实际操作的时候我们可以在PC电脑上运行ADI官方提供的DEMO程序,当需要通过AXI_LITE总线控制时候,就调用串口发送规定好的数据包实现对IP内部寄存器的读写。受限于串口速率,这里进行配置控制的速度确实慢了好多,但是好在配置不要求实时,并且数据流都在FPGA内部产生并消化,所以可以符合带宽和灵活性的要求。