本次的实战项目根据公司的具体项目要求进行设计,手把手带你实现一个公司级的项目,可以学习到公司级项目的设计及调试思路。

基于FPGA平台,采用AD9914实现扫频源。

项目需求

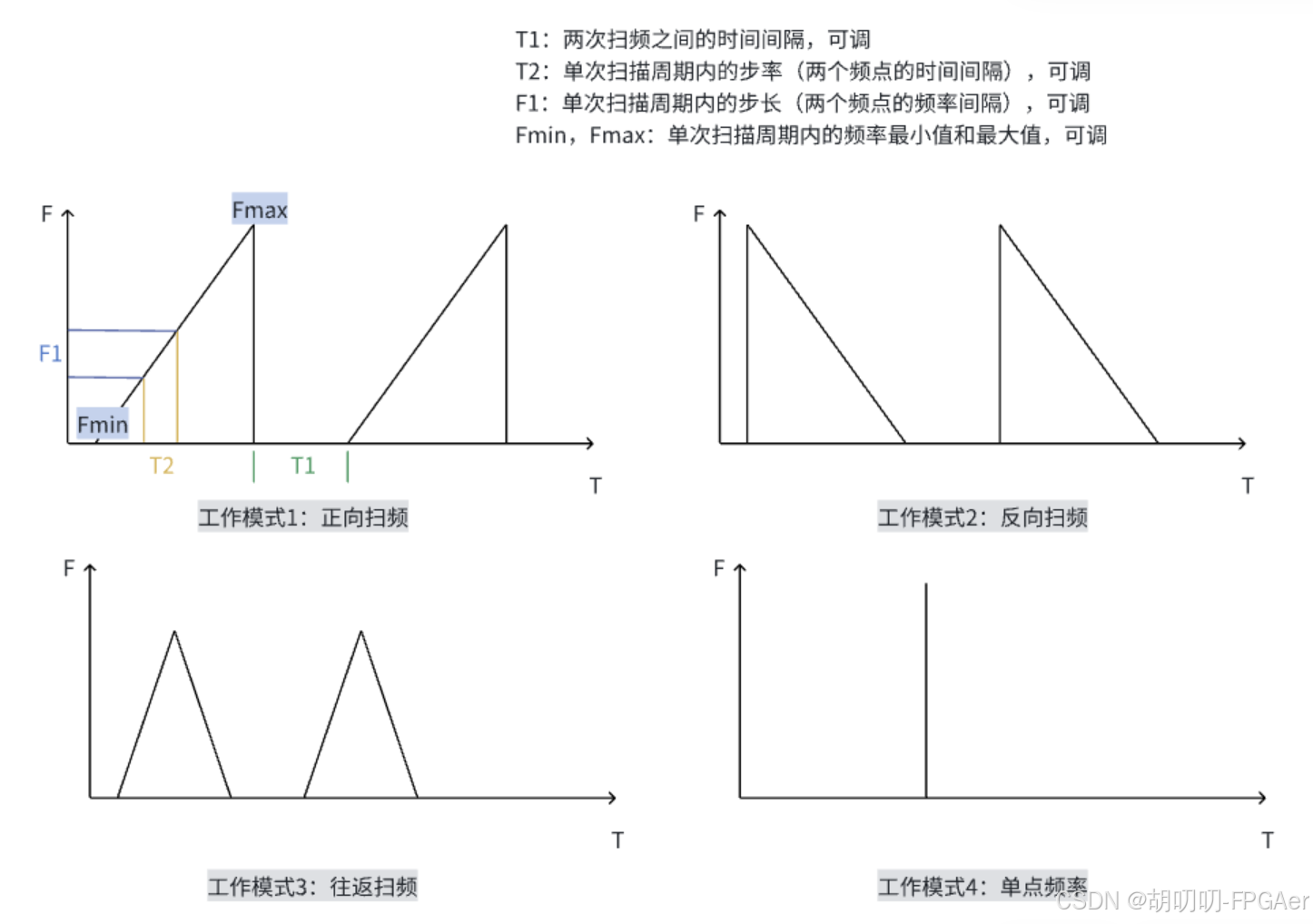

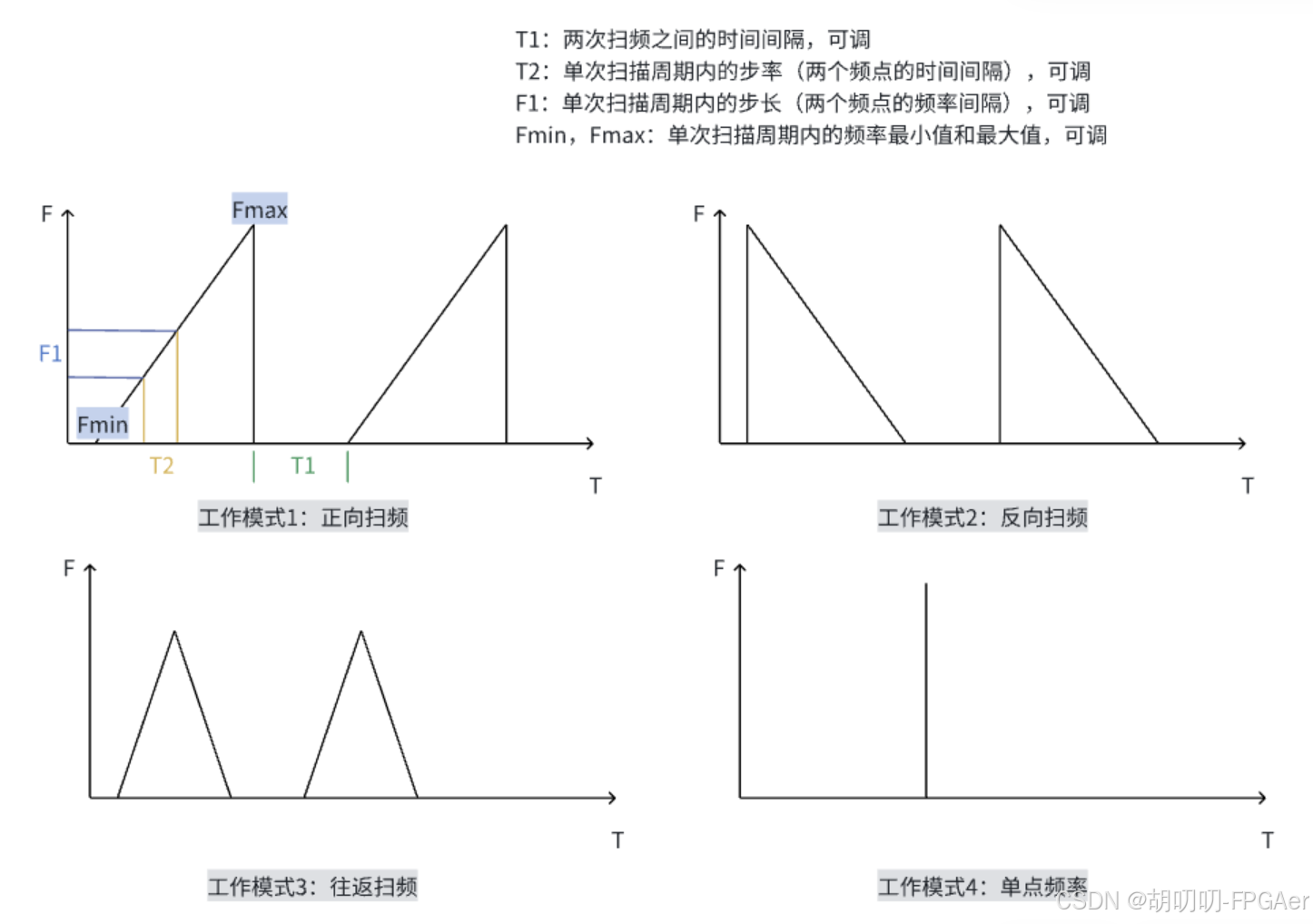

- 实现三种扫频模式和一种单频模式

- 与PC通过TCP进行通信

- 所有参数均可配置

- 数字斜坡上下限值

- 数字斜坡步长、步率

- 两次扫频的时间间隔

- 扫频方向

- 单频的频率、相位、幅度

功能框图

设计平台

- FPGA开发板:alinx AC7021B

- AD9914评估板

- Vivado2021.1

本次的实战项目根据公司的具体项目要求进行设计,手把手带你实现一个公司级的项目,可以学习到公司级项目的设计及调试思路。

基于FPGA平台,采用AD9914实现扫频源。