在FPGA上实现YOLOv5

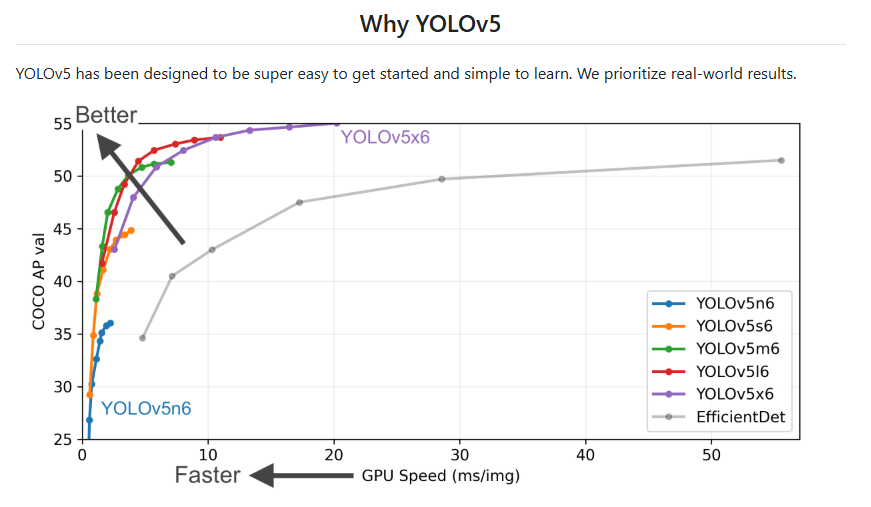

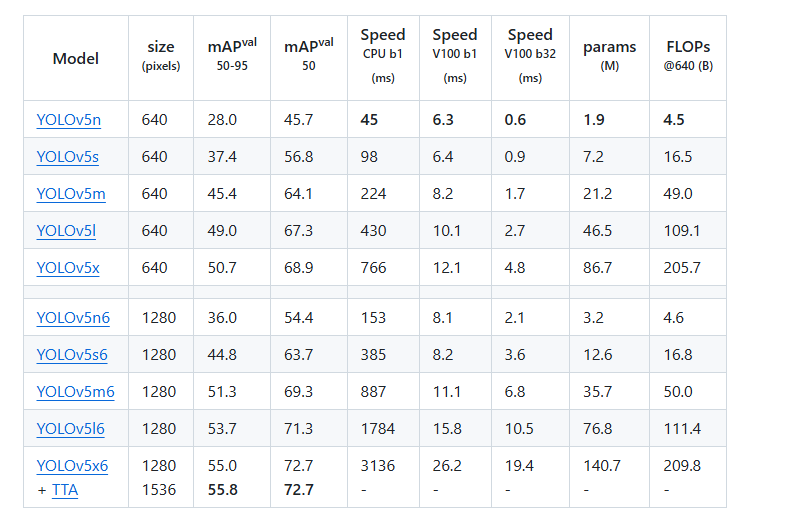

YOLO算法现在被工业界广泛的应用,虽说现在有很多的NPU供我们使用,但是我们为了自己去实现一个NPU所以在本文中去实现了一个可以在FPGA上运行的YOLOv5。

YOLOv5的开源代码链接为

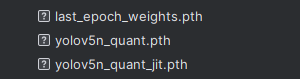

为了在FPGA中实现YOLOv5,我们首先在VOC数据集上面进行算法的训练,得到训练后的文件,并对训练后的文件进行8bit量化操作

得到三个权重文件。

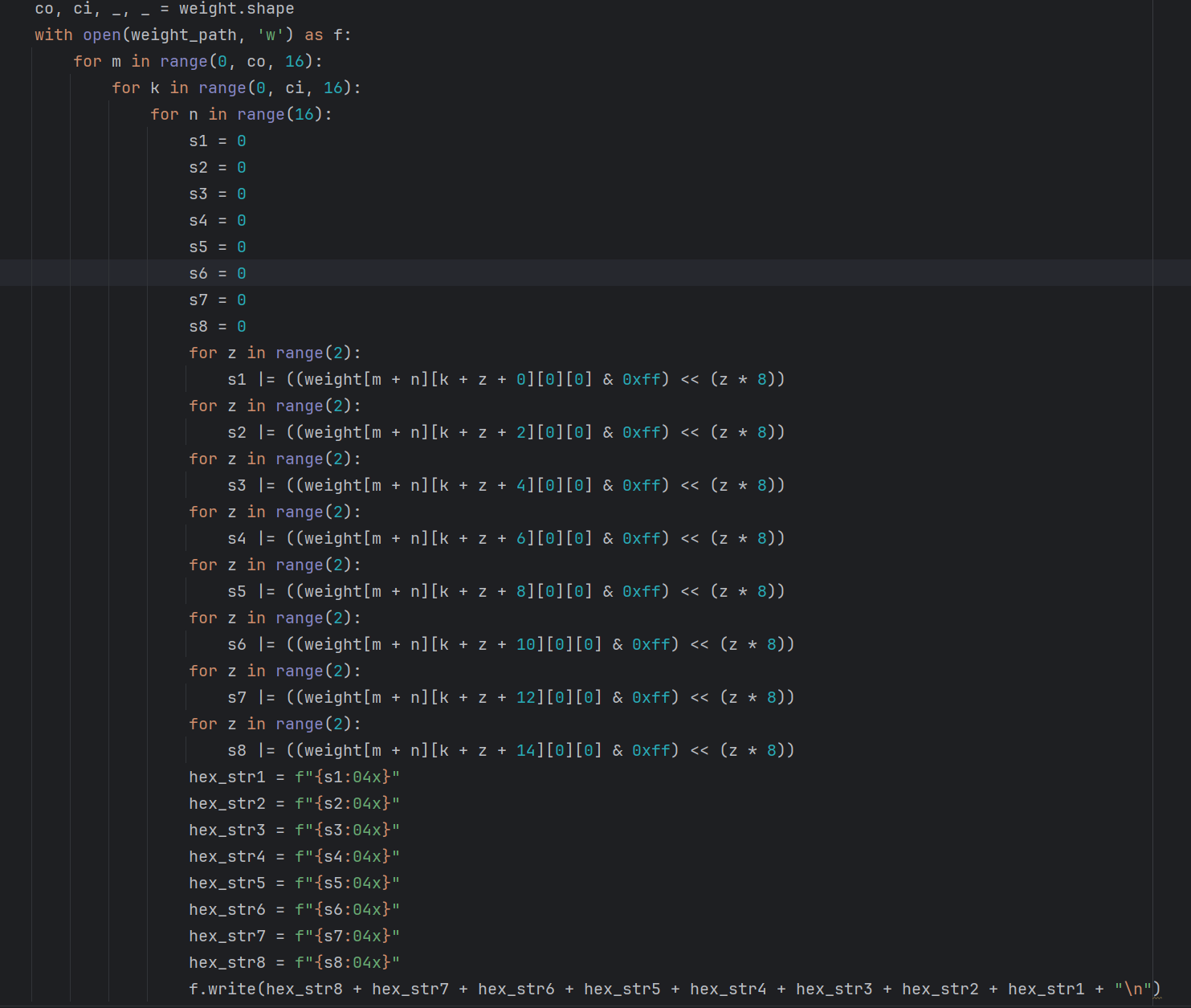

之后为了将这个权重文件发送到FPGA上,所以我们再次使用python去解析这个权重文件,然后按照我们的FPGA加速器的架构对权重进行重组

解析的Python文件示意如下

得到的权重数据示意如下:

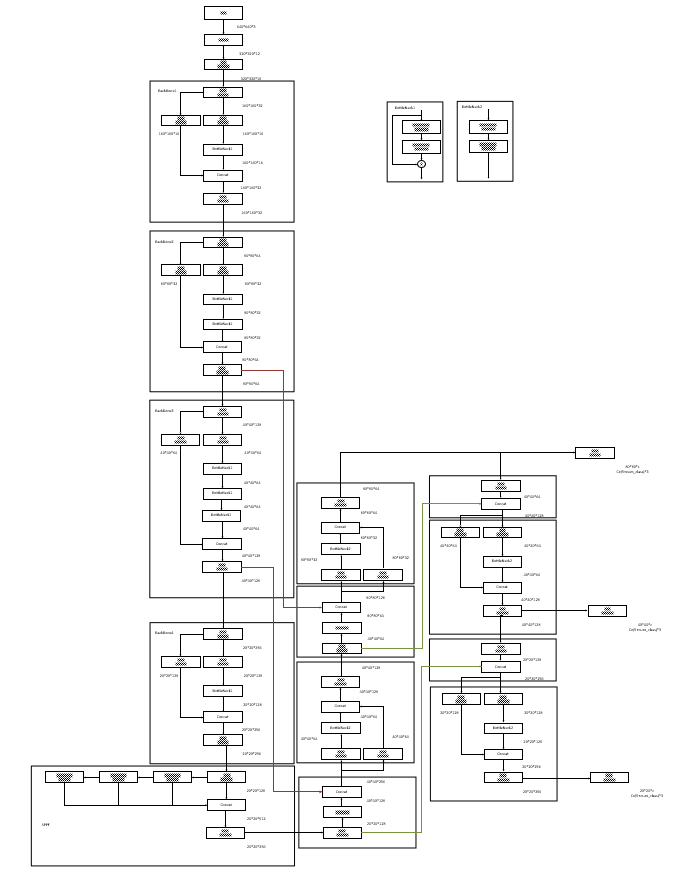

之后呢再来看一下yolov5的网络结构

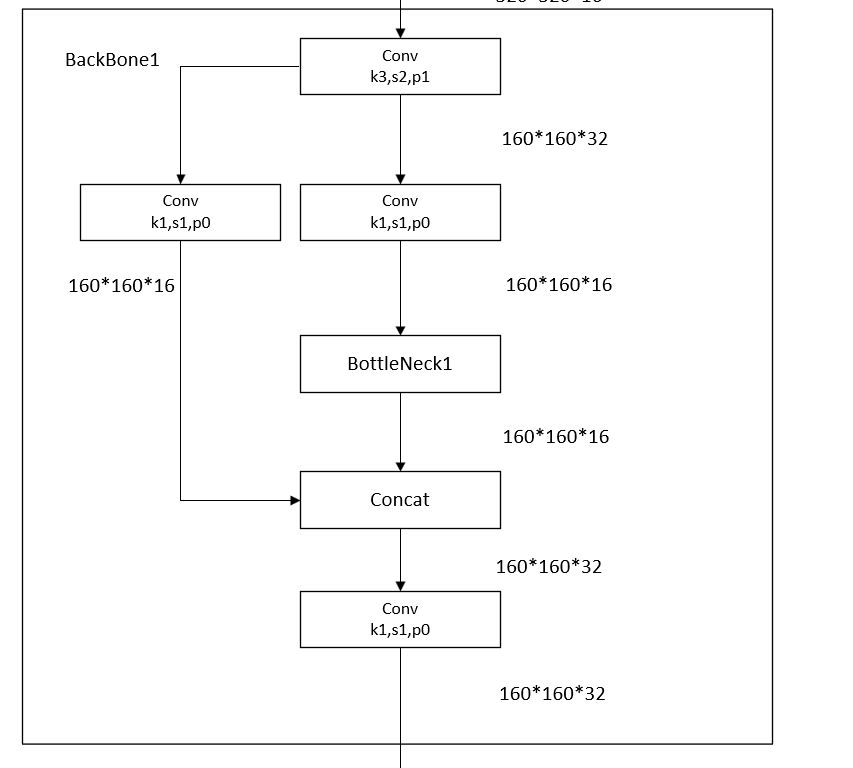

放大一个局部来看一下,可以看到就是一些卷积,cat等操作

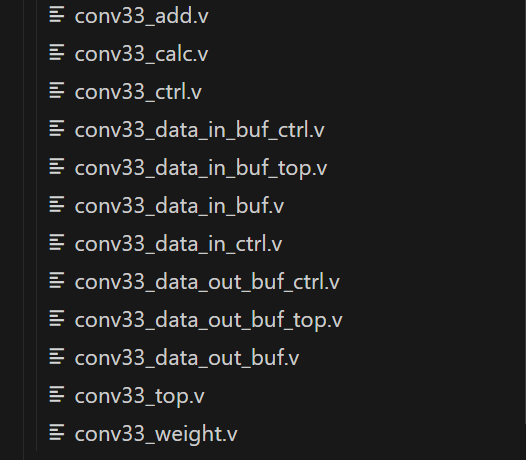

所以我们在FPGA实现的时候也是去实现这些基本的算子

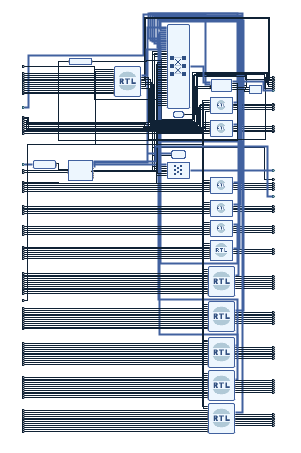

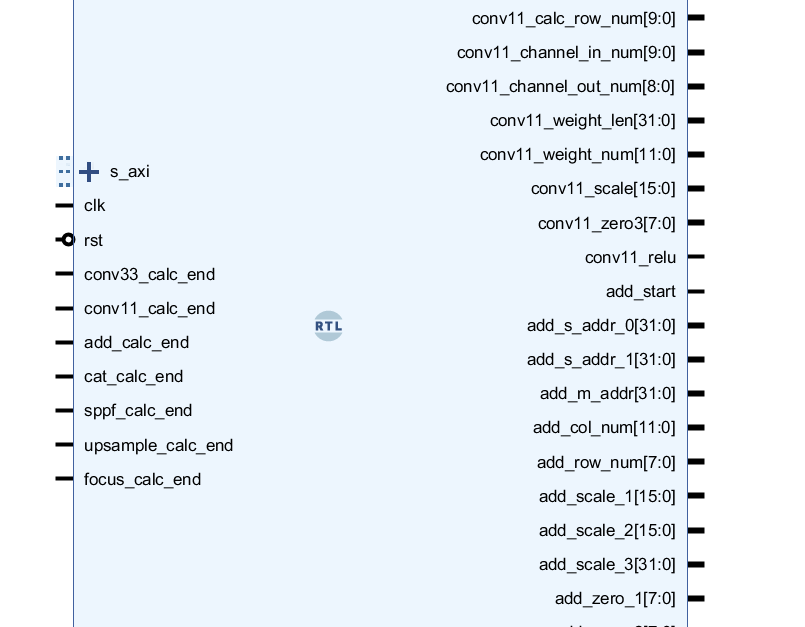

FPGA上实现的结构图如下所示

在每个算子里面都是分为in_buf,out_buf,和控制模块计算模块组成

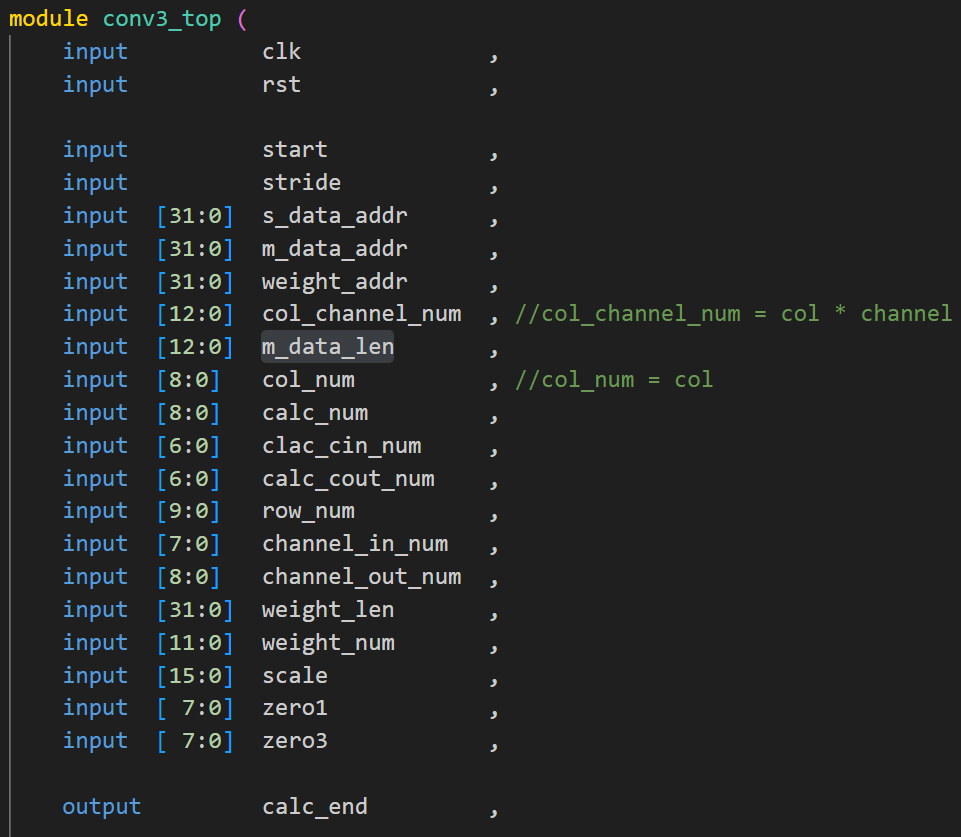

然后每个模块会有一堆的控制信号来控制整个NPU的运行

总的控制由AXI Lite逻辑组成的寄存器模块来进行控制

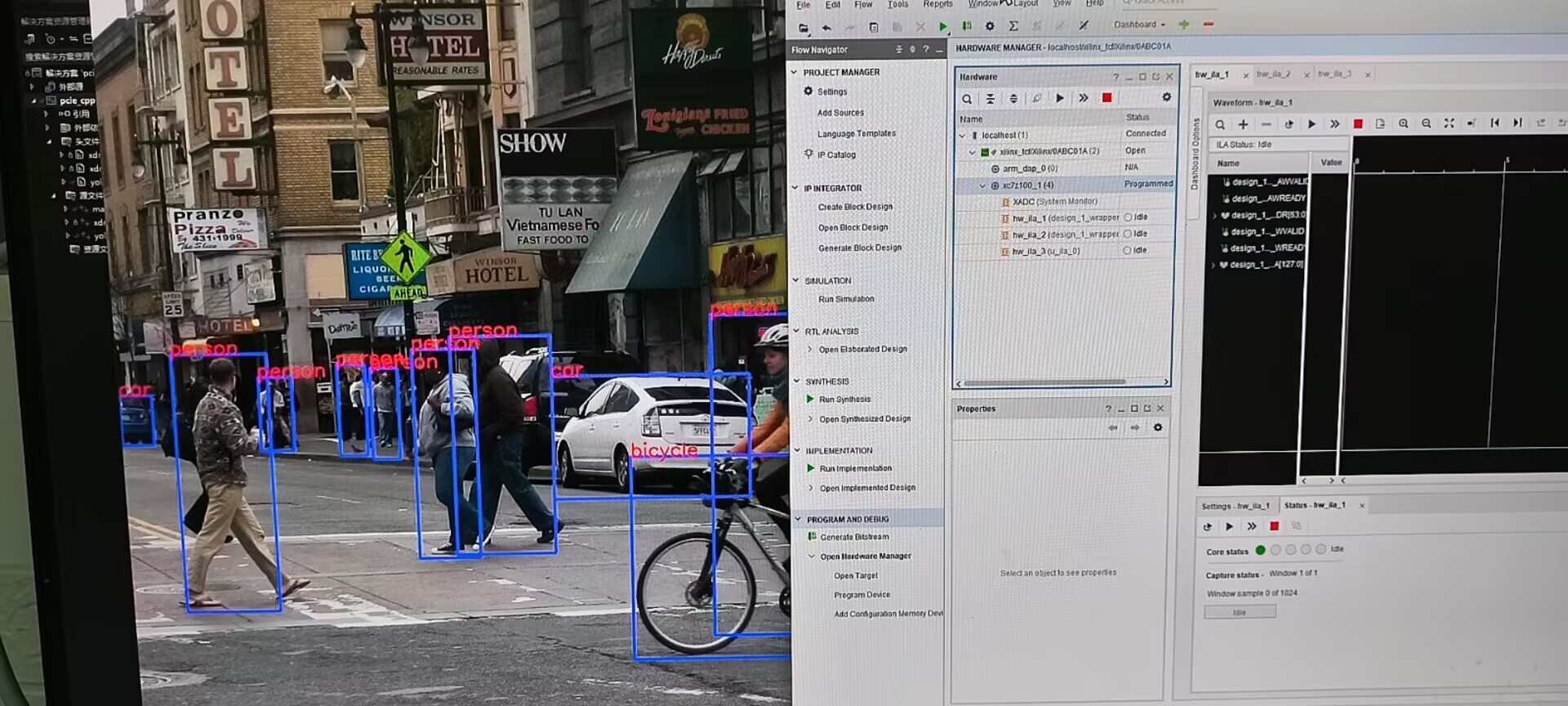

最后实现的效果如下