目录

[Vivado工具导出pin delay步骤:](#Vivado工具导出pin delay步骤:)

简介:

通过在一些等长要求比较严格的场合,会考虑到FPGA内部的走线,这时候就需要用到方法去导出fpga的pin delay。本文以xinlinx 的UltraScale系列的XCKU060-2FFVA1156I为例,手把手教你完成FPGA的pin delay导出

Vivado工具导出pin delay步骤:

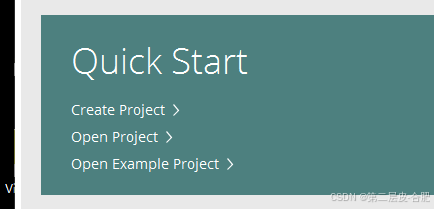

首先点击vivado工具,本文的vivado版本是Vivado2018.2

点击Create Project,新建项目

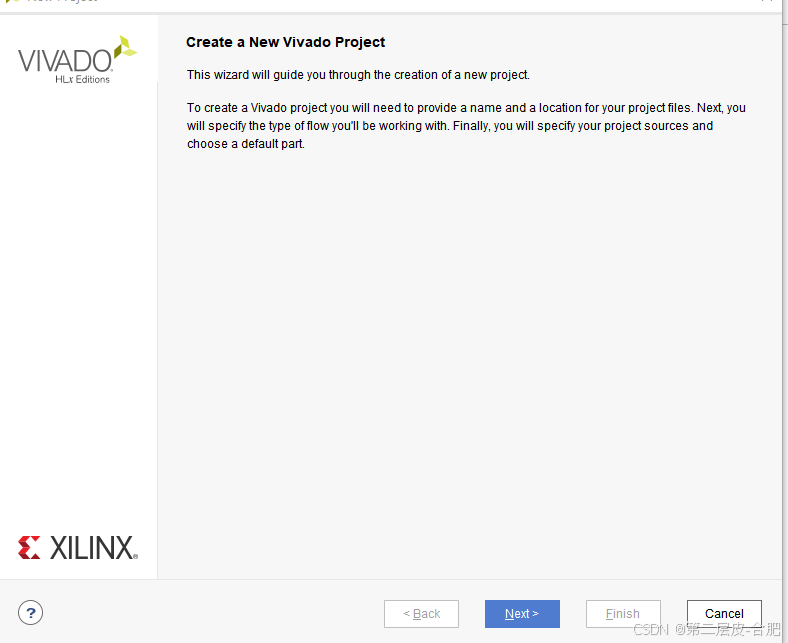

点击next

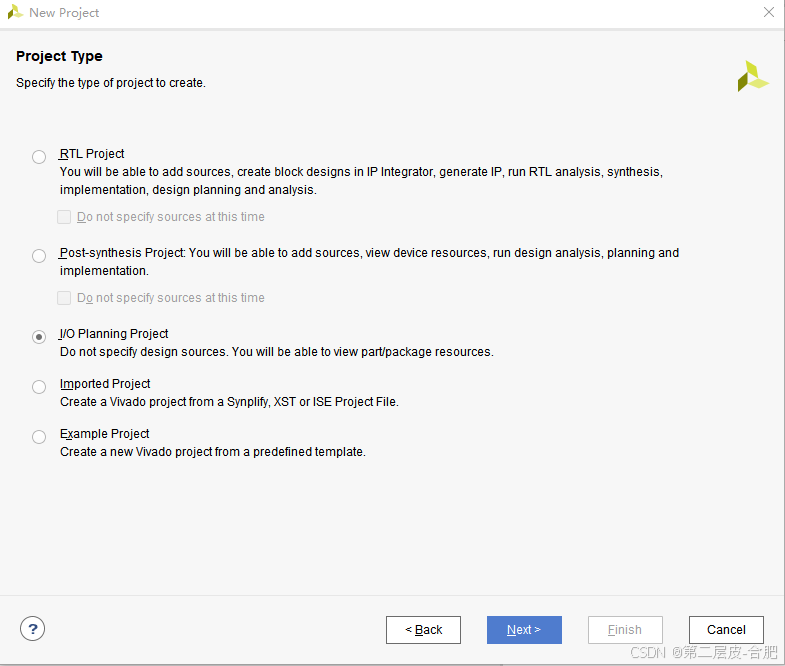

在Project TYpe这一栏配置,选择 I/O planning project

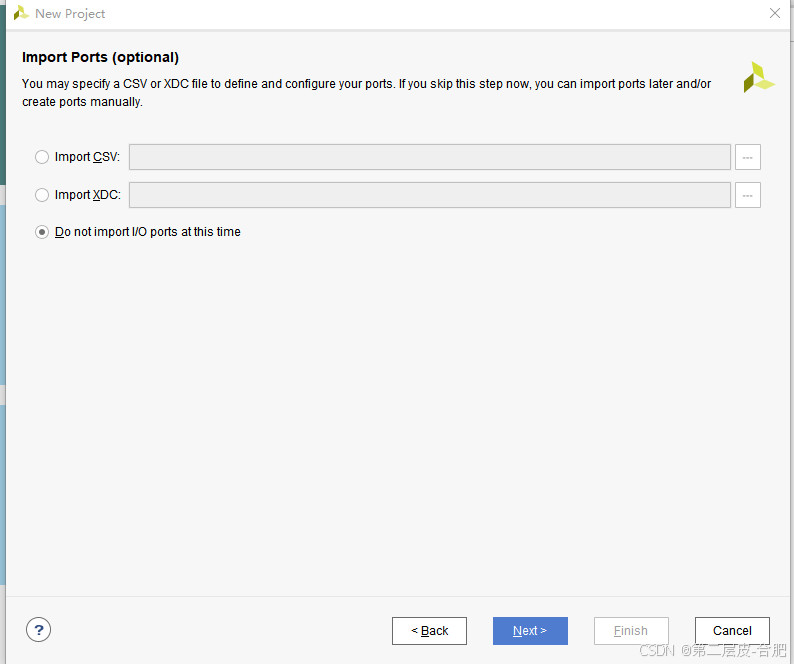

在IMPORT port这一页的配置,选择 do not import I/O ports at this time

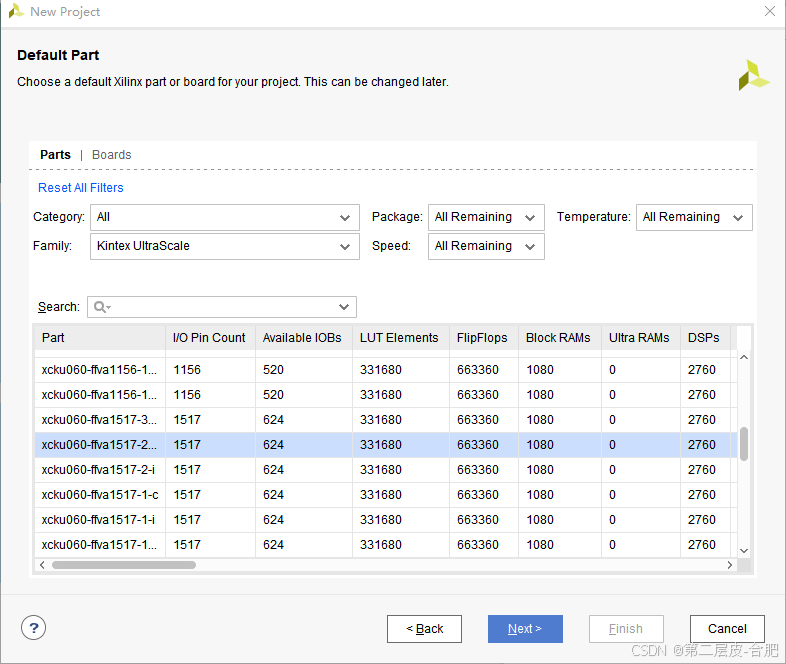

在default part 选择对应的FPGA器件型号

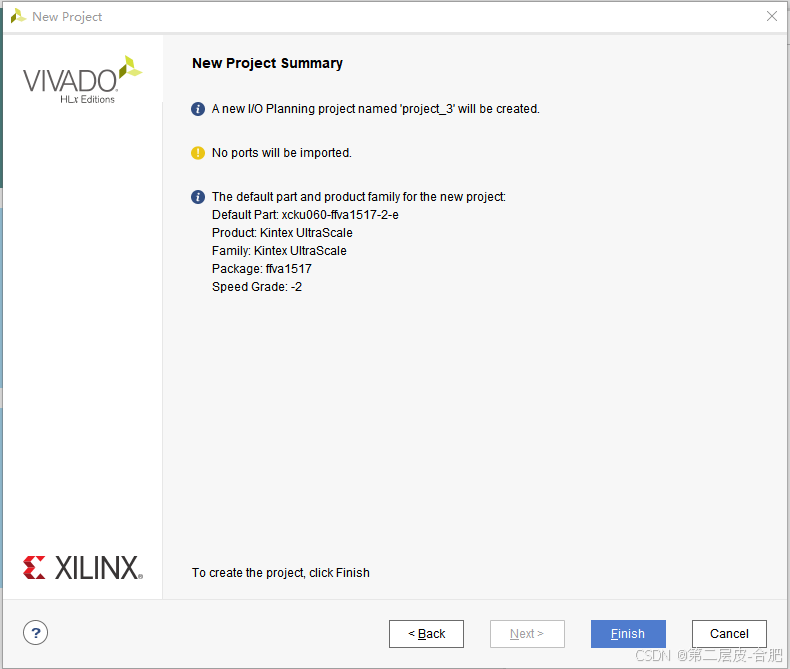

点击完成,生成IO工程

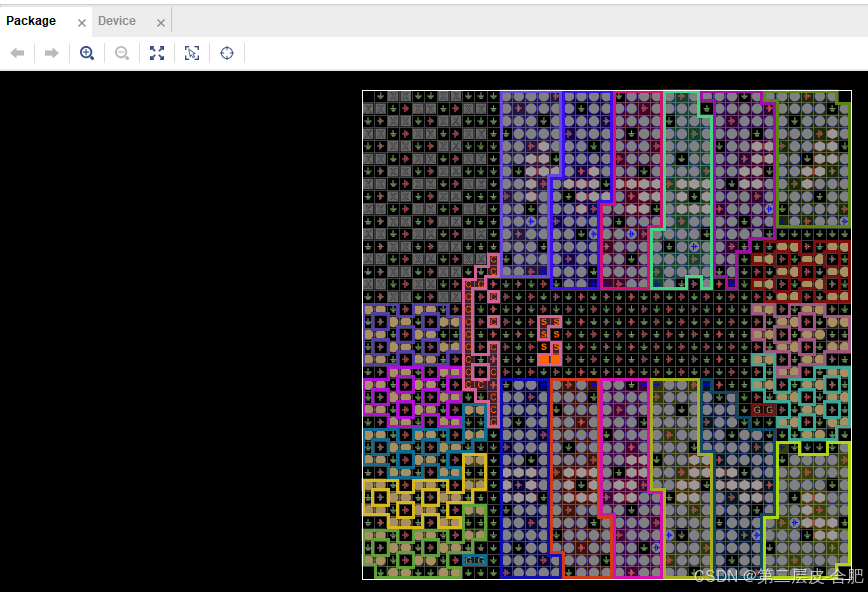

在生成的工程中,选择package这一页,点击鼠标右键,选择 export I/O ports

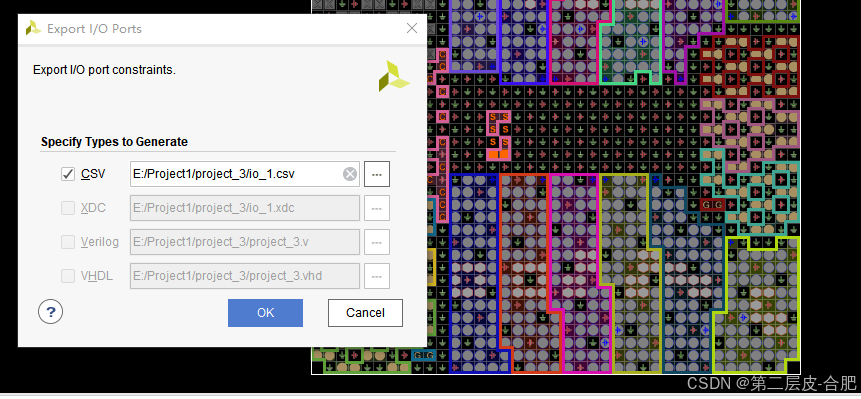

然后再弹出的菜单栏里面选择现文件的保存路径

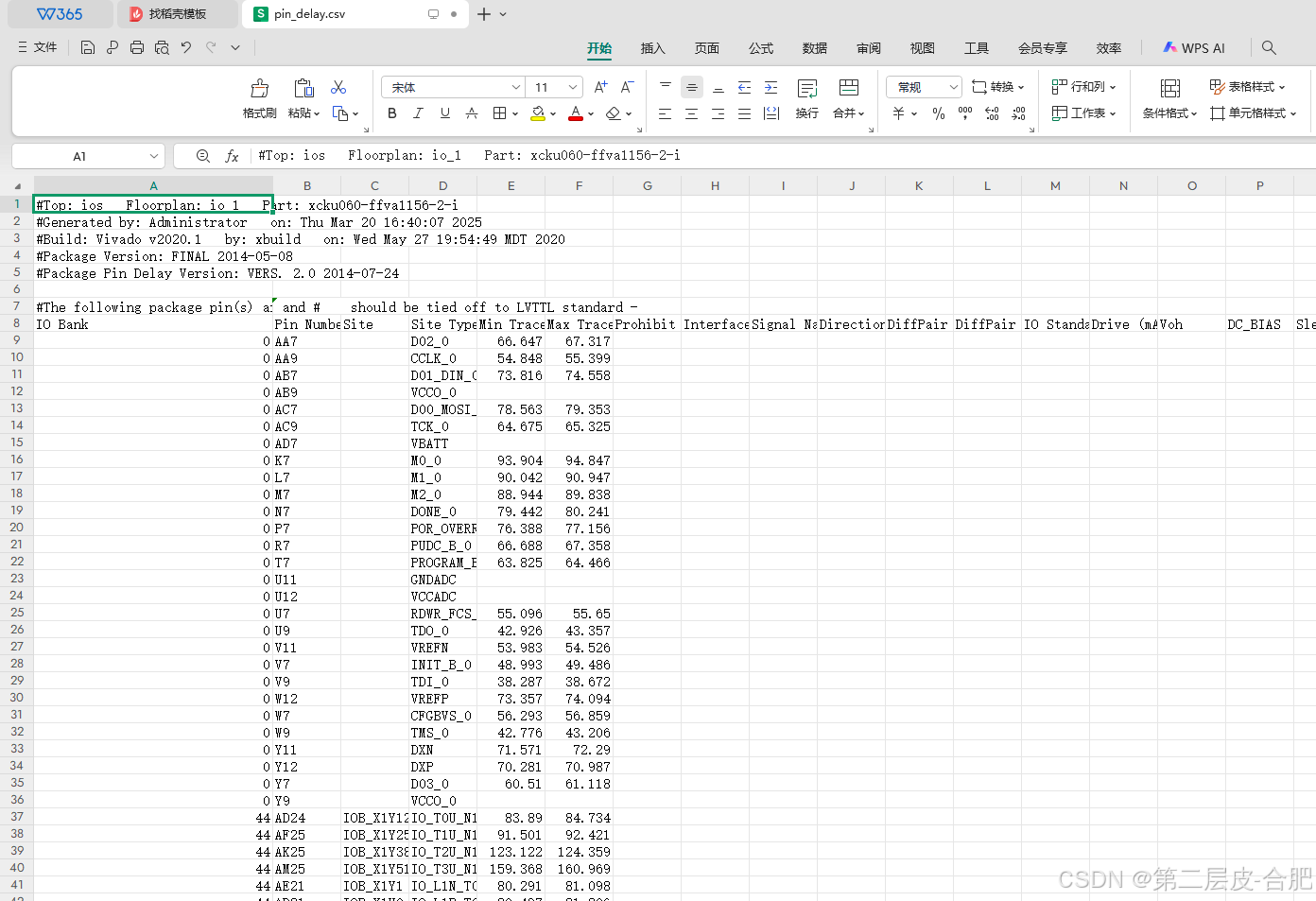

点击OK,就已经完成,然后去设置的路径下,找到响应的文件,打开如下图所示