多路选择器(MUX)简介

基本概念

多路选择器(MUX,Multiplexer)是一种多输入、单输出的组合逻辑电路。

它通过选择控制信号 ,在多个输入信号中选择一个连接到输出端。

可以理解为一个多路数字开关。

🛠 功能描述

一个 N 路输入的 MUX,有 N 个输入通道,1 个公共输出端。

控制信号(通常是 log₂(N) 位)决定了当前选通的是哪一路输入。

多路选择器可以实现信号切换、数据路由等功能,是数字系统中非常常用的模块。

在 FPGA 中的应用

多路选择器是 FPGA 内部的基础资源单元之一,广泛用于内部信号的选择与切换。

通过级联多个小型 MUX,可以轻松构建更大规模的多路选择器。

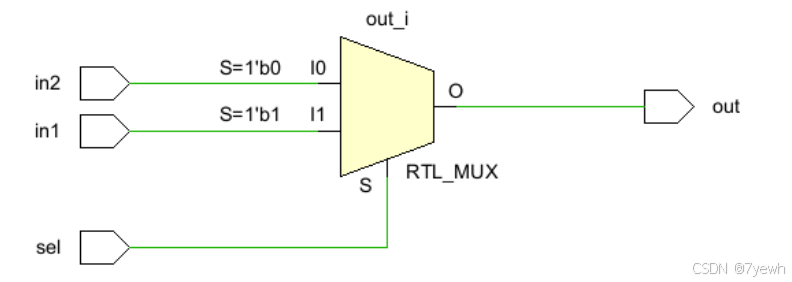

本节的实验任务是使用开发板来设计一个简单的 2 选 1 多路选择器,主要功能是通过选通控制信号 sel 确定输入信号 in1 和 in2 哪一个信号作为输出。当选通控制信号 sel 为 1 时,输出为 A 端信号;当选通控制信号 sel 为 0 时,信号输出为 B 端信号。

有两个输入信号:in1 和 in2

有一个控制信号:sel(select,选择的意思)

有一个输出信号:out

"当sel=1时,输出in1;当sel=0时,输出in2。"

assign out = sel ? in1 : in2;

always @(*) begin

if (sel)

out = in1;

else

out = in2;

end

做一个32选1多路选择器。

有32个输出口,默认都是断开的,只有一个口连接到 VCC。

用5个控制引脚 ,作为通道选择,因为 25=322^5 = 3225=32,正好能选 32 个通道。

再加 1个输入引脚(比如直接接 VCC 电源)。

控制思路是:

当选择信号是 00001(也就是十进制的 1)时,第1口输出VCC,其余口输出0。

当选择信号是 00010(也就是十进制的2)时,第2口输出VCC,其余为0。

以此类推。

| 名称 | 数量 | 说明 |

|---|---|---|

| 选择输入(select) | 5 | 控制要打通哪一个口 |

| 电源输入(VCC) | 1 | 提供需要送出的信号 |

| 输出口(out0~out31) | 32 | 连接到外部使用,每次只有一个输出有效 |

module mux32_out(

input wire [4:0] sel, // 5位选择信号

input wire vcc_in, // VCC输入

output wire [31:0] out // 32路输出

);

// 全部输出初始化为0,只有选中的那一路为vcc_in

assign out = (vcc_in) ? (32'b1 << sel) : 32'b0;

endmodule

module mux32_out_auto(

input wire clk, // 系统时钟(比如50MHz)

input wire rst_n, // 系统复位,低有效

input wire vcc_in, // VCC输入(固定高电平)

output wire [31:0] out // 32路输出

);

reg [4:0] sel; // 选择信号

// --- 选择器逻辑 ---

assign out = (vcc_in) ? (32'b1 << sel) : 32'b0;

// --- 选择器自动增加逻辑 ---

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

sel <= 5'd0; // 复位时回到0

else

sel <= (sel == 5'd31) ? 5'd0 : sel + 1'b1; // 达到31时回0,否则加1

end

endmodule