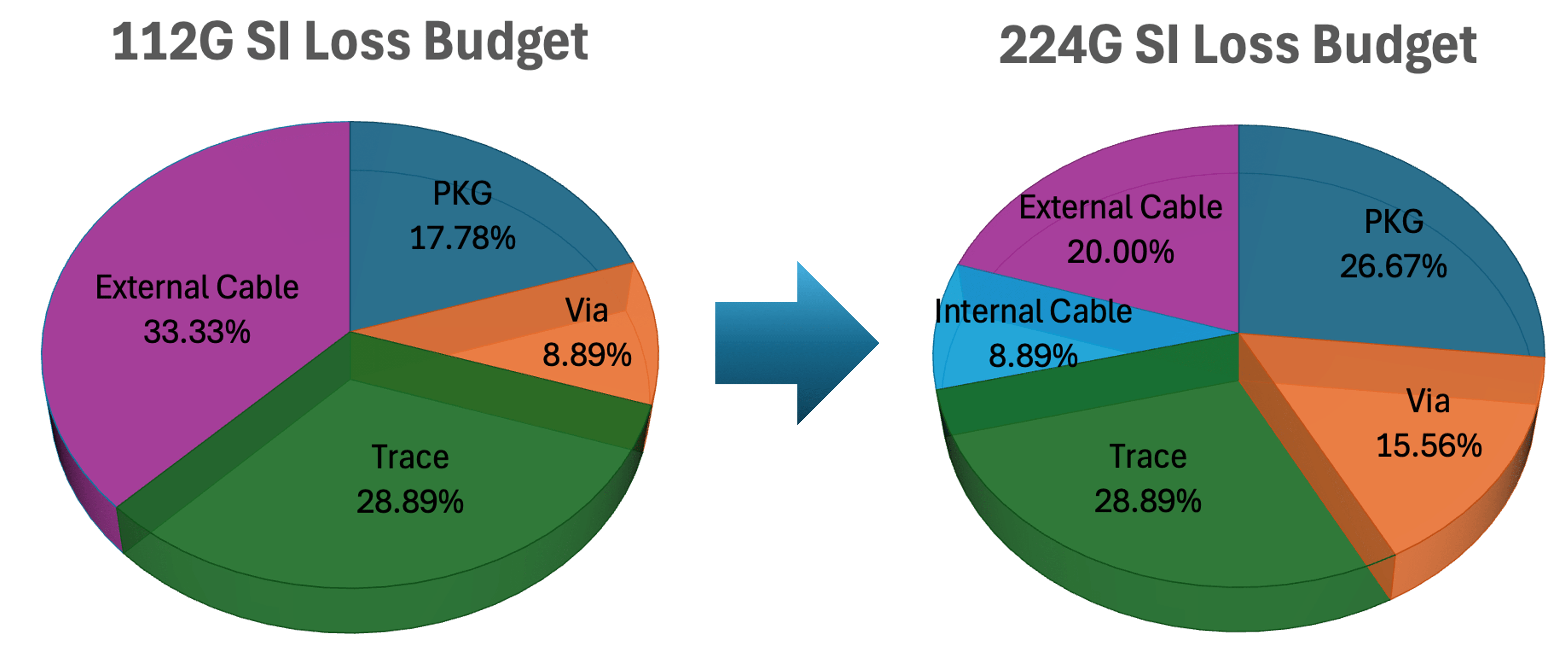

在AI驱动的时代,系统设计已经从单一PCB的视角,逐步转向以整个rack为单位来考量。 对于信号完整性而言,焦点以不再局限于单一PCB上的损耗,而是扩展到芯片与芯片之间的端到端互连损耗(end-to-end interconnect loss)。 这种转变反映了现代高性能系统设计的新需求与挑战,也让互连损耗成为设计者无法忽视的核心课题。

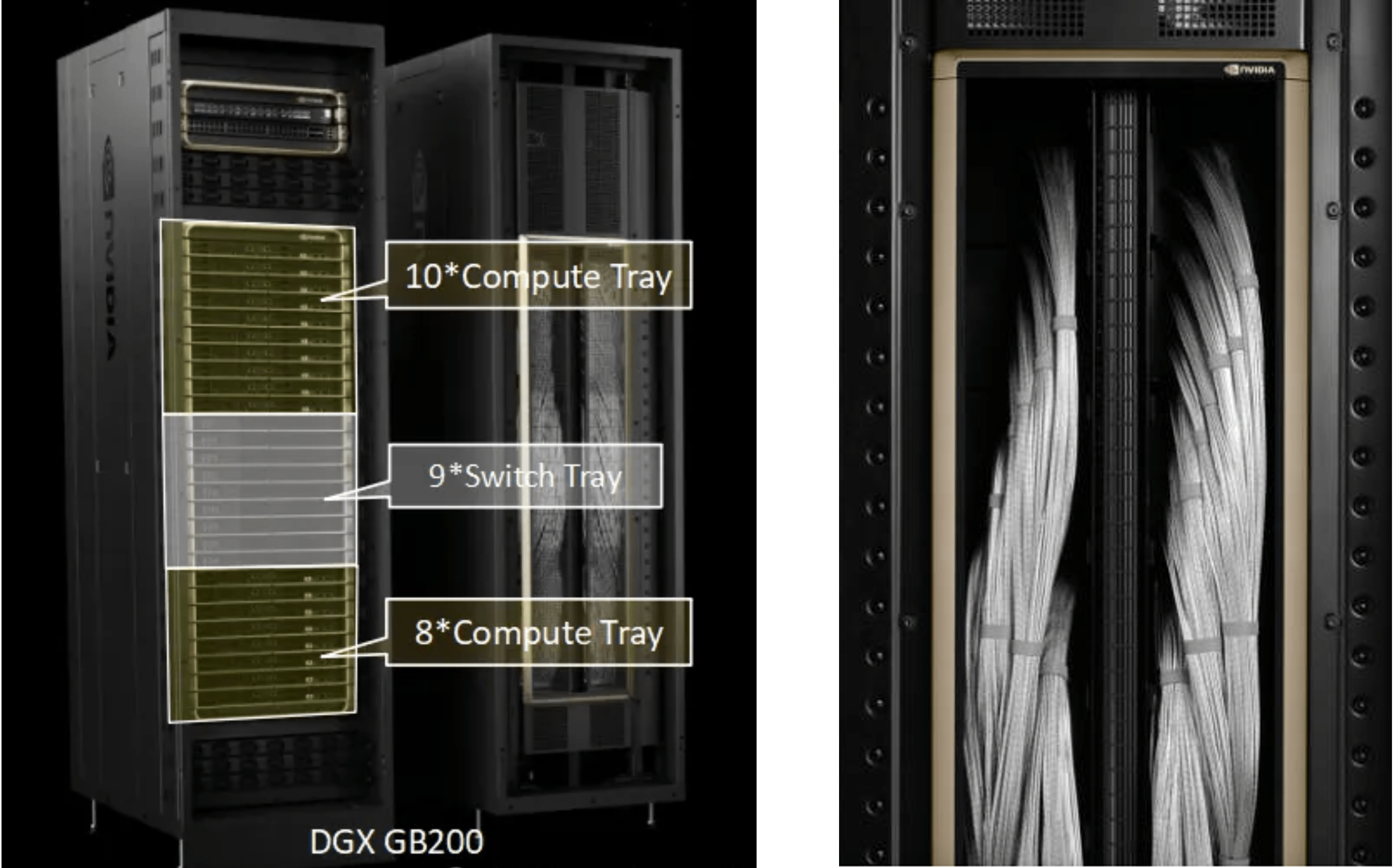

比如最近大家一直在关注的GB200,Compute Tray即透过Cable Cartridge与Switch Tray高速连通,这种End-End loss(Blackwell to NVswitch)大概落在40~45dB,也是目前SerDes做Equalization的上限。

晶片到芯片的互连损耗可以细分为以下三个主要部分,每一部分都对整体系统性能产生重要影响:

1. 封装载板与PCB损耗

载板与PCB损耗这部分是整体讯号互连损耗的重要组成,主要包括以下几个方面:

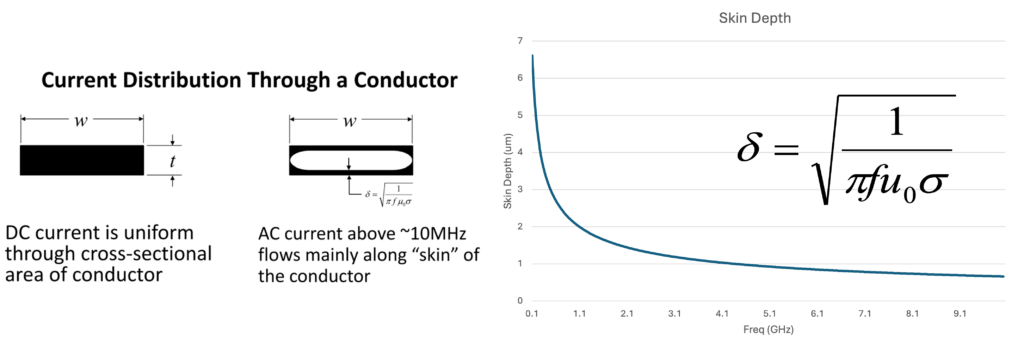

金属损耗

金属损耗主要分成金属(通常是铜)本身的电阻效应 以及表面粗糙度!

铜箔电阻损耗

PCB上绝大多数的金属是铜,本身就带有些许电阻,低频时电流较为平均分布在铜箔内部,损耗较小; 高频时会有集肤效应,电流会分布在铜箔表面,电流截面积下降,导致高频电阻升高的情况下高频时损耗会上升。

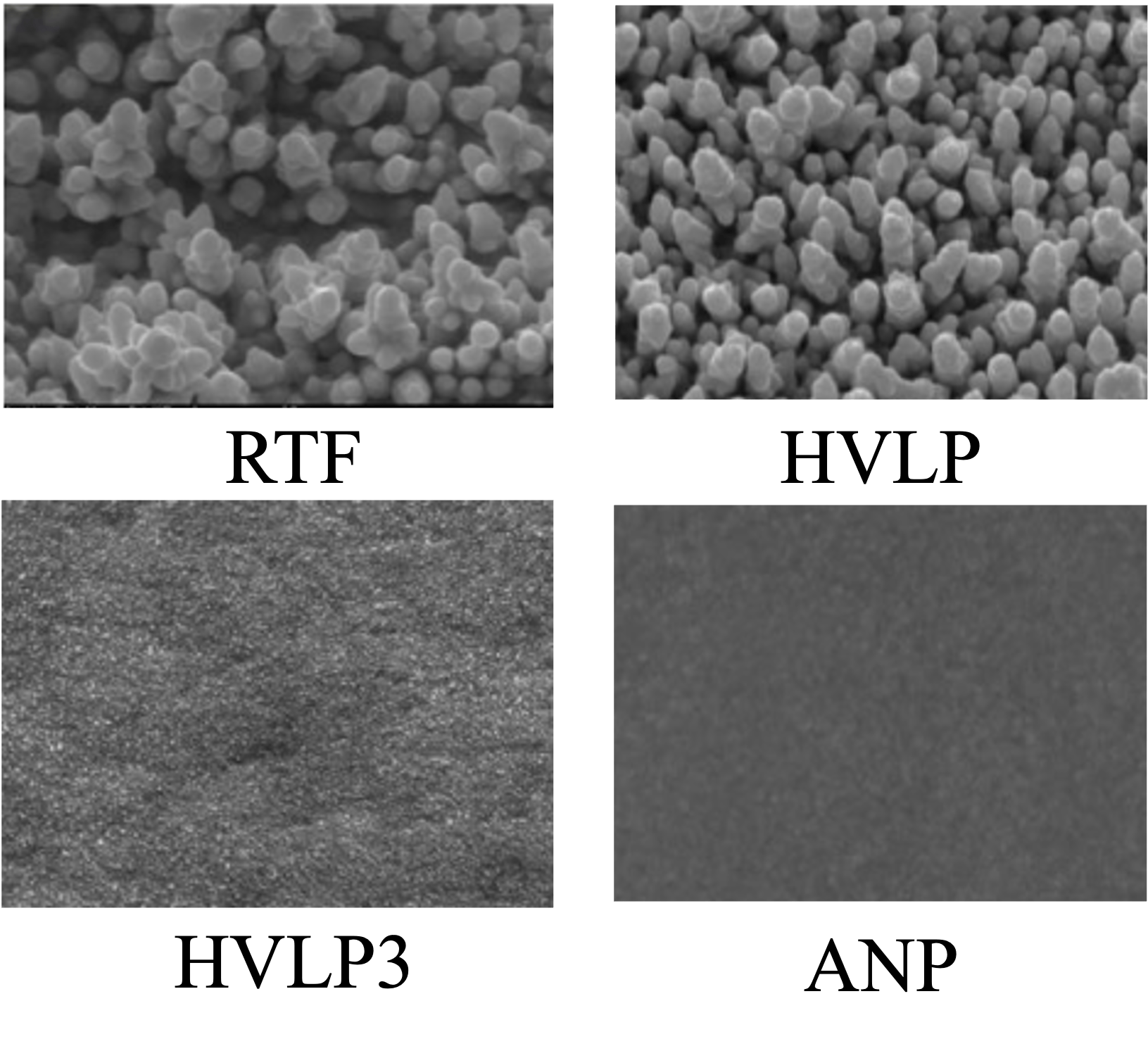

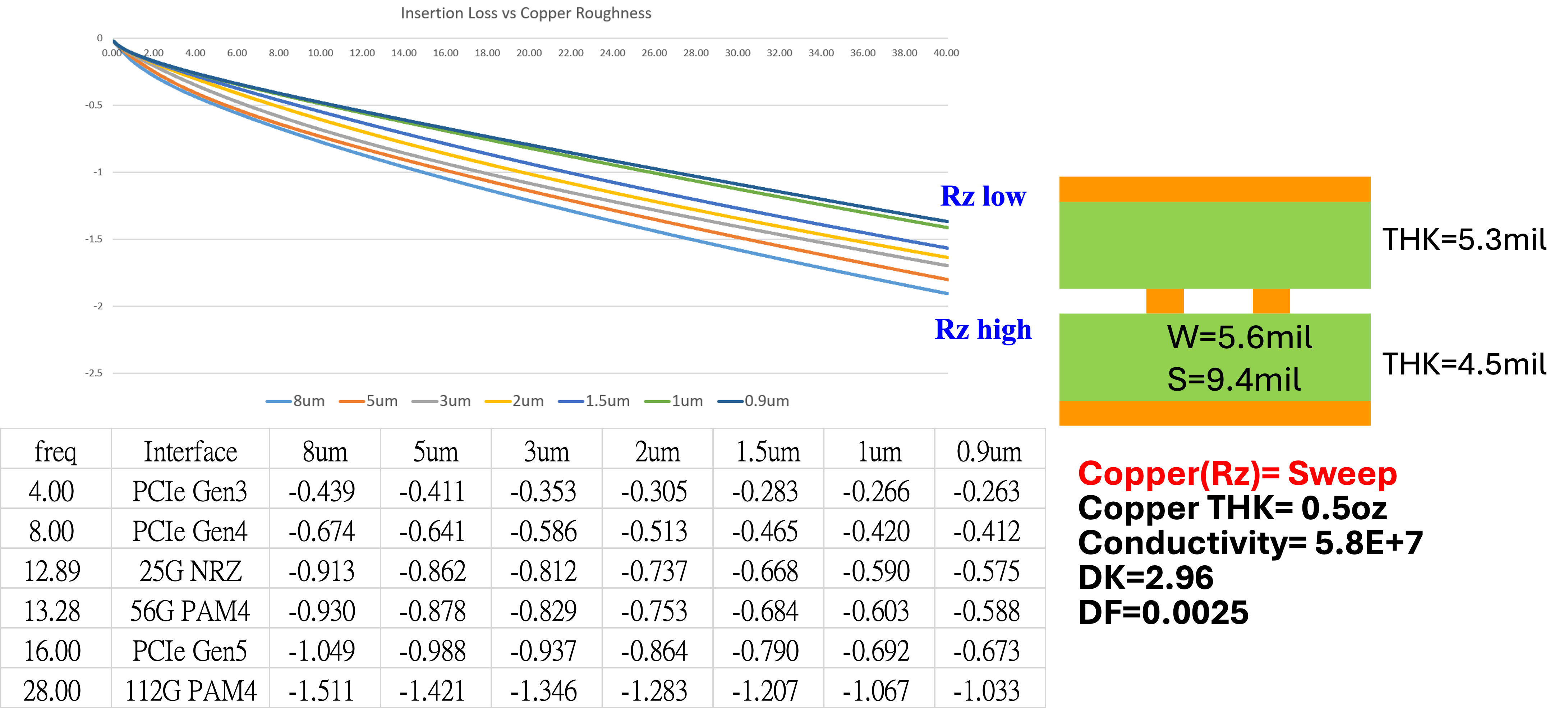

表面粗糙度

再加上PCB铜箔的表面不会是一个完整的平面,微观来讲可以看到些许的颗粒,铜箔的这些颗粒会增加其与树脂的表面接触面积,使其结合强度变高,铜皮会较不易脱落,不过在高频时的损耗会急剧增加!

透过改善铜皮的表面粗糙的行为,可以改善表面粗糙度,通常以Ra或是Rz呈现,对SI工程师而言,我们较常关心的是Rz。 而依不同铜皮的表现又分成不同等级,其中有RTF(Reverse Treated Foil)、VLP(Very Low-Profile)、HVLP(Highly Very Low-Profile)、ANP(Any No-Profile)等等。

目前产业界最高档的铜箔是HVLP5,几乎已经是没有任何的Rz,可以将表面粗糙度降低许多! 不过CCL与PCB厂还在努力克服没有颗粒的铜箔对于材料拉力(Peeling)的影响,预计今年(Y2025)会有好消息。

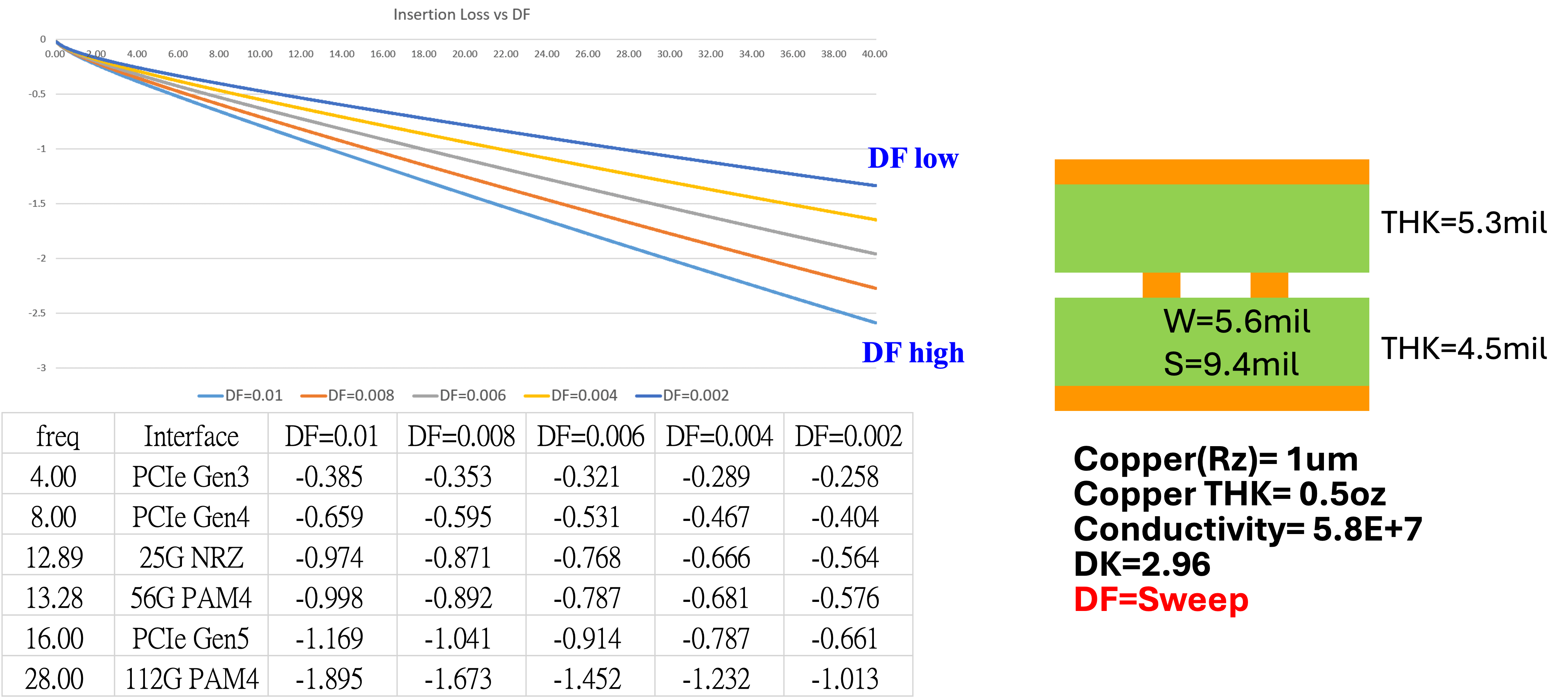

介质损耗

PCB介质有所谓的损耗正切参数(Loss Tangent)或是所谓DF(Dissipation Factor),这两者指的是同一件事,代表材料在高频信号通过时,会有多少能量损耗(消耗成热能等)。

从电磁学的角度,介电材料会有「实部 \( \mathrm{Re}(\varepsilon) \)」与「虚部 \( \mathrm{Im}(\varepsilon) \)」的介电常数:

• 实部代表电场储存能量的能力;

• 虚部代表材料吸收并转换这些能量的损耗能力。

而 DF可以写成:

tan(δ)≈Im(ε)Re(ε)

这里 \( \delta \) 是介电损耗角。 数值越大,表示「虚部」在整个介电常数所占比重越高,也就是介质损耗越显著。

来个比喻:我们可以将介质损耗则可以比拟为水流过程中管壁吸收能量、造成水流衰减的效果。 若管壁很粗糙、吸水量大(损耗大),水流一路过去就会衰减得很厉害; 反之,若管壁光滑且不吸水(损耗小),水能保有更多原本的流量与压力。

辐射损耗

将输出信号电压扣除信号的反射与系统内的损耗后,剩余的能量可以视为辐射信号。 辐射讯号实际上是一种损耗,因为这些能量会直接散布到环境中。 然而,从系统SI的角度来看,我们通常不特别关注这部分损耗。 原因在于,只要系统的阻抗设计得当,辐射能量通常会被控制在非常小的范围内,对整体性能的影响可以忽略不计。

\( \text{Radiation Loss} \; =\; 1 \; -\; |S_{11}|^2 \; -\; |S_{21}|^2 \)

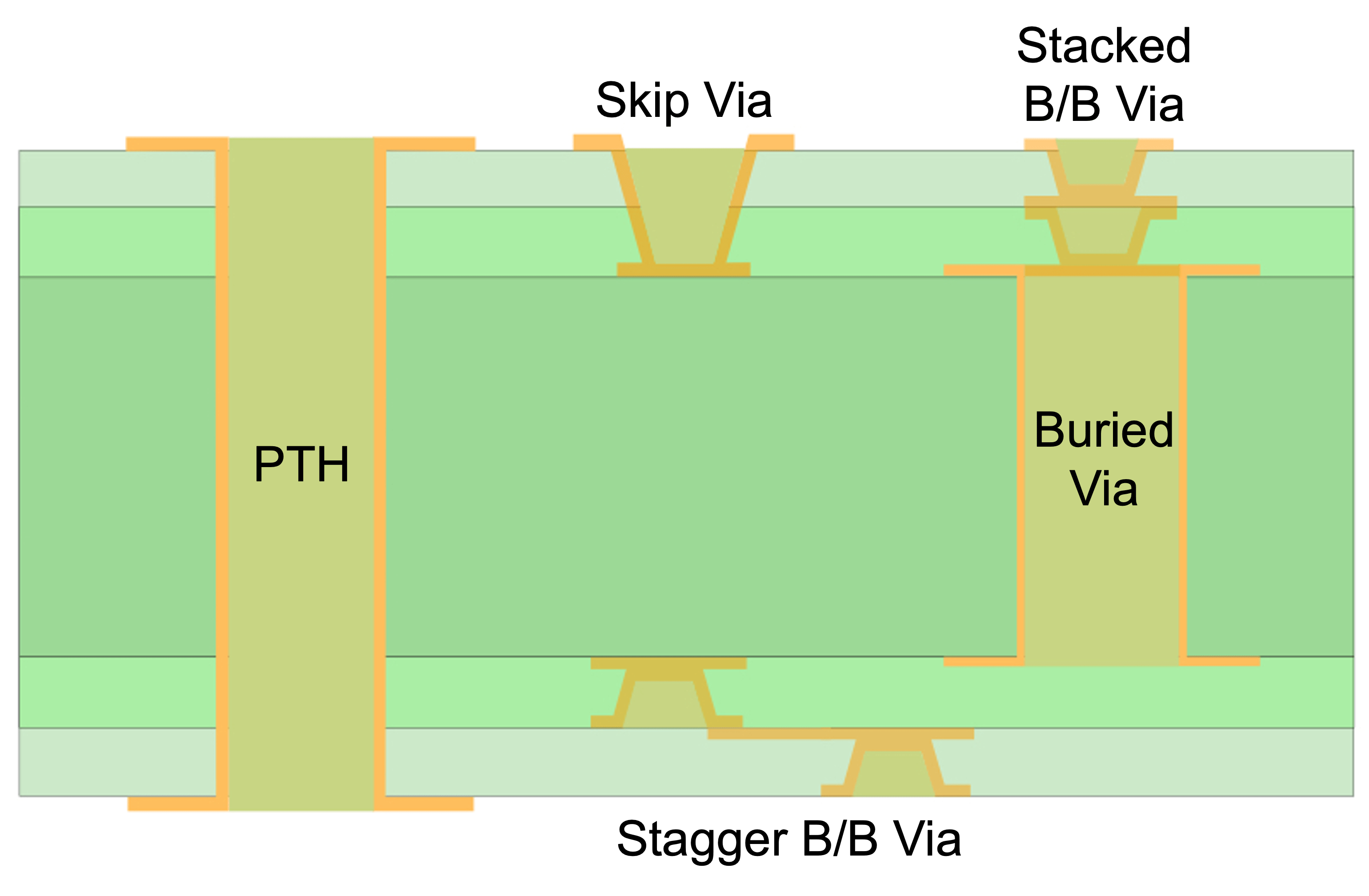

镀穿孔与雷射孔

在PCB设计中,我们习惯将互连(Interconnect)分为2D与3D走线两类。 2D走线 通常指的是传输线,这些线路可以使用2D软件进行高效的模型化,例如 Keysight ADS 的 CILD 模块或常见的 Polar 软件,都能很好地处理这类结构。 而3D结构则包括镀穿孔(Plating Through Hole, PTH)与激光孔(Laser Via),这些结构需要借助3D电磁场模拟软件来建模,如 Cadence 的 Clarity 或 Ansys 的 HFSS。 相较于2D软件,3D模拟的分析时间更长,对技术要求也更高,并且需要较长的学习与建模周期,才能确保模型与软件设定的准确性。

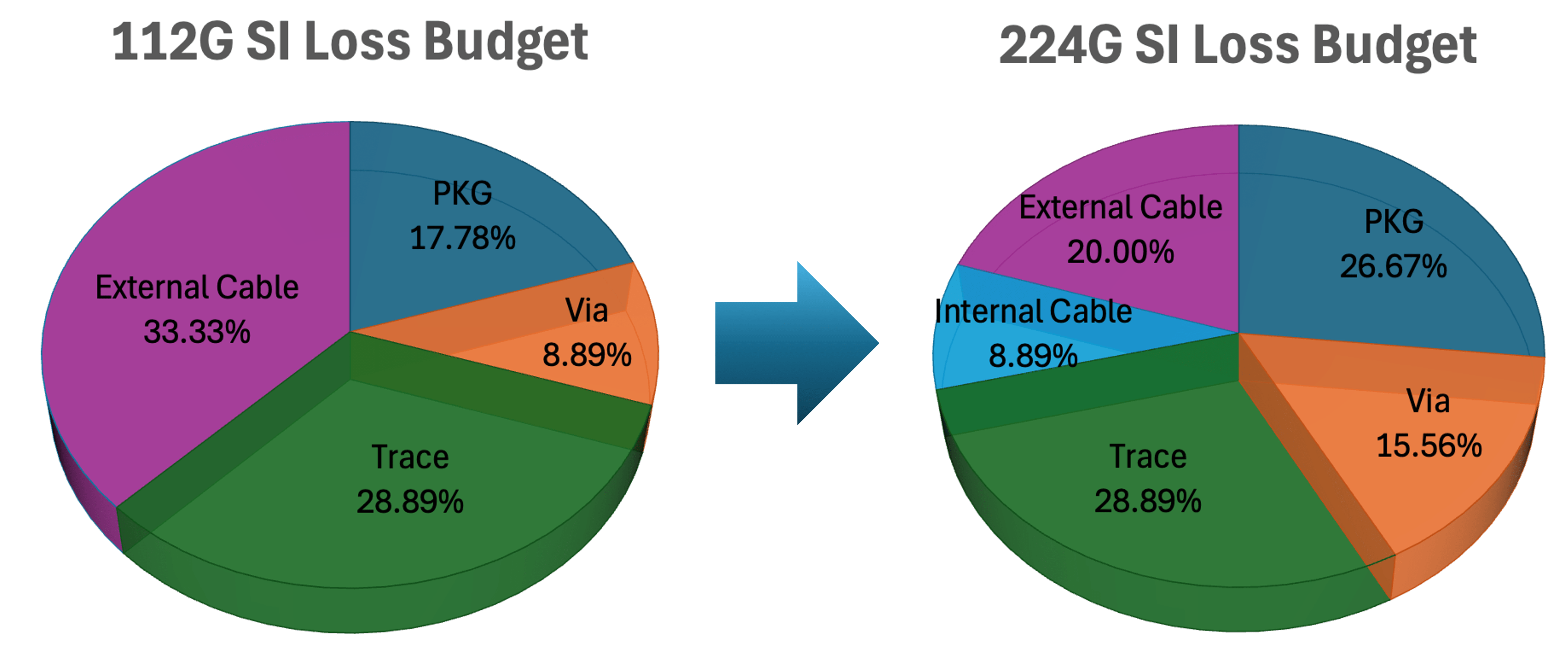

随着产业迈向 224G-PAM4 的时代,Via 已成为设计中无法忽略的关键因素。 由于服务器或交换机主板的厚度不断增加(目前厚度即将超过6mm),Via的长度也随之变长。 同时,频率已攀升至53GHz,在这样的条件下,单一Via的损耗可能高达1.5dB至2dB ,所有Via的损耗就占掉了整个通道损耗的**15%**左右。 更为关键的是,在目前PCB材料升级受限的情况下,Via所带来的损耗显得格外突出,对整体通道性能的影响不容忽视。 (P.S. 所有Cable损耗均包含与其连接的Connector损耗)

2. 连接器损耗

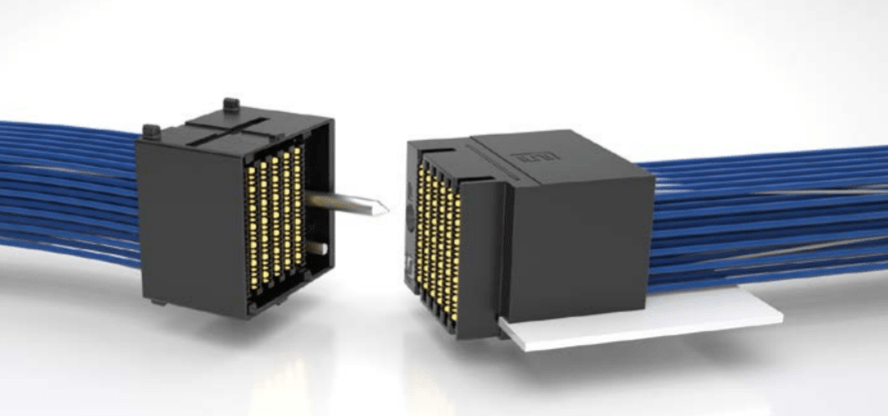

开头已经提到,现今的AI system是不同机柜间的连结,讯号路径上会有许多的连接器,例如GB200的Compute Tray对外就有一个Backplane连接器跟Cable cartridge对接,再利用铜缆线接到Switch Tray。 (图为Samtec的Backplane连接器,或称BP Connector)

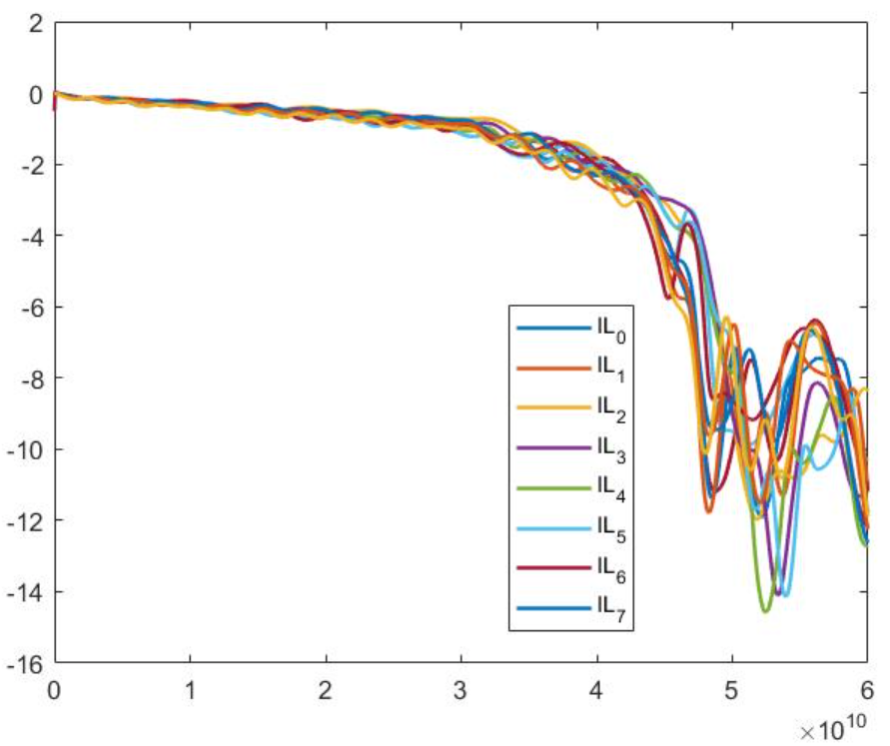

这些连接器是3D的架构,设计上很仰赖3D建模的技术,且与PCB via类似,缺乏完整的reference plane,因此连接器的高频特性不容易控制,从图可以看到高频损耗抖动的非常严重! 最好的做法就是做的精小,可是会遇到机械结构较为薄弱,焊接或是组装不良的议题,相当不好搞!

3. 铜缆损耗

以现在的AI system来说,这部分又分成两种

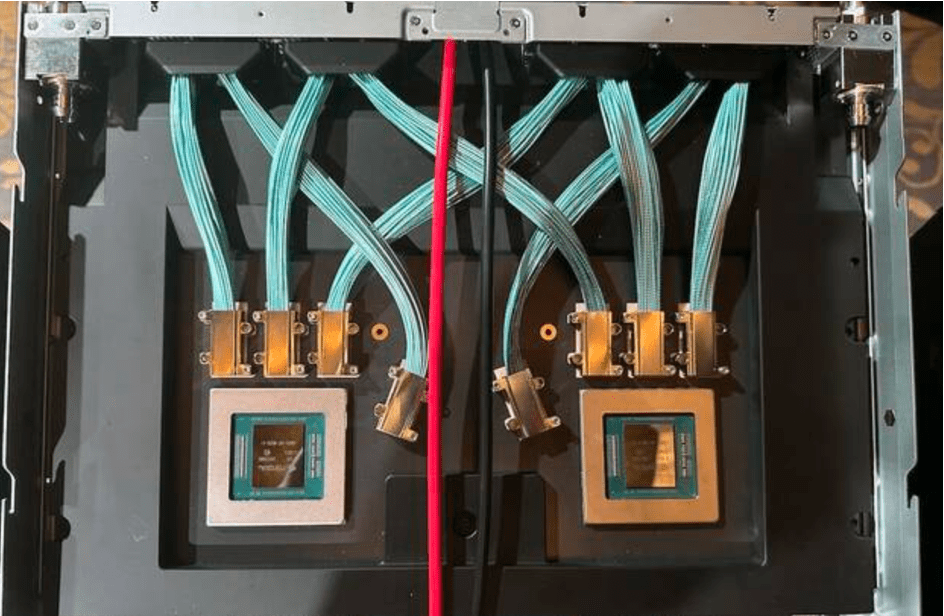

- 内部飞线(Internal Flyover Cable):例如GB200的Switch Tray内部即是用这种Amphenol的飞线。

- 外部系统间连接(External Cable):例如交换机网络对连需要用到的DAC cable(Direct-Access Cable)或是类似GB200 Compute Tray与Switch Tray外部的Cable,都是属于这类型的外部连接媒介。

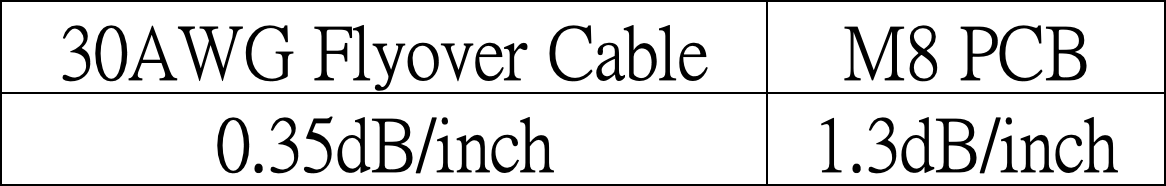

因为Cable具有稳定的阻抗特性、良好的reference path以及较低的材料DF,所以比PCB CCL材料的损耗还来的小很多。 对比M8等级的材料来看(例如台光电的EM892K+HVLP4铜箔),在224G-PAM4的应用上,30AWG的Cable的损耗大约是0.35dB/inch而PCB的损耗大约是1.3dB/inch,两者差别极大!

然而没有这么美好的事情,有好就有坏,用Cable会有几个Trade-off:

-

成本较高:Cable本身就已经很贵了,还需要加上连接Cable的连接器的成本,所以使用内部 Cable的机台成本都较高。

-

**散热问题:**因为需要内部连接器组装Cable,这些连接器会有一定的高度(通常20mm),这会影响内部的风流,使得ASIC或是GPU的散热效果变差。 当然如果走水冷(Liquid Cooling),可能是比较没差?

-

组装与维修:多了内部连接器,对于系统组装一定会有所影响,毕竟多了一道工序。 且这种连接器为了做在内部,会比较精小,所以机械强度比较弱,很容易掉件,且维修时整台机台都需要开盖检查,较为麻烦!

-

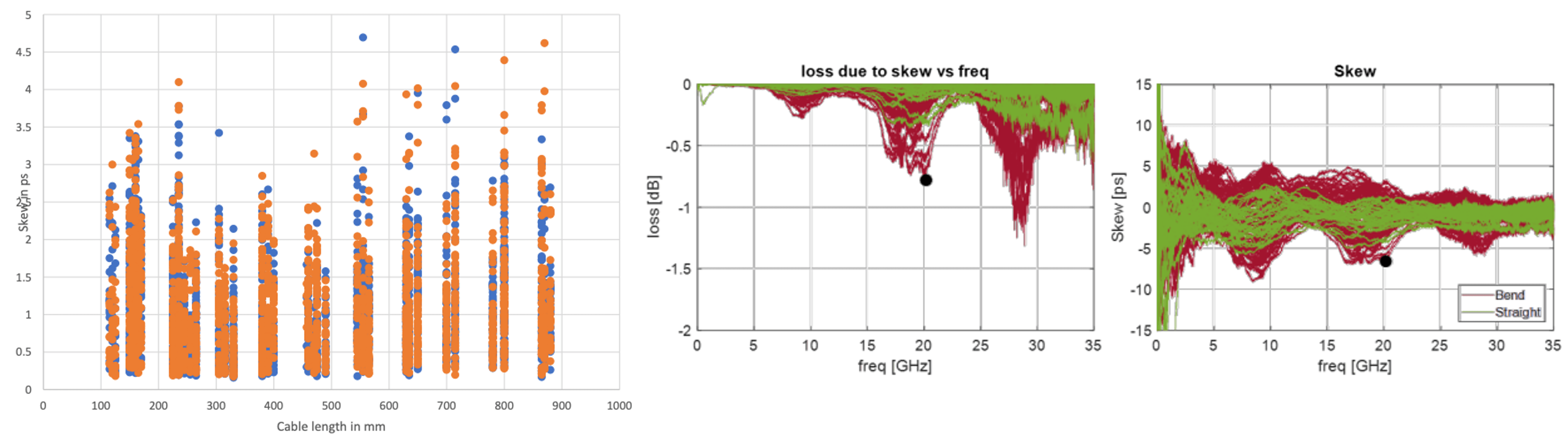

模态转换损耗:Cable结构的不均匀性(P/N Skew)会引发额外的模态转换损耗(Mode Conversion Loss),这个损耗随着数据传输速度越来越快而越难被忽视,这不只牵扯到Cable本身制造上的稳定度,还得分析当Cable转折时是否会影响到差动对两条线的均匀性, 抑或是Cable与Connector在焊接过程中的不匹配性,相当地复杂!

总结

随着数据传输速度不断提升,对损耗的要求也越来越严苛,讯号完整性的重要性日益凸显! 这不仅仅是对SI工程师的专业要求,从业人士也需要具备基础的理解能力。 无论是如何解读供应商提供的损耗规格,还是熟悉零组件的技术迭代,这些都成为不可或缺的能力。 此外,能够凭借专业知识提出针对性问题,例如询问Cable的P/N Skew等被设计「包装」的细节,也是未来工作的核心能力之一。

未来,我们将有机会逐一剖析如何有效控制与设计这些损耗,敬请期待!