DDR4控制器一般采用自带的MIG控制器,用户控制主要是基于MIG IP核进行设计

实际工程项目中可能只挂载了一组DDR,但是用户数据可能有很多种,用户通过给每种数据划分特定地址进行存储,如何实现灵活管理成为设计的关键

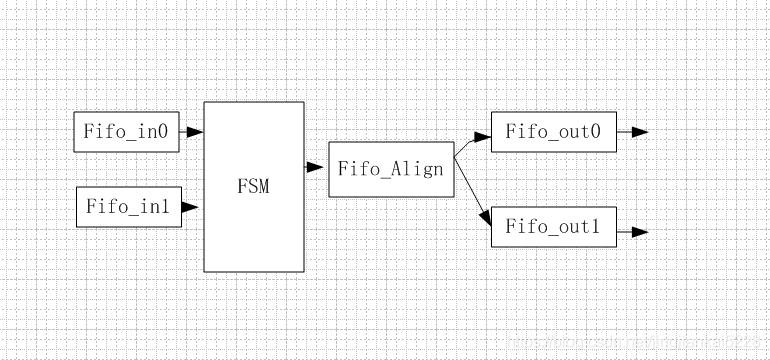

为了方便后端数据分流,可以通过缓存FIFO进行数据分流处理,示意图如下图所示,从FIFO_in0进入的数据最终输出到FIFO_out0通道,这样前端数据可以同时到达,只要数据的总带宽不大于DDR4的理论带宽,就不会发生数据丢失,从宏观上看,DDR4是可以完成读写同时的,只要用户数据不够突发长度,即可发起DDR4的读操作

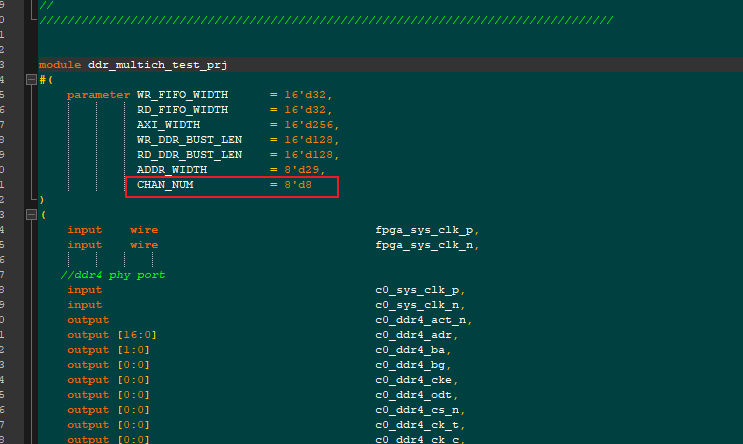

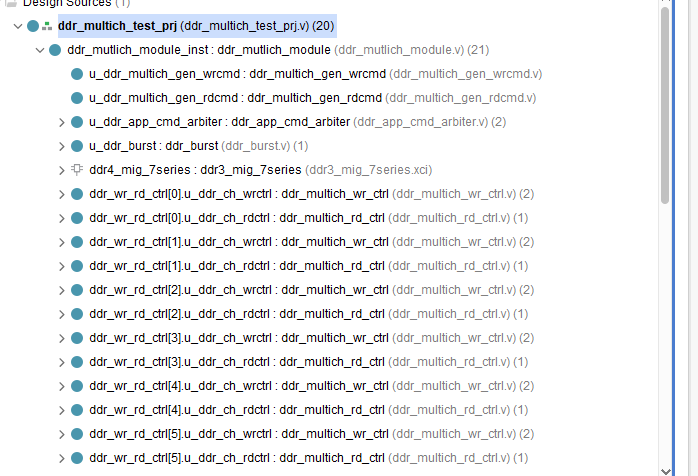

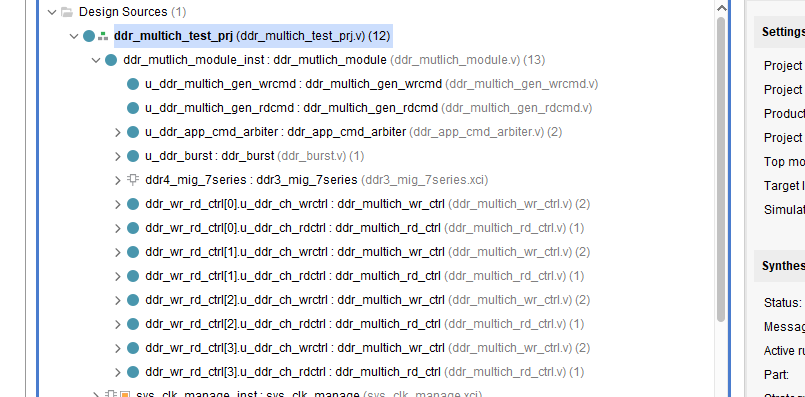

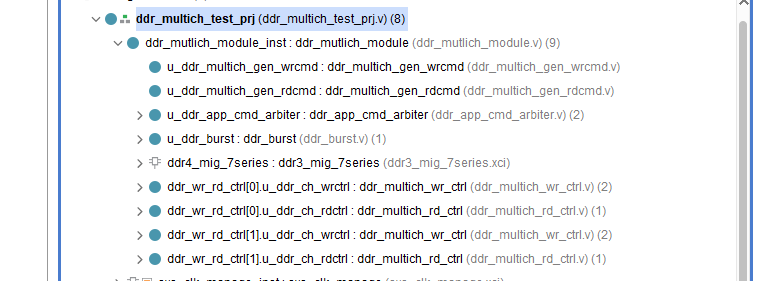

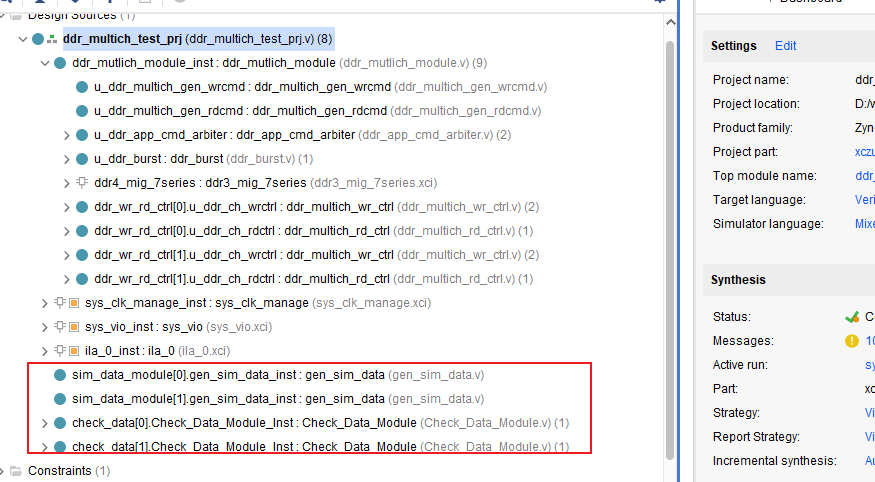

程序设计过程中,为了随意裁剪通道数,尽量采用generate例化方式

通过parameter决定实际使用的通道数

上图为8通道例化

4通道例化

上图为2通道例化模式

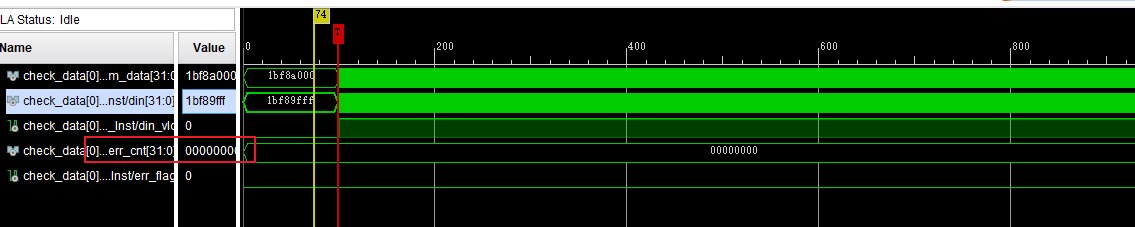

测试过程通过产生一个递增数,然后输出添加对应的校验模块

实际测试

通过统计错误数据个数,监测内部数据有无读写错误

测试下来DDR4的读写同时效率基本可以保证在75%左右