参考视频:

数字IC,FPGA秋招【单bit信号的CDC跨时钟域处理手撕代码合集】_哔哩哔哩_bilibili

一、亚稳态

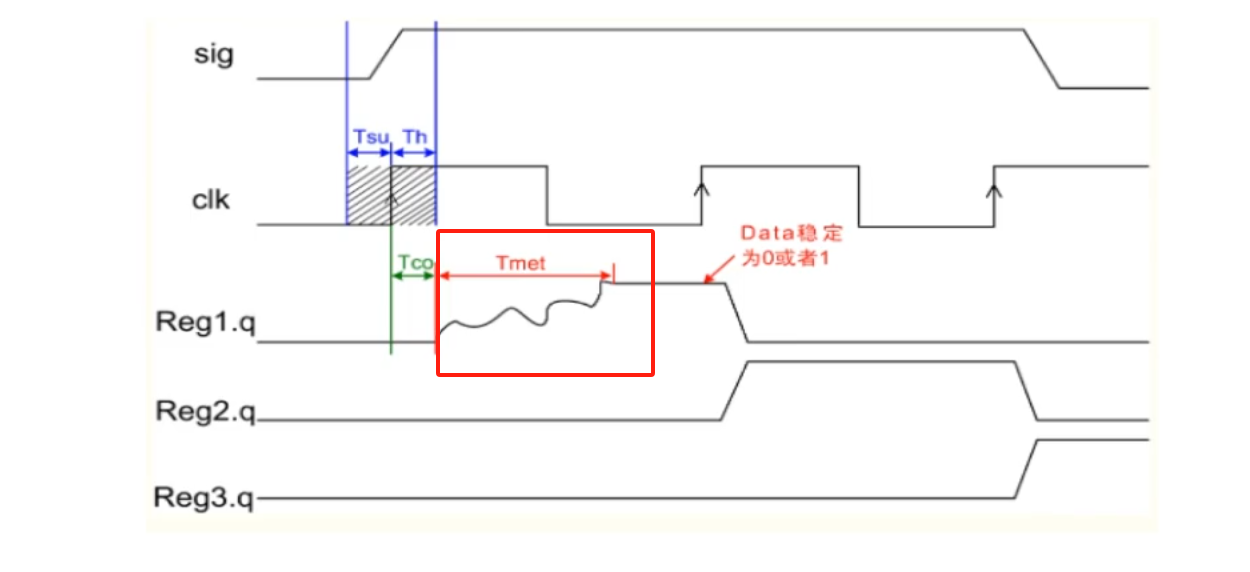

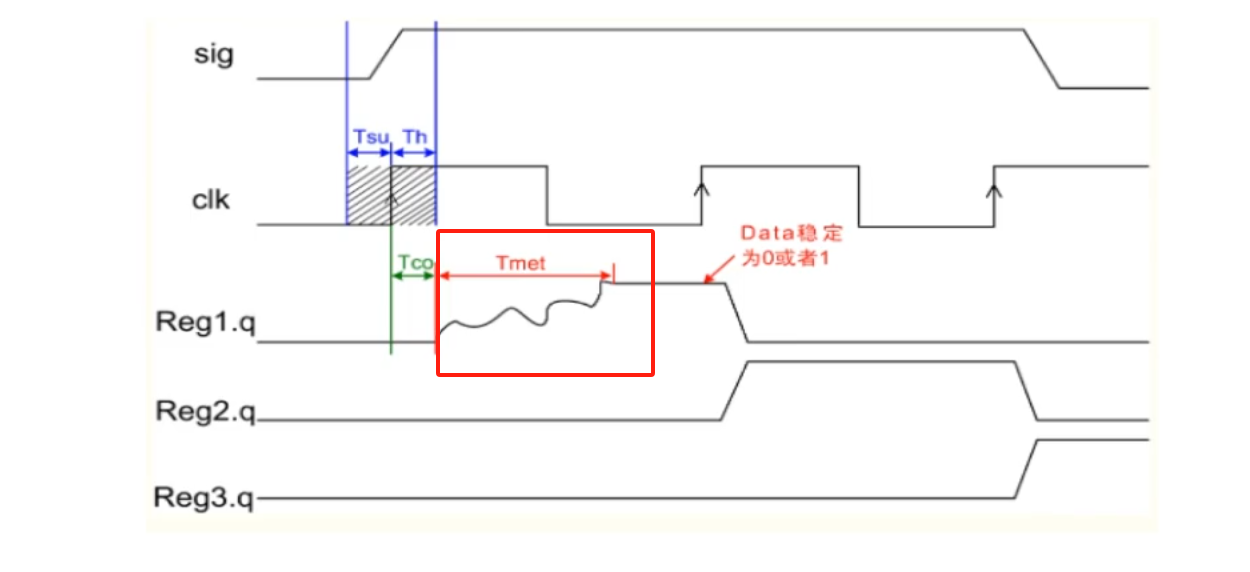

原因是:建立时间和保持时间没有保持住。然后在下图的红框里面,产生亚稳态。因为电路反馈机制,最后大概率会恢复到一个正确的值(低电平0或者高电平1)。

注意

亚稳态无法消除,只能被减弱。

数字IC,FPGA秋招【单bit信号的CDC跨时钟域处理手撕代码合集】_哔哩哔哩_bilibili

原因是:建立时间和保持时间没有保持住。然后在下图的红框里面,产生亚稳态。因为电路反馈机制,最后大概率会恢复到一个正确的值(低电平0或者高电平1)。

亚稳态无法消除,只能被减弱。