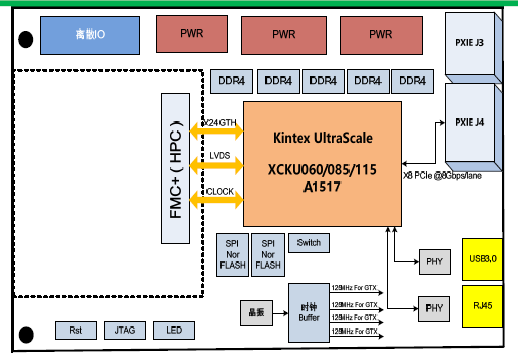

基于PXIE 总线架构的Kintex UltraScale 系列FPGA 高性能数据预处理板卡

一款基于3U PXIE 总线架构的高性能数据预处理FMC 载板,板卡具有1 个FMC+(HPC)接口,1 个X8 GTH 背板互联接口,可以实现1 路PCIe x8。板卡采用Xilinx 的高性能KintexUltraScale 系列FPGA 作为实时处理器,实现FMC 接口数据的采集、处理、以及背板接口互联。板载1 组独立的72 位DDR4 SDRAM 大容量缓存。该板卡通过搭载不同的FMC 子卡,可快速搭建起3U PXIE

系统平台,实现前端数据的预处理,可广泛应用于雷达与中频信号采集、视频图像采集等场景。

技术指标

板载FPGA 实时处理器:XCKU060-2FFVA1517;

与XCKU085-2FFVA1517I 以及XCKU115-2FFVA1517I 可以实

现 PIN-PIN 兼容,可升级FPGA 资源容量;

背板互联接口:

X8 GTH 互联;

支持PCIe gen3 x8@8Gbps/lane;

独立的XDMA 控制器,理论带宽高达64Gbps;

支持SMBUS 总线管理;

FMC 接口指标:

标准FMC+(HPC)接口,符合VITA57.4 规范;

支持x24 GTH@16Gbps/lane 高速串行总线;

支持80 对LVDS 信号;

支持IIC 总线接口;

+3.3V/+12V/+VADJ 供电,供电功率≥15W;

独立的VIO_B_M2C 供电(可由子卡提供);

动态存储性能:

存储带宽:72 位,DDR4 SDRAM,1200MHz 工作时钟;

存储容量:支持4GByte DDR4 SDRAM;

其它接口性能:

8 路LVTTL GPIO 接口,1 路RS422 接口;

1 路RJ45 千兆以太网接口,1 路USB3.0 接口;

板载2 个SPI Flash 用于FPGA 的加载;

物理与电气特征

板卡尺寸:100 x 160mm;

板卡供电:4A max@+12V(±5%,不含给子卡供电);

散热方式:风冷散热;

工作湿度:5%~95%,非凝结