wire与reg理解,阻塞与非阻塞

时序取值,时钟触发沿向左看

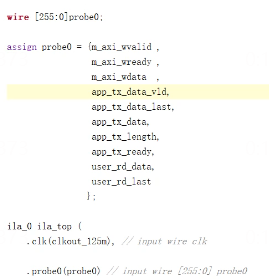

ip核/setup debug 添加 ila

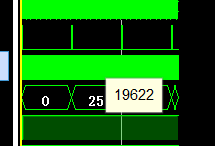

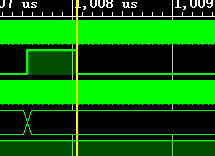

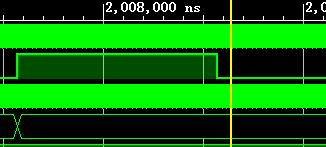

一、ila使用小技巧

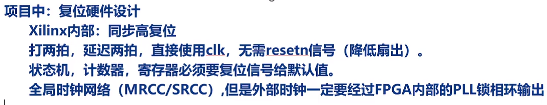

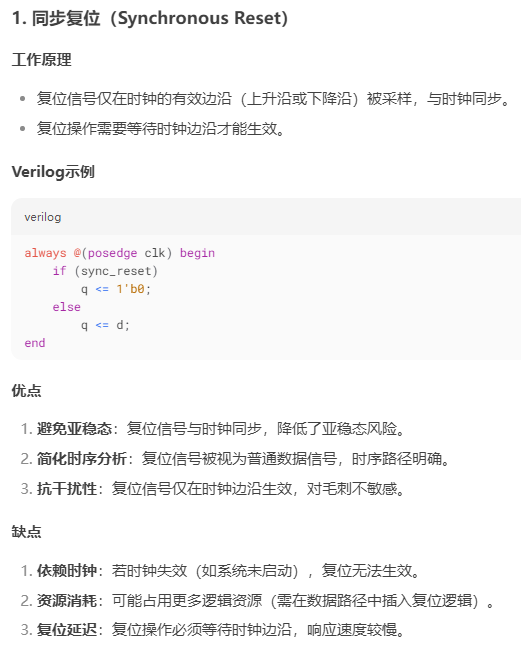

二、同步复位、异步复位和异步复位同步释放

设计复位设计,尽量使用 **异步复位同步释放;**尽管该方法仍然对毛刺敏感,但原本的毛刺复位信号也是一个不定态,无法得知该毛刺是否对工程产生负面影响,那么针对该毛刺,放大了之后更好便于处理问题。

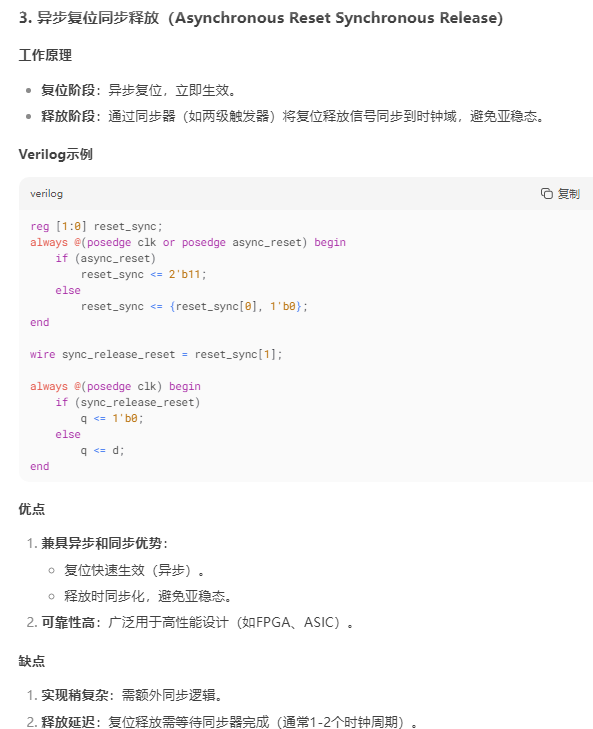

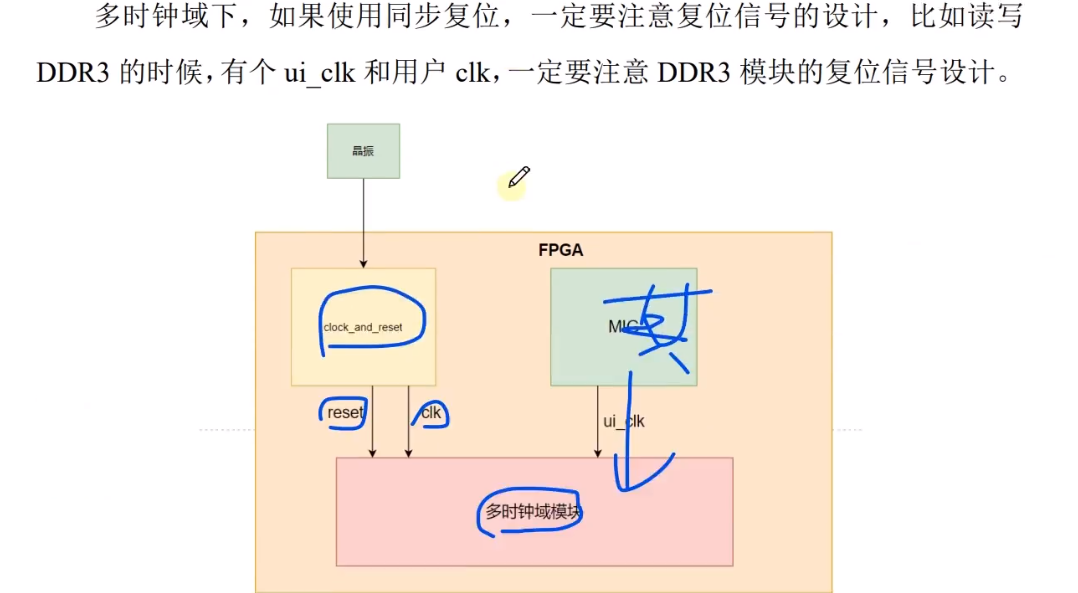

1.项目工程复位时钟产生:

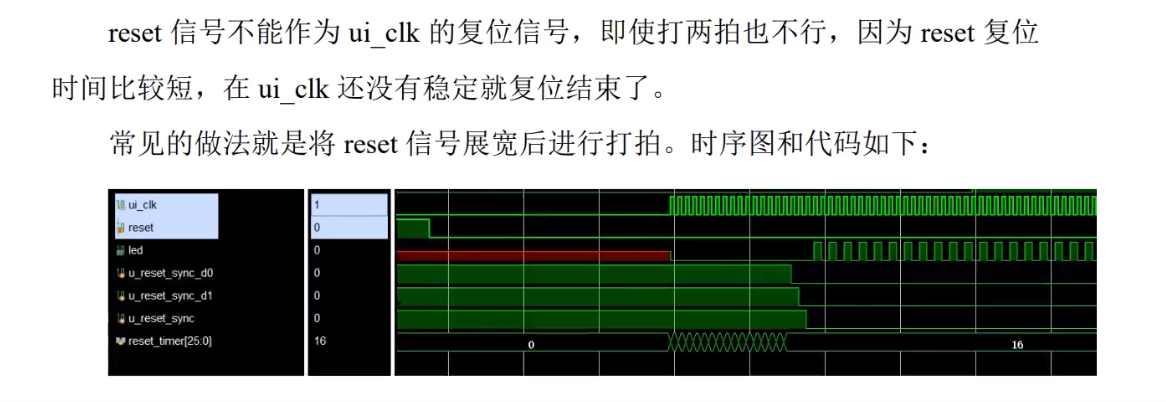

外部晶振时钟经过pll的ip核,通过locked信号,引入计数器cnt对复位信号进行展宽,以便后续的多时钟域进行打拍寄存。例如在后续的ddr设计中,在mig核使用同步复位时,现将复位进行展宽,在进行打两拍寄存,实现对ui_clk的同步

2.多时钟域下同步复位设计

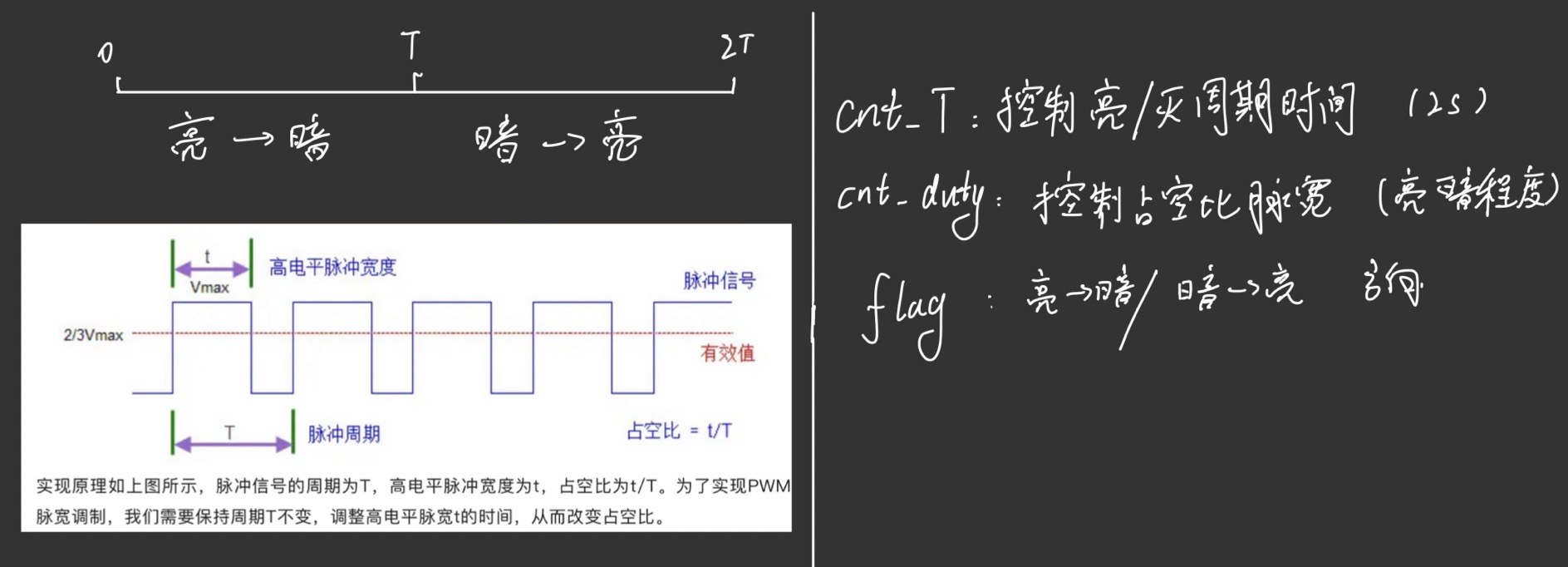

三、呼吸灯实验(PWM调制)

`timescale 1ns / 1ps

//

// Description:呼吸灯

//

module top(

input clk_50M ,

output led

);

reg [15:0] cnt_T;

reg [15:0] cnt_duty ;

reg flag ;

wire clk_sys_50M ;

wire clk_sys_100M ;

wire rst_sys ;

assign led = (cnt_duty > cnt_T) ? 'd1 : 'd0;

//时钟和复位

clock_and_reset u0(

.clk_50M (clk_50M ),

.clk_sys_50M (clk_sys_50M ),

.clk_sys_100M (clk_sys_100M),

.rst_sys (rst_sys )

);

always @(posedge clk_sys_50M or posedge rst_sys) begin

if(rst_sys)

cnt_T <= 'd0;

else if(cnt_T >= 'd50_000)

cnt_T <= 'd0;

else

cnt_T <= cnt_T + 'd1;

end

//默认上电复位从暗到亮

always @(posedge clk_sys_50M or posedge rst_sys) begin

if(rst_sys)begin

cnt_duty <= 'd0;

flag <= 'd1;

end

else if(cnt_T >= 'd50_000)begin

//flag = 1,亮度递增;佛增递减

if(flag)begin

if(cnt_duty == 'd50_000)

flag <= ~flag;

else

cnt_duty <= cnt_duty + 'd25;

end

else begin

if(cnt_duty == 'd0)

flag <= ~flag;

else

cnt_duty <= cnt_duty - 'd25;

end

end

else

flag <= flag;

end

endmodule