在FPGA领域,商业工具长期垄断架构设计与验证的「解释权」。而来自多伦多大学的VTR-Verilog-to-Routing项目,以开源代码掀开了FPGA的「黑盒子」,让任何人都能探索从电路设计到布线算法的全链路自由。

一、VTR是什么?------FPGA架构的「科学实验平台」

项目地址:

https://github.com/verilog-to-routing/vtr-verilog-to-routing

https://verilogtorouting.org/

项目定位:

VTR 是一个全球协作的开源项目,旨在为 FPGA 架构和 CAD 研究提供一个完整的设计流程框架。该项目由多所高校和企业共同开发,包括多伦多大学、新不伦瑞克大学、加州大学伯克利分校、谷歌、英特尔等。VTR 的设计流程以 Verilog 描述的数字电路和目标 FPGA 架构描述为输入,经过一系列处理,生成 FPGA 的速度和面积等性能指标.

支持从Verilog代码→逻辑综合→布局布线→时序分析的完整流程

独特能力:允许自定义FPGA架构参数(如LUT大小、布线资源等),实现"虚拟FPGA"仿真

技术栈亮点:

架构探索:可模拟Xilinx/Altera未公开的底层硬件结构

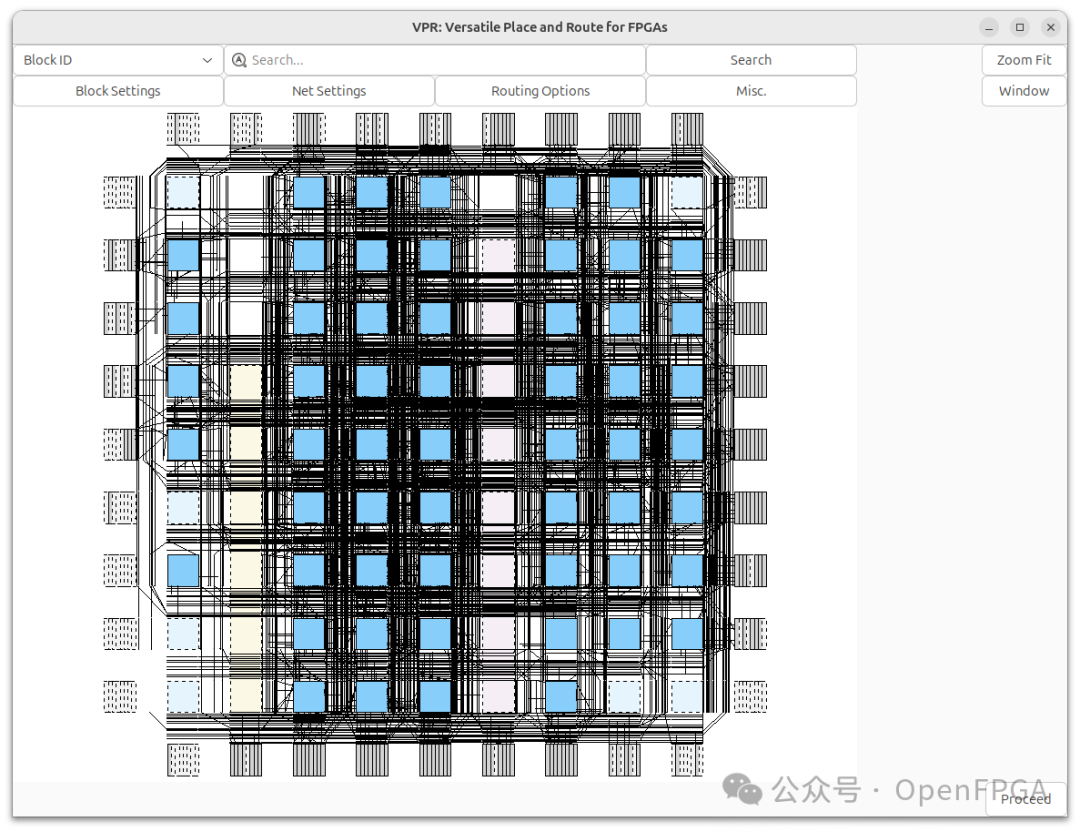

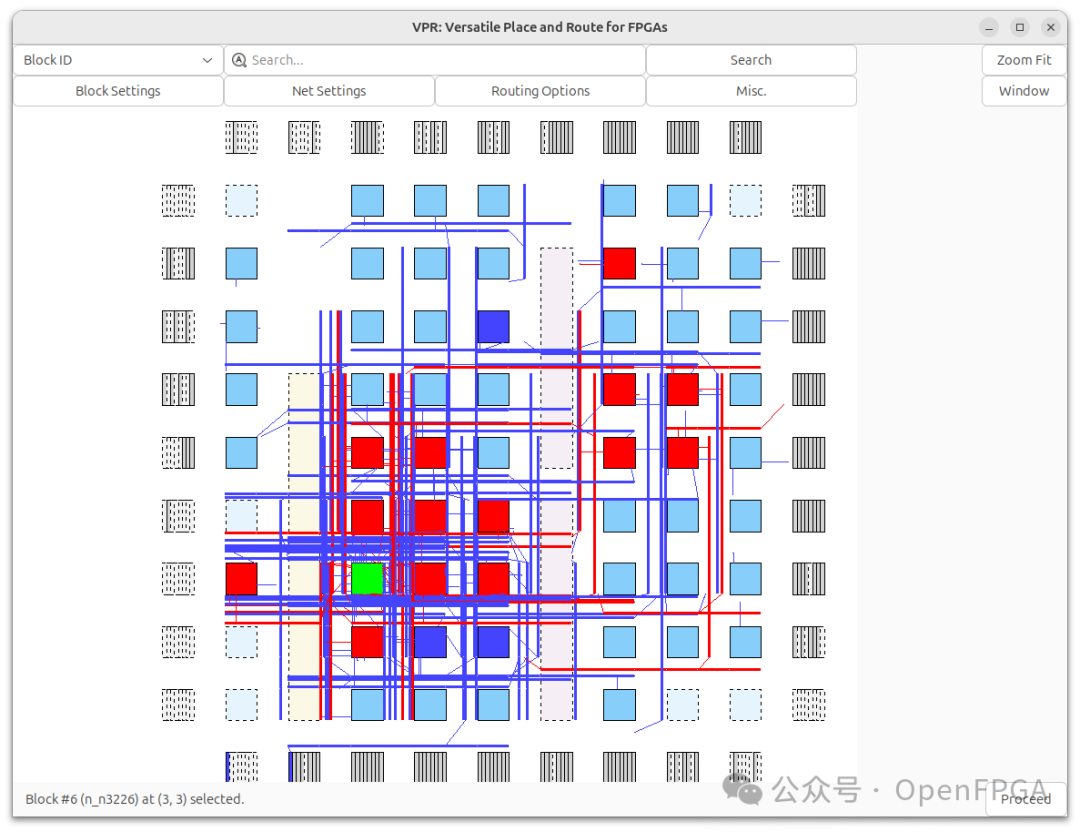

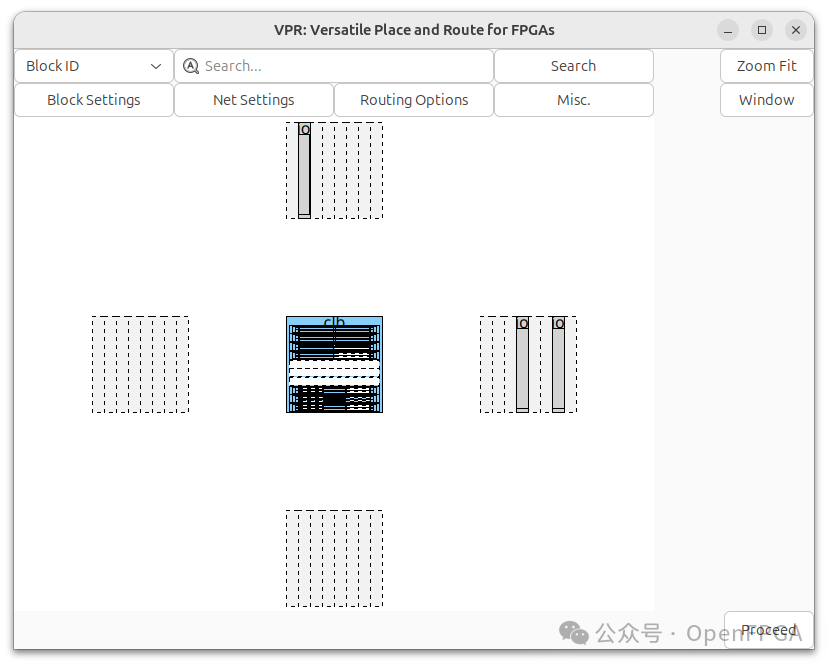

算法竞技场:集成VPR(Versatile Place and Route)布局布线引擎

产学研桥梁:已被Intel PSG、Cornell等用于下一代FPGA预研

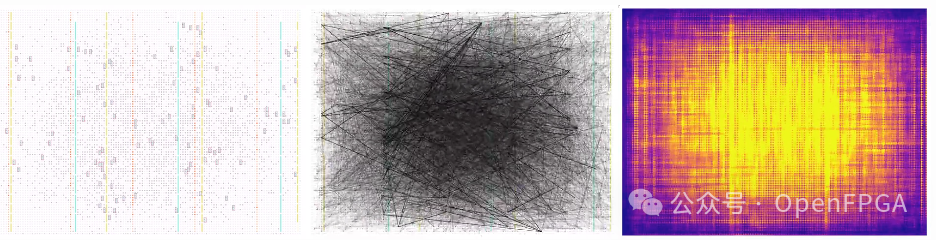

VTR 的设计流程

VTR 的设计流程包括以下主要阶段:

前端综合与部分映射(Parmys):将 Verilog 代码转换为中间表示,并进行初步优化。

逻辑优化与技术映射(ABC):对电路进行逻辑优化,并映射到目标技术库。

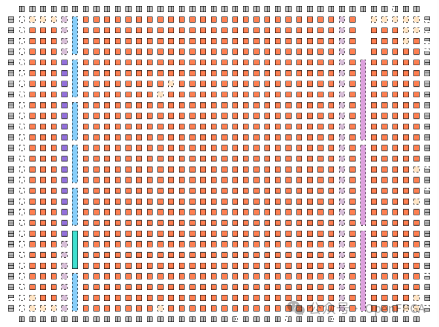

打包、布局、布线与时序分析(VPR):将逻辑块打包、在 FPGA 上进行布局和布线,并进行时序分析,评估设计的性能。

此外,VTR 还支持生成用于编程某些商用 FPGA 的比特流信息(通过 Symbiflow 项目),并包含一套已知可与设计流程配合使用的基准设计。

VTR 的应用场景

VTR 作为一个灵活的开源工具,广泛应用于以下领域:

FPGA 架构研究:探索新型 FPGA 架构的性能和可行性。

CAD 算法开发:开发和测试新的综合、布局、布线算法。

教育教学:作为教学工具,帮助学生理解 FPGA 设计流程。

开源硬件项目:支持开源硬件社区的 FPGA 设计需求。

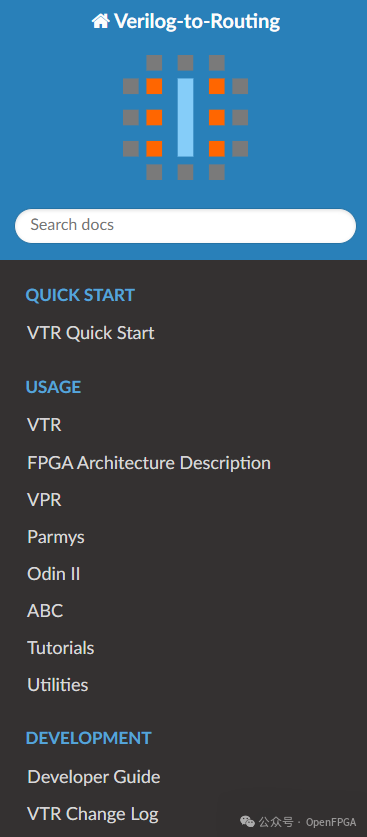

学习资源

VTR官方教程

硬件推荐:

低成本实验:Lattice ICE40UP5K(VTR已支持)

总结

随着 FPGA 技术的不断发展,VTR 项目也在持续进化,最新版本 VTR 9 引入了更多功能和优化,支持更广泛的 FPGA 架构探索。未来,VTR 将继续致力于推动开源 FPGA 设计工具的发展,降低硬件设计的门槛,促进创新和研究。

"当FPGA变成可编程的「乐高积木」,芯片创新的权力不再属于巨头实验室里的少数人。VTR项目的意义,不仅在于它贡献了20万行代码,更在于它证明了一件事:在算力为王的时代,开放的架构,才是最快的架构。"

通过 VTR 项目,研究人员和开发者可以深入探索 FPGA 的设计与实现,推动硬件设计的创新与发展。无论是硬件设计的新手,还是经验丰富的工程师,VTR 都是不可或缺的工具。