近日,FPGA高效验证工具Solidify发布了8.0版本。该版本对图形用户界面(GUI)进行了全面重构,历时两年,经过了大幅的架构改进,旨在为用户提供更安全、更稳定的使用环境。

Solidify的用户对隐私有严格要求,有些场景甚至不连接互联网。WxWidgets跨平台GUI库比Qt更符合用户需求,并能提供更稳定的内部开发和用户环境。8.0新版中的GUI采用WxWidgets并严格实现了模型-视图-控制器(MVC)架构,便于未来必要时切换GUI库能够更加灵活。

此外,8.0版本还修复了近百个问题,并进行了多项功能增强。开发过程中历经近17个里程碑,最终形成了详尽的GUI规格说明,为未来的维护提供了良好基础。现有的GUI仍可使用,但将逐步被替代。

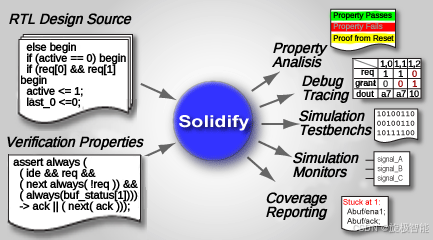

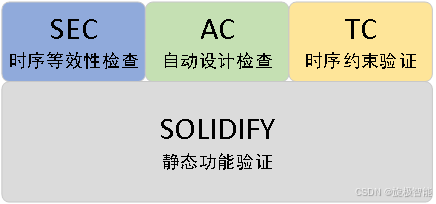

作为一套全面的高效验证工具,Solidify旨在帮助设计人员验证FPGA研发过程中的复杂设计。Solidify工具包包含Solidify(静态功能验证)、SolidSEC(时序等效性检查)、SolidAC(自动设计检查)和SolidTC(时序约束验证)。

Solidify™ - 静态功能验证

Solidify为工具套件的核心,它是一款拥有超过10年实际生产应用验证的高性能形式验证引擎。该工具提供属性验证、多个自主研发的形式化引擎、代码覆盖率分析、无TestBench的缺陷追踪、分层验证、可定制引擎、仿真监测、源代码调试追踪与波形分析等完整功能。

SolidSEC™ - 时序等价性检查

SolidSEC通过时序修改(如功率优化)检查设计和版本之间的功能等效性。此外,该工具可与Solidify集成,以消除时序冗余,从而提高验证性能,并包括一个组合逻辑验证模块。

SolidAC™ - 自动设计检查

SolidAC会自动检查电路是否存在许多常见的设计问题。SolidAC只需读取设计源代码,且几乎无需用户额外输入,就可以跟踪诸如跨时钟域问题、死锁、死代码和许多常见但难以捉摸的设计缺陷。

SolidTC™ - 时序约束验证

SolidTC采用形式化技术来验证时序异常文件(SDC)中伪路径与多路径约束的正确性。

我们相信用户会对8.0版本的增强功能以及更高的保护性和稳定性感到满意。此次开发很好地补充了我们的验证引擎,为用户提供了一套功能强大、无缝集成的形式化验证环境,涵盖了性质验证、时序和组合等价性检查、跨时钟域检查、属性覆盖率和自动检查等功能。

历经十余年产品化过程中的精心改进与优化,Solidify已成为成熟且广泛部署的验证工具。其兼具卓越的运行速度与大规模的处理能力,代表了属性验证领域的技术巅峰。

了解更多有关Solidify的技术信息及商务服务,请访问http://www.softtest.cn/留言,或按以下方式联系旋极智能: