在当今芯片设计中,多时钟域已成为常态。从手机SoC到航天级FPGA,不同功能模块运行在各自的时钟频率下,时钟域间的信号交互如同"语言不通"的对话,稍有不慎就会引发亚稳态、数据丢失等问题。这些隐患轻则导致功能异常,重则引发系统崩溃。本文将深入解析跨时钟域信号处理的核心问题与解决方案,助您打造高可靠性的芯片设计。

一、跨时钟域的致命陷阱

1. 亚稳态:数字世界的量子态

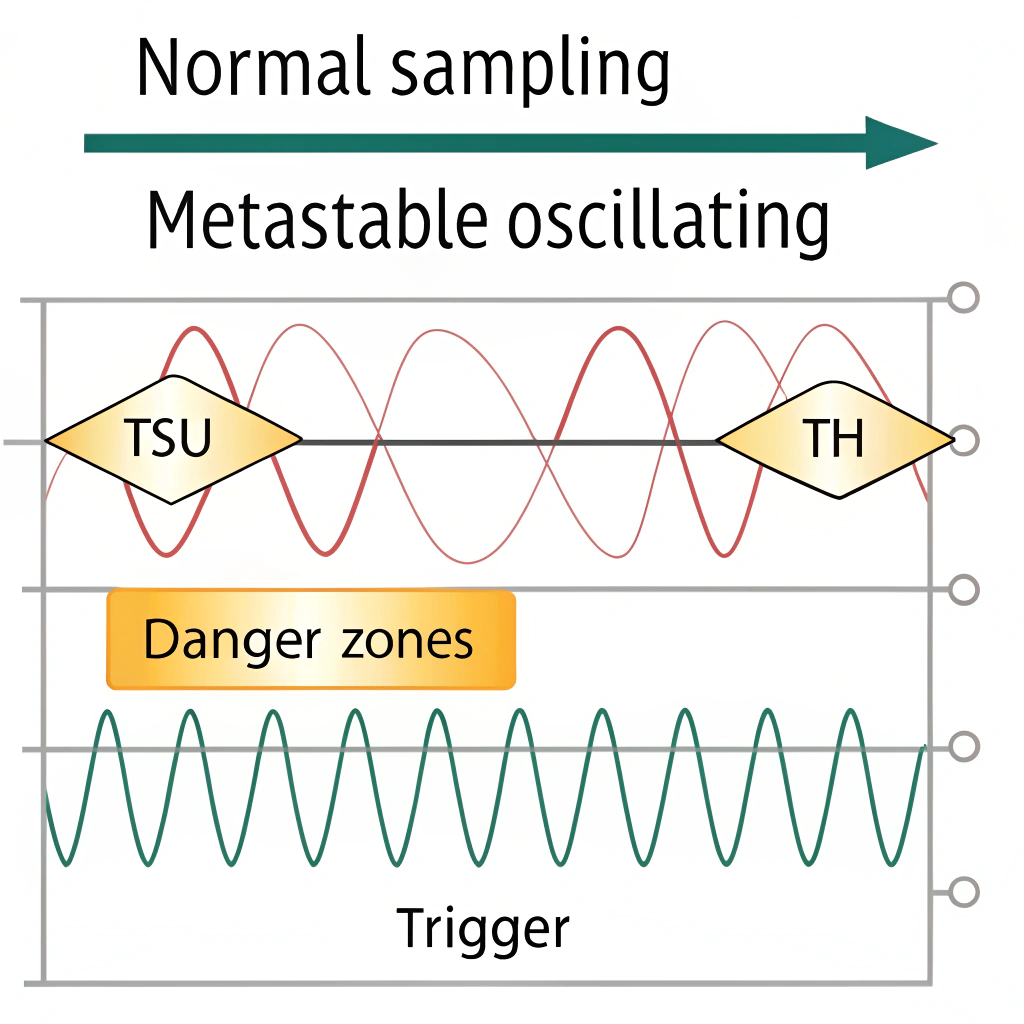

当信号跨越时钟域时,若采样时刻恰好在信号跳变边沿附近,接收端的触发器可能进入亚稳态------既非0也非1的"量子态"。这种状态会引发不可预测的电路行为,且可能通过逻辑链传播,造成大规模功能混乱。

典型案例:某MCU与FPGA通信设计中,异步读取计数器导致数据错乱。由于计数器多位同时翻转时被读取,部分位已更新、部分未更新,最终采集到错误计数值。

2. 数据丢失:快慢时钟的时空错位

当信号从快时钟域传输到慢时钟域时,若信号脉宽小于慢时钟周期,可能完全被"忽略"。例如100MHz时钟域的信号在10MHz时钟域可能被连续两次采样为同一值,导致脉冲丢失。

3. 信号再聚合:异步世界的混乱交响

多个跨时钟域信号在接收端组合使用时,因各信号路径延迟不同,重组后的逻辑可能完全错误。例如两个控制信号A和B在传输中出现错位,导致使能信号误触发。

二、六大跨时钟域处理法宝

方法1:双触发器同步(打两拍)

原理:用两级触发器对单比特信号同步,将亚稳态概率降至百万分之一级。

适用场景:单比特信号从慢时钟域到快时钟域传输。

c

代码示例:

verilog

(* ASYNC_REG = "TRUE" *) reg [1:0] sync_reg;

always @(posedge clk_fast) begin

sync_reg <= {sync_reg[0], async_signal};方法2:握手协议(双向确认)

原理:通过请求-应答机制确保数据安全传输,代价是增加延迟。

适用场景:任意方向、任意位宽信号传输,尤其适合低频控制信号。

关键设计:请求信号需保持到接收端确认,典型需要5级触发器实现全同步。

方法3:格雷码编码

原理:将多比特数据转为每次仅1位变化的格雷码,消除跨时钟域采样错位。

适用场景:连续递增/递减的计数器跨时钟域传输。

c

转换公式:

verilog

gray = (binary >> 1) ^ binary; // 二进制转格雷码方法4:异步FIFO

原理:利用双端口RAM和格雷码指针实现安全数据缓冲。

适用场景:大数据量跨时钟域传输,支持任意方向、任意频率比。

设计要点:

读写指针采用格雷码,避免指针同步错误

深度计算需考虑最差情况下的数据堆积

方法5:独热码转换

原理:将多比特信号编码为每次仅1位有效的独热码,避免多位同时跳变。

适用场景:离散状态信号传输,如状态机控制信号。

方法6:电平展宽+同步

原理:对窄脉冲进行展宽,确保被慢时钟域捕获。

适用场景:快时钟域窄脉冲传输至慢时钟域。

c

实现方式:

verilog

always @(posedge clk_fast) begin

if(pulse_in) extend_reg <= 1'b1;

else if(slow_ack) extend_reg <= 1'b0;

end

三、跨时钟域验证三板斧

1. 结构验证

检查同步电路是否存在(至少两级触发器)

验证多比特信号是否采用格雷码/FIFO

识别信号再聚合路径

2. 协议检查

分析信号保持时间是否满足慢时钟采样需求

验证握手协议超时机制

检查FIFO深度是否匹配业务流量

3. 动态仿真

注入亚稳态注入测试(如人为添加延迟)

使用断言验证跨时钟域时序约束

覆盖率驱动验证:确保所有CDC路径被激活

某航天FPGA实测数据:

| 验证方法 | 发现问题数量 | 修复后MTBF提升 |

|---|---|---|

| 结构验证 | 23处CDC错误 | 100倍 |

| 协议检查 | 5处数据丢失风险 | 1000倍 |

| 动态仿真 | 2处再聚合错误 | 10倍 |

四、未来挑战与趋势

3D IC带来的三维时钟域:堆叠芯片中垂直方向的跨时钟域同步

光互连时钟恢复:光电融合芯片的时钟域协同

AI驱动的CDC验证:机器学习自动识别潜在亚稳态路径

设计箴言:

"跨时钟域问题不会消失,只会转移。优秀的设计师不是消灭问题,而是将风险控制在已知范围内。"

结语

掌握这些核心方法,您将能游刃有余地应对复杂芯片设计中的时钟域挑战。在追求性能与功耗平衡的时代,安全可靠的跨时钟域设计,正是芯片竞争力的隐形护城河。