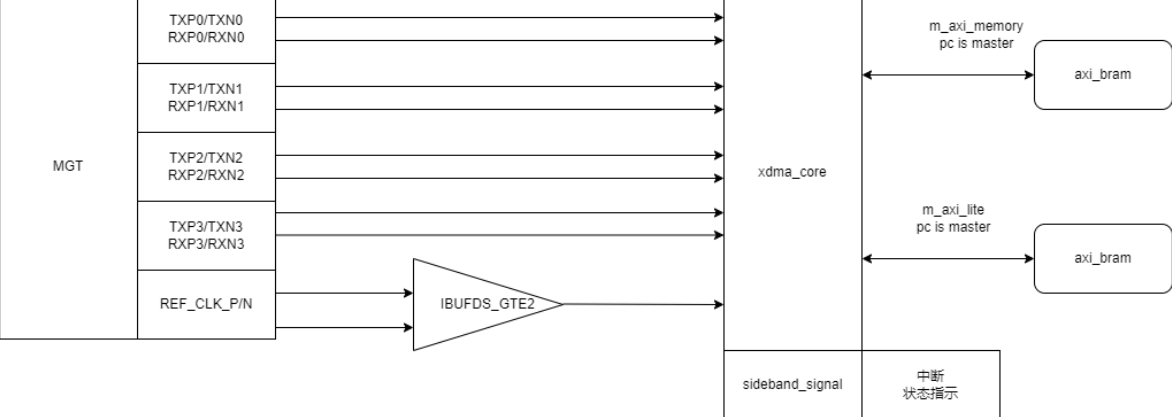

图-1 测试框架图

一、上图中,主要用于测试XDMA的axilite寄存器访问和axi-memory大数据访问,图1完成了逻辑设计。

二、如果是windows环境,进行相关驱动开发,打驱动,然后进行应用层数据读写操作

参考:(WIN)S04-CH01 PCIE XDMA开发环境搭建以及环路测试 - 4-PCIE UISRC工程师开源站 -

三、如果是和ARM交互,那就是使用linux驱动,然后应用层进行数据读写操作

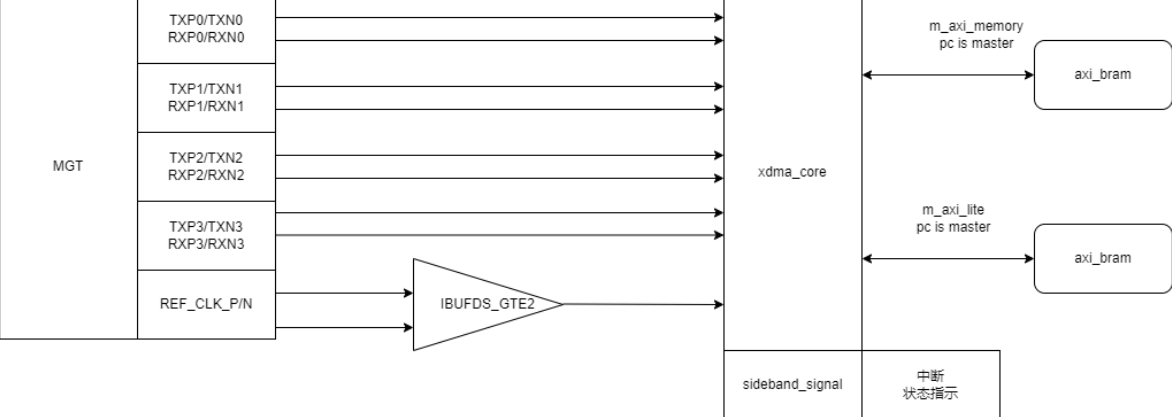

图-1 测试框架图

一、上图中,主要用于测试XDMA的axilite寄存器访问和axi-memory大数据访问,图1完成了逻辑设计。

二、如果是windows环境,进行相关驱动开发,打驱动,然后进行应用层数据读写操作

参考:(WIN)S04-CH01 PCIE XDMA开发环境搭建以及环路测试 - 4-PCIE UISRC工程师开源站 -

三、如果是和ARM交互,那就是使用linux驱动,然后应用层进行数据读写操作