CSI-2 协议详细解析 (一)

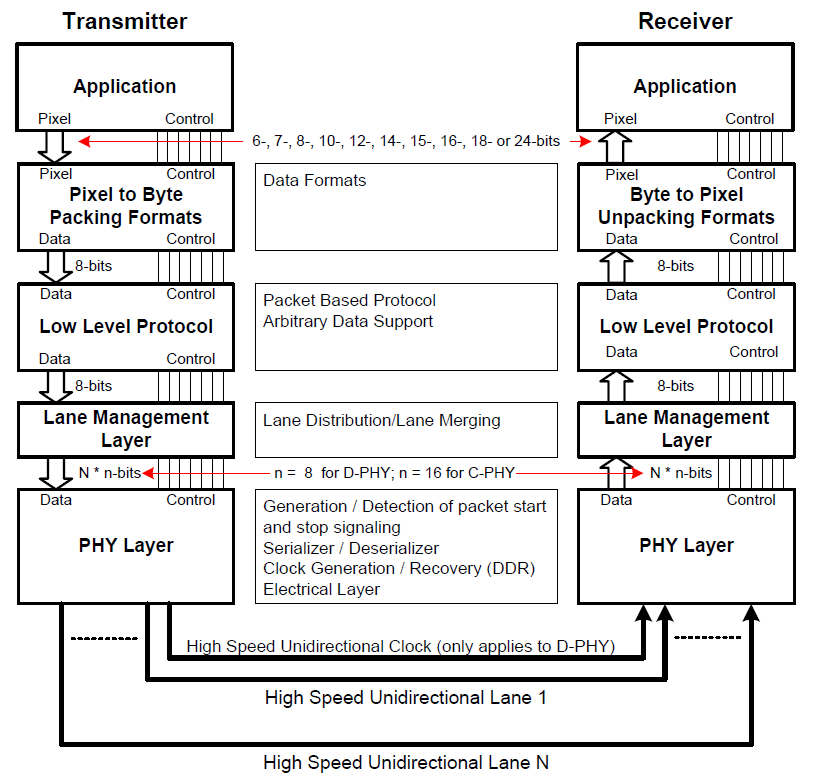

1. CSI-2层定义(CSI-2 Layer Definitions)

分层结构 :CSI-2协议分为6层:

- 物理层(PHY Layer) :

定义电气特性、时钟机制和传输介质(导线)。负责比特/字节同步、SoT/EoT信号及"带外"信息传递。

底层规范由MIPI D-PHY/C-PHY标准定义(本文仅关注D-PHY)。 - 协议层(Protocol Layer) :

支持多数据流标记和交织传输,确保接收端能正确重建各数据流。 - 像素/字节打包层(Pixel/Byte Packing/Unpacking Layer) :

发送端将应用层像素打包为字节;接收端将字节解包为像素。支持6--24位/像素格式,8位/像素数据直通。 - 底层协议(Low Level Protocol, LLP) :

基于字节的包协议(短包/长包格式),支持:- 任意数据传输

- 4个虚拟通道(Virtual Channel)

- 帧/行同步包(Frame/Line Start/End)

- 数据类型(Data Type)描述负载格式

- 16位CRC校验和(D-PHY/C-PHY均适用)

- 8位包头纠错码(ECC,仅D-PHY)

- 通道管理层(Lane Management) :

实现通道扩展:- 发送端 :分发器(LDF)将字节流轮询分发到N个通道。

- 接收端 :合并器(LMF)从N个通道收集并重组字节流。

- D-PHY以单字节为单位分发(C-PHY以双字节为单位)。

- 应用层(Application Layer) :

高层数据编码(如像素映射)

- 规范范围 :仅约束链路上的外部数据/比特模式,内部接口为建议性设计。

2. DPHY物理层(Physical Layer)

- 组成 :1个时钟通道 + 1个或多个数据通道(均为单向差分接口)。

- 时钟模式 :

连续时钟(默认) :数据包间时钟保持高速模式。

非连续时钟(可选) :数据包间时钟进入LP-11状态。 - 最低要求 :

| 模块 | 发送器(TX) | 接收器(RX) |

|---|---|---|

| 数据通道 | HS-TX + LP-TX + CIL-MFEN功能 | HS-RX + LP-RX + CIL-SFEN功能 |

| 时钟通道 | HS-TX + LP-TX + CIL-MCNN功能 | HS-RX + LP-RX + CIL-SCNN功能 |

- 关键特性 :

ULPS支持 :所有数据通道必须支持前向超低功耗状态(Escape ULPS)。 - 去偏斜校准 :

- 发送器提供 去偏斜序列模式 ,接收器据此校准通道间偏斜。

- 校准仅在固定频率有效,频率变化时需重新校准。

- 低频率或旧版发送器可绕过校准。

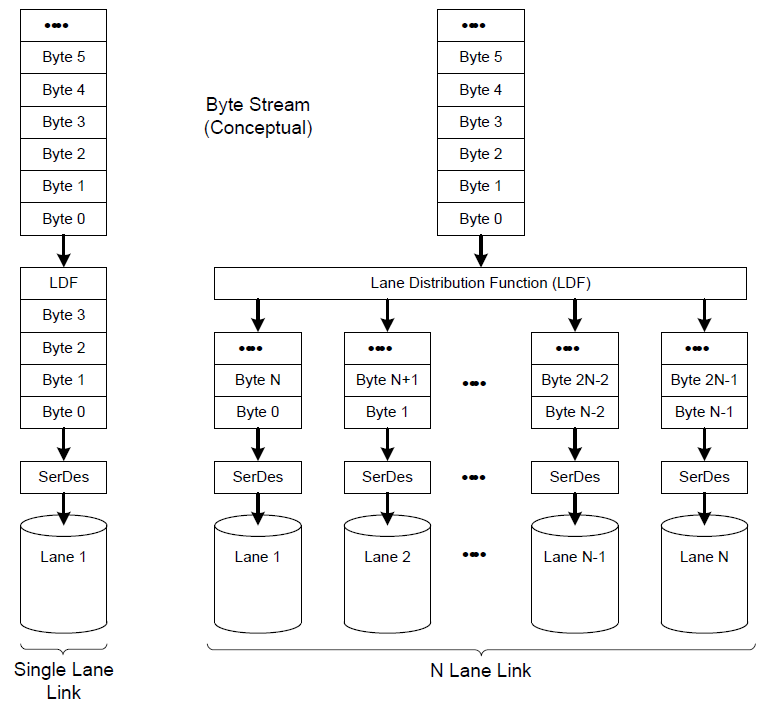

3. 多通道分布与合并(Multi-Lane Distribution/Merging)------仅D-PHY

-

通道扩展原理 :

-

发送端 :分发器(LDF)按轮询方式分配字节:

- N通道示例 :字节0→Lane 1,字节1→Lane 2,...,字节N→Lane 1(循环)。

-

接收端 :合并器(LMF)按通道顺序重组字节流。

-

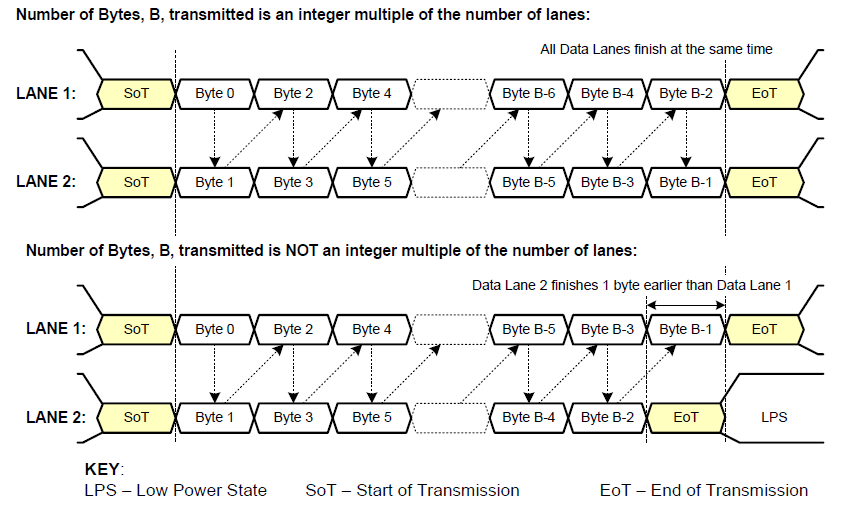

非整数倍字节处理 :

- 末尾字节不足时,无数据的通道进入LPS状态。

- 各通道独立结束传输,EoT信号可能错开1字节周期。

-

通道数互操作性 :

M发送器 vs N接收器 :场景 性能影响 连接规则 M ≤ N(例:1→4) 无损失 TX Lane 1→RX Lane 1,依次对应 M > N(例:4→1) 带宽下降(接收通道不足) TX Lane 1--N→RX Lane 1--N -

配置 :通过CCI接口动态重配置分发/合并逻辑。

-

短包传输 :

短包(4字节)仅需4条通道,多余通道保持LPS状态(图28)。

总结重点 :CSI-2通过分层协议和通道扩展实现高带宽传输,D-PHY物理层提供稳定电气接口,多通道管理确保字节级精确分发/合并,且支持发送端与接收端通道数灵活适配。