低层协议(Low Level Protocol, LLP)详细解析

1. 低层协议(Low Level Protocol, LLP)核心特性

- 包基础 :基于字节的包协议,支持 短包 (32位)和 长包 (可变长度)。

- 关键功能 :

传输任意数据负载(与格式无关)

支持4个虚拟通道(Virtual Channel)

帧/行同步包(Frame/Line Start/End)

数据类型(Data Type)标识负载格式(如YUV/RGB/RAW) - 错误检测 :16位CRC校验(长包负载)

- 错误纠正 :8位包头ECC(仅D-PHY)

2. 包结构详解

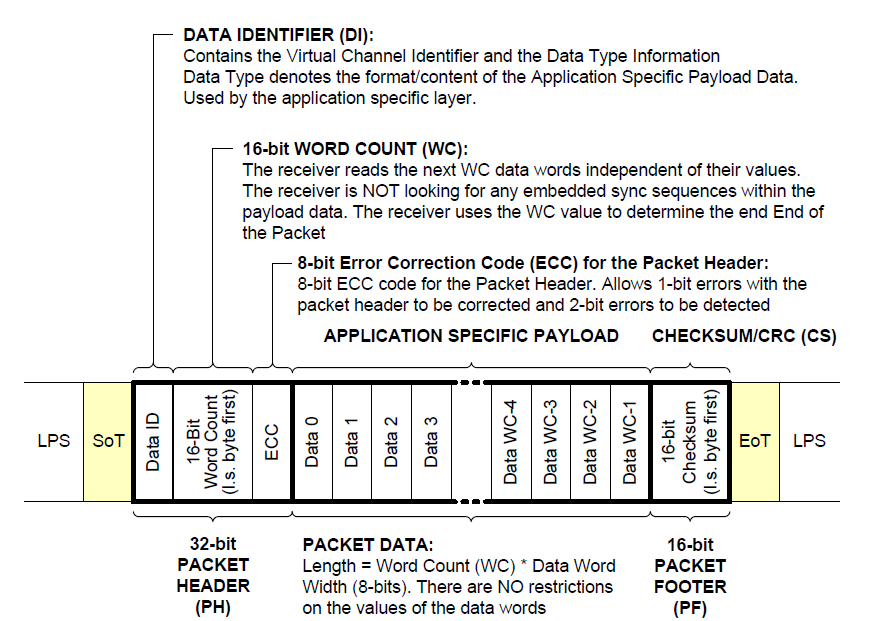

(1) 长包(Long Packet)

-

包头(PH)字段 :

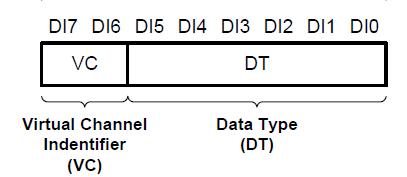

数据标识(DI, 1字节) :高2位=虚拟通道号(0-3),低6位=数据类型

字计数(WC, 2字节) :负载的 字节数 (LSB优先)。

ECC(1字节) :保护包头(可纠正1位错误,检测2位错误)。 -

包尾(PF) :16位CRC校验整个负载。

-

数据包负载规则 :长度=WC字节,值无限制(无嵌入同步码)。

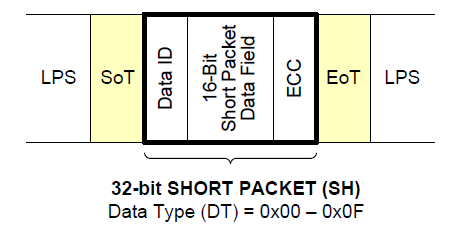

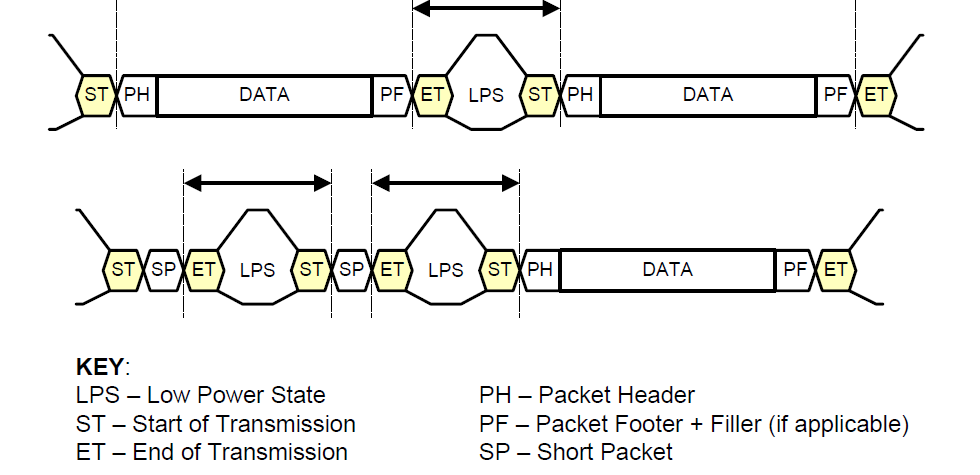

(2) 短包(Short Packet)

- 仅含包头 :结构同长包PH,但WC字段替换为 16位用户数据 (如帧/行号)

- 用途 :

同步包 (Data Type 0x00-0x03):

0x00帧开始(FS)、0x01帧结束(FE)→ 携带 16位帧号 (非零)

0x02行开始(LS)、0x03行结束(LE)→ 携带16位行号

通用包 (Data Type 0x08-0x0F):传递用户自定义事件(如快门控制)。

3. 关键机制

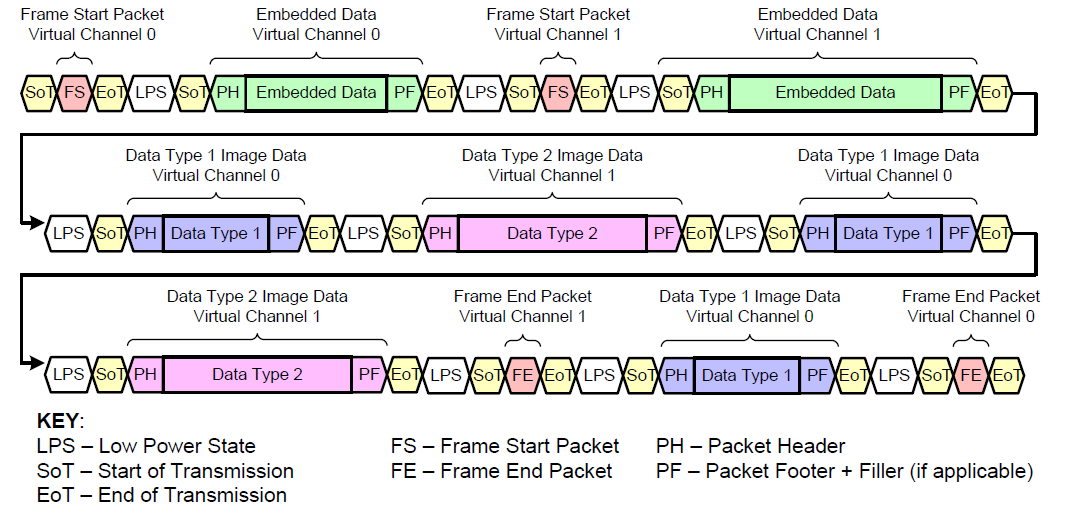

(1) 虚拟通道(Virtual Channel)

- 作用 :复用4个独立数据流(如多摄像头)。

- 实现 :DI字节高2位标识通道号(0-3),接收端据此分流(图44, 67)。

- 特性 :各通道有独立帧同步(FS/FE包),支持不同帧率。

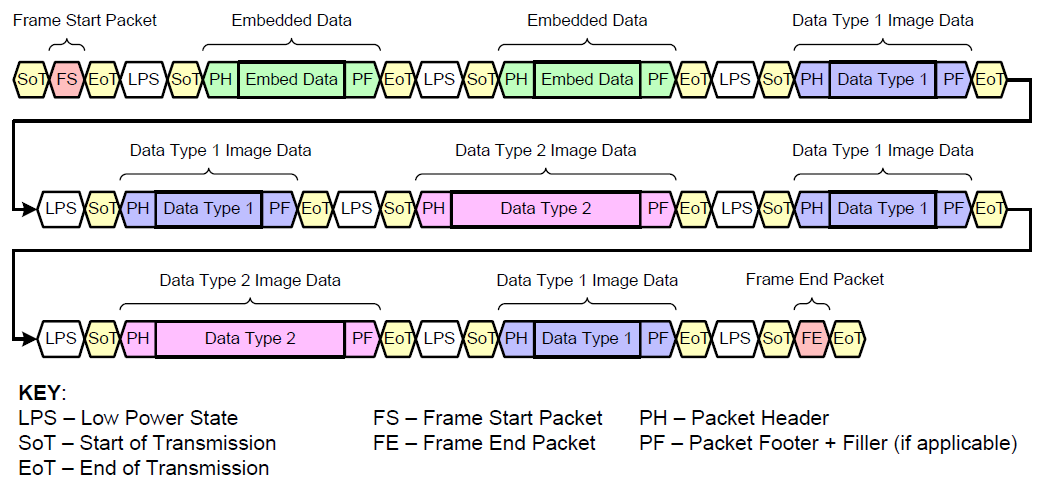

(2) 数据交织(Data Interleaving)

-

方式 :

-

类型交织 :同一通道内不同DataType包交替传输,基于相同的帧开始、帧结束控制,传输不同数据类型的包。

-

通道交织 :不同Virtual Channel包混合传输,每个虚拟通道单独控制自己的帧开始、帧结束包。

-

规则 :同一帧内同通道同DataType包长度必须一致(YUV420例外)。

(3) DPHY错误处理

- 包头ECC :

- 基于 汉明码(24位) ,覆盖DI+WC字段,可以纠正24-bit数据的一个错误,标示两个错误的存在,提高传输的鲁棒性。

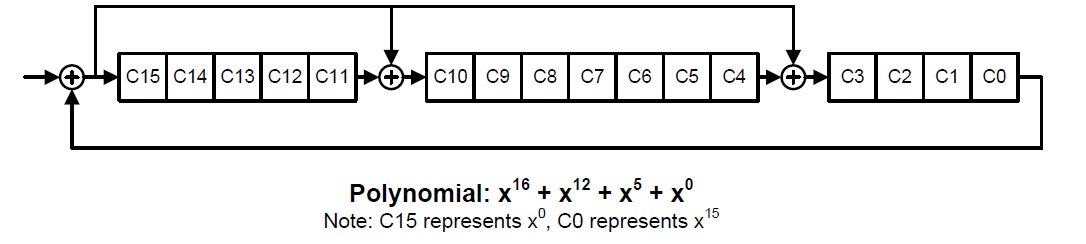

- 负载CRC :多项式

x¹⁶ + x¹² + x⁵ + 1,初始值0xFFFF

4. 传输规则

-

包间距 :包间必须进入 低功耗状态(LPS)

-

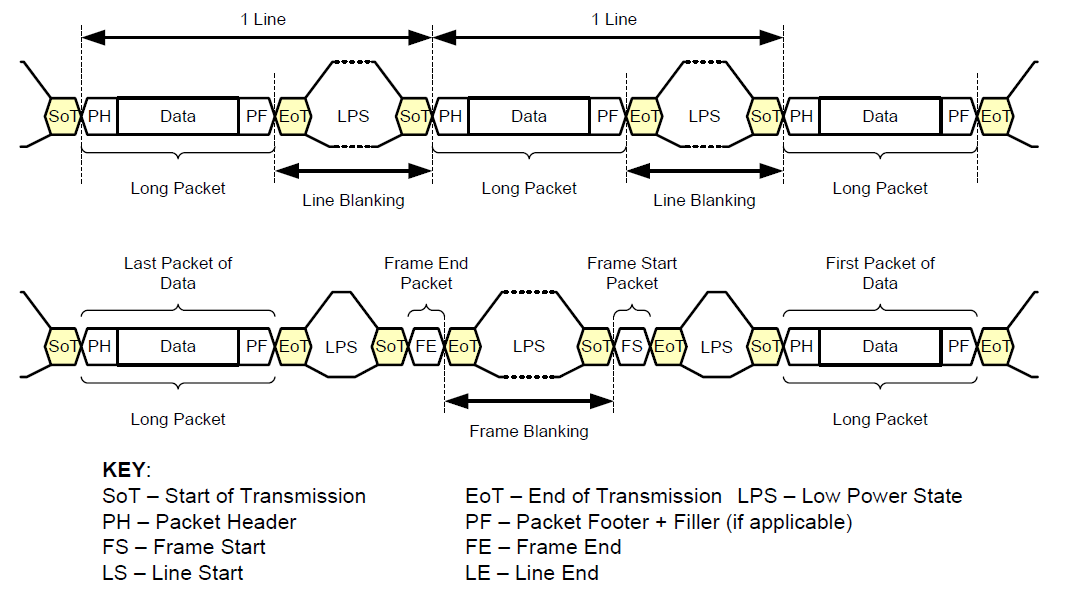

时序控制 :

-

垂直同步 :FS/FE包位置可调,实现像素级精准帧定时

-

水平同步 :LS/LE包位置可调,控制行消隐期

-

空白期定义 :

行消隐(Line Blanking) :包尾到下一包头之间

帧消隐(Frame Blanking) :FE包到下一FS包之间