背景介绍: 我们在进行原理图设计时,经常需要对设计规则进行检查,来确保设计符合制造工艺的能力和限制,避免在实际生产过程中出现因设计不当而导致的缺陷或失败。而通过Capture自带的Design Rules Check功能可以快速实现这一效果,帮助设计师设置设计规则,实时检查不符合规则的错误,更好地进行设计。

下面我们就开始分享具体的操作步骤:

一、实现 Design Rules Check

步骤一:使用Capture CIS软件打开原理图,在工程管理器窗口选中整个工程,在菜单栏中依次点击"PCB"-"Design Rules Check...",如图1所示。

图1 打开"Design Rules Check"窗口

步骤二:在弹出的DRC规则设置界面中先在"Options"标签下修改想要的设置,如图2所示。

图2 "Options"标签

"Options"标签功能详情如表1所示。

表1 "Options"标签功能详情

|--------|----------------------|-----------|

| 序号 | 名称 | 功能详情 |

| ① | Online DRC | 是否开启实时DRC |

| ② | DRC Action | DRC运行范围 |

| ③ | Use Properties(Mode) | 使用的属性模式 |

| ④ | Warning | 是否创建DRC标记 |

| ⑤ | Waived DRC | 是否隐藏DRC |

| ⑥ | Show DRC Outputs | 是否显示DRC输出 |

| ⑦ | Report | 输出报告路径 |

步骤三:选中"Rules Setup"标签,根据需要勾选和修改想要的"Electrical Rules"设置,其中勾选"Batch"代表运行DRC时检测,勾选"Online"代表实时检测,如图3所示。

图3 编辑电气规则设置

"Electrical Rules"设置功能详情如表2所示。

表2 "Electrical Rules"设置功能详情

|--------|------------------------------------------------|---------------|

| 序号 | 名称 | 功能详情 |

| ① | Check single node nets | 检查单端网络 |

| ② | Check no driving source and Pin type conflicts | 检查无驱动源和引脚类型冲突 |

| ③ | Check duplicate net names | 检查重复网络名称 |

| ④ | Check off-page connector connections | 检查跨页连接符连接 |

| ⑤ | Check hierarchical port connections | 检查层次端口连接 |

| ⑥ | Check unconnected bus nets | 检查未连接的总线网络 |

| ⑦ | Check unconnected pins | 检查未连接的引脚 |

步骤四:根据需要勾选和修改想要的"Physical Rules"设置,如图4所示。

图4 编辑物理规则设置

"Physical Rules"设置功能详情如表3所示。

表3 "Physical Rules"设置功能详情

|--------|----------------------------------------------|---------------------|

| 序号 | 名称 | 功能详情 |

| ① | Check power pin visibility | 检查电源引脚显示属性 |

| ② | Check missing/illegal PCB footprint property | 检查PCB封装属性缺失/非法 |

| ③ | Check PCB footprint in configured path | 检查PCB封装配置路径 |

| ④ | Check normal covert view sync | 检查正常视图和转换视图引脚编号是否相同 |

| ⑤ | Check incorrect Pin Group assignment | 检查统一引脚组中所有引脚类型是否相同 |

| ⑥ | Check high speed props syntax | 检查网络高速属性的语法 |

| ⑦ | Check missing pin numbers | 检查引脚编号丢失 |

| ⑧ | Check device with zero pins | 检查无引脚器件 |

| ⑨ | Check power ground short | 检查电源引脚是否连接到不同名称的网络 |

| ⑩ | Check name prop consistency | 检查层次块是否有相同的名称属性 |

步骤五:根据需要勾选和修改想要的"Simulation Rules"和"Custom DRC"设置,如图5所示。

图5 编辑仿真规则和自定义DRC设置

"Simulation Rules"和"Custom DRC"设置功能详情如表4所示。

表4 "Simulation Rules"和"Custom DRC"设置功能详情

|--------|--------------------------------|---------------------|

| 序号 | 名称 | 功能详情 |

| ① | Check PSpice Model Path | 检查PSpice模型路径 |

| ② | Device Pin Mismatch | 检查器件位号导致的引脚不匹配 |

| ③ | Hanging Wires | 检查未连接的导线端 |

| ④ | Overlapping Wires | 检查导线重叠 |

| ⑤ | Part Reference Prefix Mismatch | 检查位号前缀不匹配 |

| ⑥ | Port Pin Mismatch | 检查端口引脚不匹配 |

| ⑦ | Shorted Discrete Part | 检查分立器件短接 |

| ⑧ | Invalid Pin Number | 检查无效引脚编号 |

| ⑨ | Physically Shorted PACK-SHORT | 检查物理短接的PACK-SHORT引脚 |

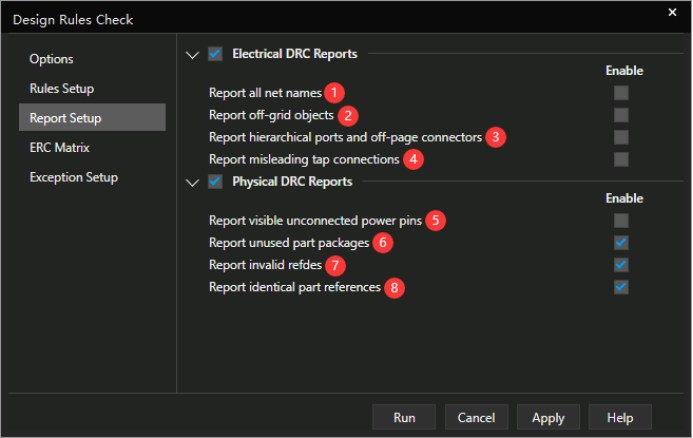

步骤六:选中"Report Setup" 标签,修改"Electrical DRC Reports"和"Physical DRC Reports"设置,如图6所示。

图6 编辑电气和物理DRC报告设置

"Electrical DRC Reports"和"Physical DRC Reports"设置功能详情如表5所示。

表5 "Electrical DRC Reports"和"Physicall DRC Reports"设置功能详情

|--------|---------------------------------------------------|--------------|

| 序号 | 名称 | 功能详情 |

| ① | Report all net names | 报告所有网络名称 |

| ② | Report off-grid objects | 报告不在格点上的对象 |

| ③ | Report hierarchical ports and off-page connectors | 报告层次端口和跨页连接符 |

| ④ | Report misleading tap connections | 报告错误和丢失的总线标签 |

| ⑤ | Report visible unconnected power pins | 报告可见的未连接电源引脚 |

| ⑥ | Report unused part packages | 报告未使用的器件封装 |

| ⑦ | Report invalid packaging | 报告无效封装 |

| ⑧ | Report identical part references | 报告相同位号 |

步骤七:选中"ERC Matrix"标签,矩阵中"W"表示对该类DRC错误进行警告,"E"表示对该类DRC错误进行报错,无标识表示不对该类型进行DRC检查,点击"Restore Defaults"可以恢复默认,修改想要的设置,如图7所示。

图7 编辑ERC矩阵

步骤八:选中"Exception Setup"标签,可以在该处点击"Add New"添加想要忽略的DRC错误编号,或是点击"Remove"移除添加的错误编号,完成后点击"Run",如图8所示。

图8 添加额外规则

步骤九:软件就会自动进行DRC检查,检查完毕会在DRC信息栏将结果显示出来,包括各种警告和错误,如图9所示。

图9 DRC信息栏

步骤十:在该栏中双击想要修改的问题,可以自动对问题进行定位,如图10所示。

图10 自动定位问题位置

步骤十一:在工程管理器的outputs文件夹下也会自动生成drc文件,可以双击打开进行查看,如图11、图12所示。

图11 生成drc文件

图12 查看drc文件

二、小结

本节主要介绍了在Capture CIS原理图设计工具中,如何通过"Design Rules Check"功能实现规则错误检查与管理设置功能,帮助工程师在原理图设计中实时发现设计过程中存在的错误,并及时纠正这些设计错误和存在的问题,为电路的原理图设计打好坚实基础。