设计IP需要考虑如下因素:

1)基于 IBTA 1.5 协议规范,支持 RoCE v2 标准协议传输,同时支持 ARP协议和 ICMP 协议。

2)基于 Xilinx CMAC 集成块进行开发并独立设计 UDP/IP 协议栈。一方面,CMAC 集成块具有多种版本,并且适用平台多,因此本数据传输系统能够部署在支持 CMAC 集成块的 FPGA 开发板上。另一方面,独立设计 UDP/IP 协议栈能够让本设计具有更高的数据传输性能并进一步降低资源占用。

3)采用纯逻辑电路开发。设计基于纯逻辑电路,可以脱离 MCU 控制独立运行,兼容 SoC 环境与纯逻辑环境。

4)使用标准 AXI 总线接口,设计使用标准化的 AXI4 及 AXI-Stream 总线接口进行数据传输,同时使用标准化的 AXI-Lite 总线接口提供系统控制功能,在保证传输性能的同时,使得本设计更容易集成到应用、生产环境中。

5)多队列并行管理及控制。支持系统运行过程中进行创建队列、删除队列、队列更改等操作。

6)DMA 传输。通过配置 DMA 寄存器实现直接的数据传输请求,同时使用突发传输来提高数据传输性能。

系统框架

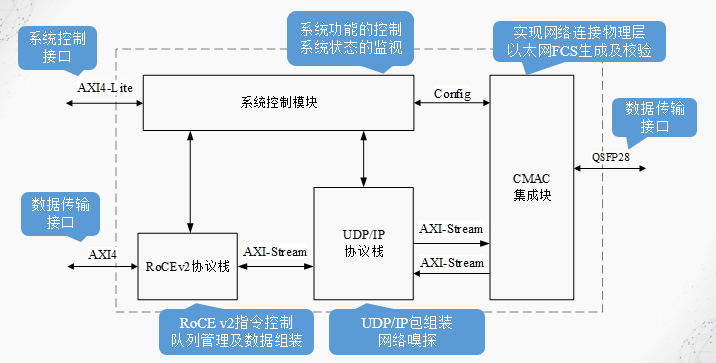

这里重点讨论PC与FPGA之间采用RDMA RoCE v2 高速数据传输,FPGA与FPGA后面介绍。该IP系统的整体架构如图 1 所示。它通过 QSFP28 接口连接上位机进行数据传输;通过AXI-Lite 接口进行系统控制;AXI4 接口进行数据传输。在系统内部,根据功能划分为系统控制模块、融合以太网协议栈、以太网协议栈和 CMAC 集成块。以下为各功能模块的定义。

图1 RDMA over RoCE V2 IP框图

该IP控制模块是实现系统功能控制的核心模块。RoCE v2 高速数据传输系统内部集成了多种功能,包括 RDMA 建链、RDMA 队列管理、DMA 传输和系统监控等。

这些功能均由系统控制模块进行管理。为了对这些功能进行高效的管理,系统控制模块设计了对应的功能控制单元及相应的寄存器,并将这些寄存器抽象为 AXI-Lite 从机端接口,使得本数据传输系统可以简易地集成进用户环境。同时通过 AXI-Lite 接口,用户可以高效的与本数据传输系统进行交互,实现对系统功能的控制,而不必了解本IP的底层工作逻辑。

融合以太网协议栈是实现 RoCE v2 命令提交和完成机制的核心模块,完成网络层级中网络层及应用层功能。该模块负责将来自系统控制模块的功能请求转换为RoCE v2 指令,如建链、断链、数据传输,并执行指令提交及完成机制。此外,该模块还实现了 RDMA 队列管理功能,包括队列存储、队列创建及删除、队列仲裁等功能。同时,本模块也负责控制 DMA 数据读写,将数据读写请求转换为 AXI4 总线事务,通过 AXI4 总线接口读写数据,并负责 RoCE v2 网络包的封装、解析、不变循环冗余校验(ICRC)生成等功能。

以太网协议栈模块负责解析及组装网络包,完成网络层级中传输层、网络层及网络接口层功能。首先,该模块接收来自融合以太网协议栈的网络包,并为其逐层添加UDP、IP 及 ETH 头部,使其成为完整的网络包后发送至 CMAC 集成块。其次,该模块解析来自远程主机的 ARP 或 ICMP 网络包,用以实现网络嗅探功能。最后,该模块负责接收 CMAC 集成块传输过来的网络包,并对其进行解包和解析,而后根据包的功能分发到相应模块或子模块。最后,该模块还实现了网络拥塞处理及流量控制机

制,如 ECN 协议或 PFC 协议。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click