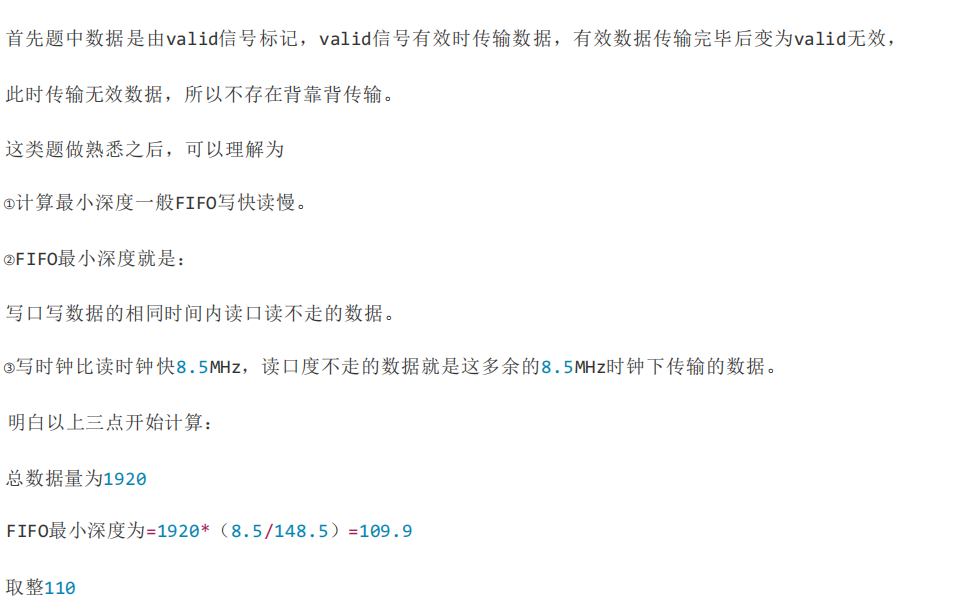

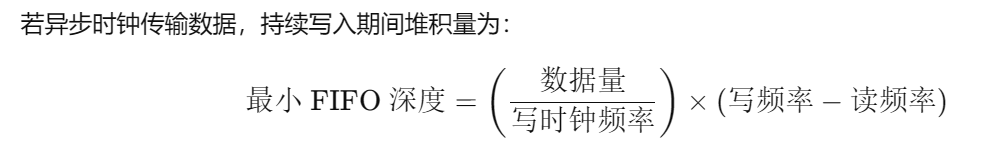

FIFO深度计算

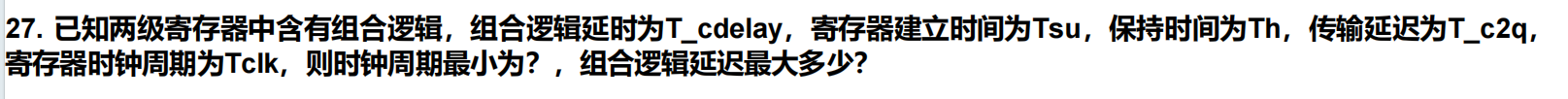

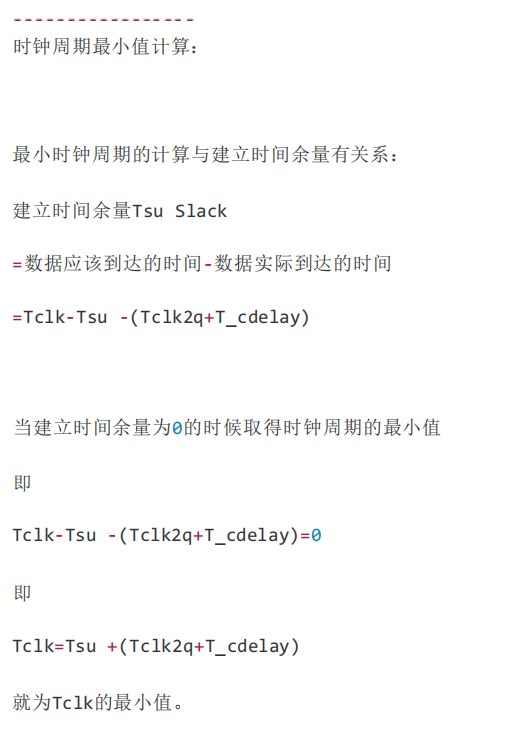

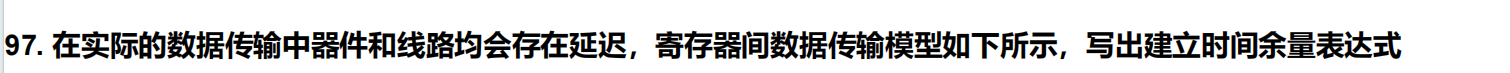

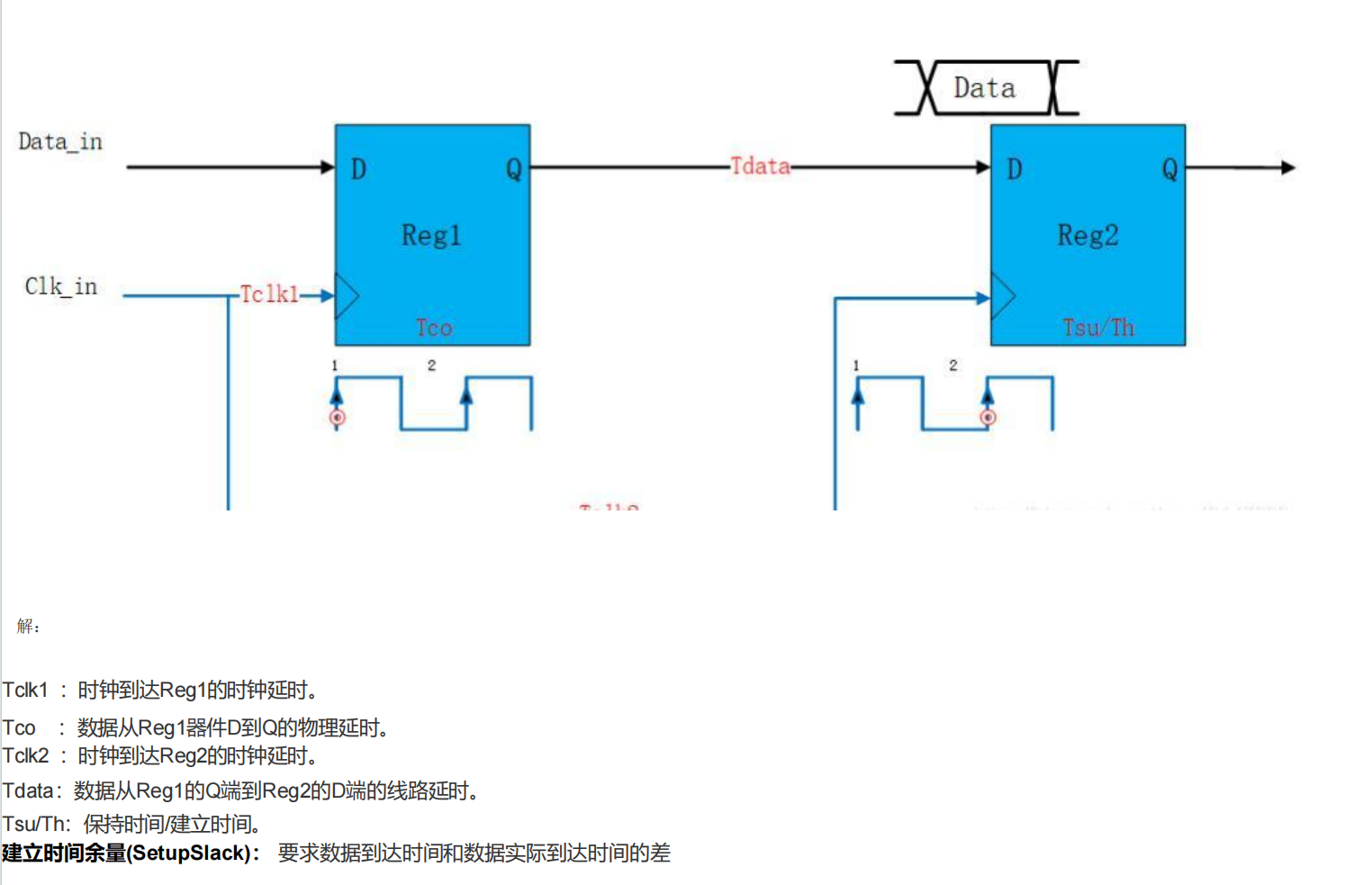

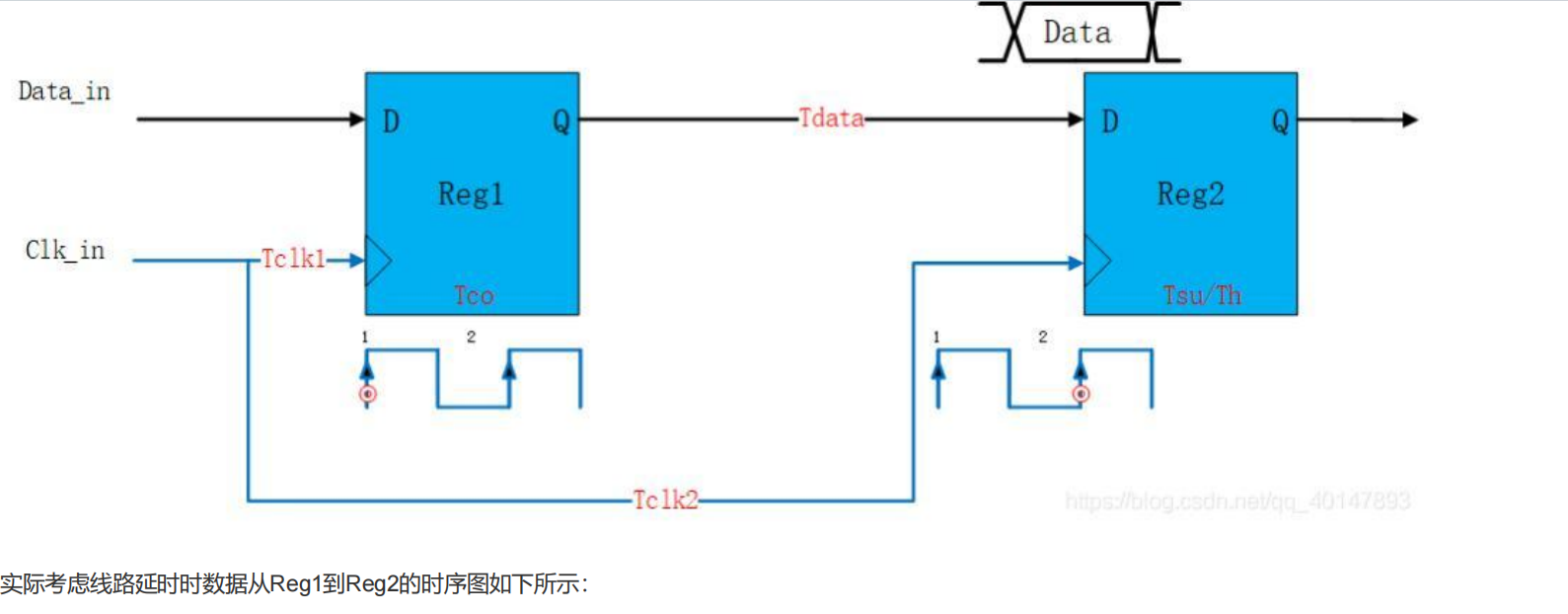

时序分析

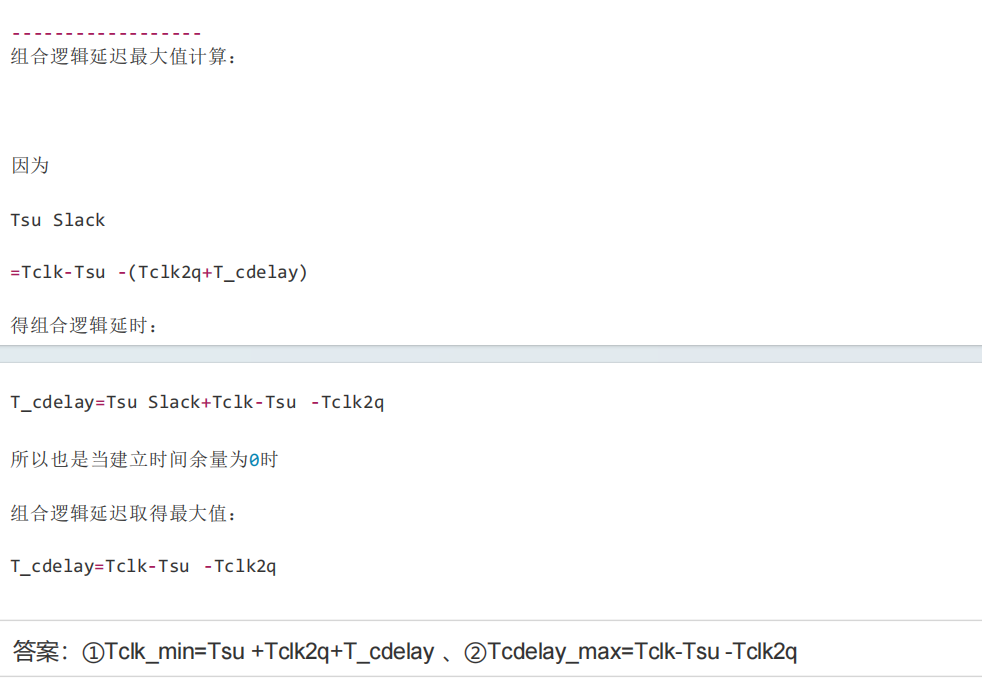

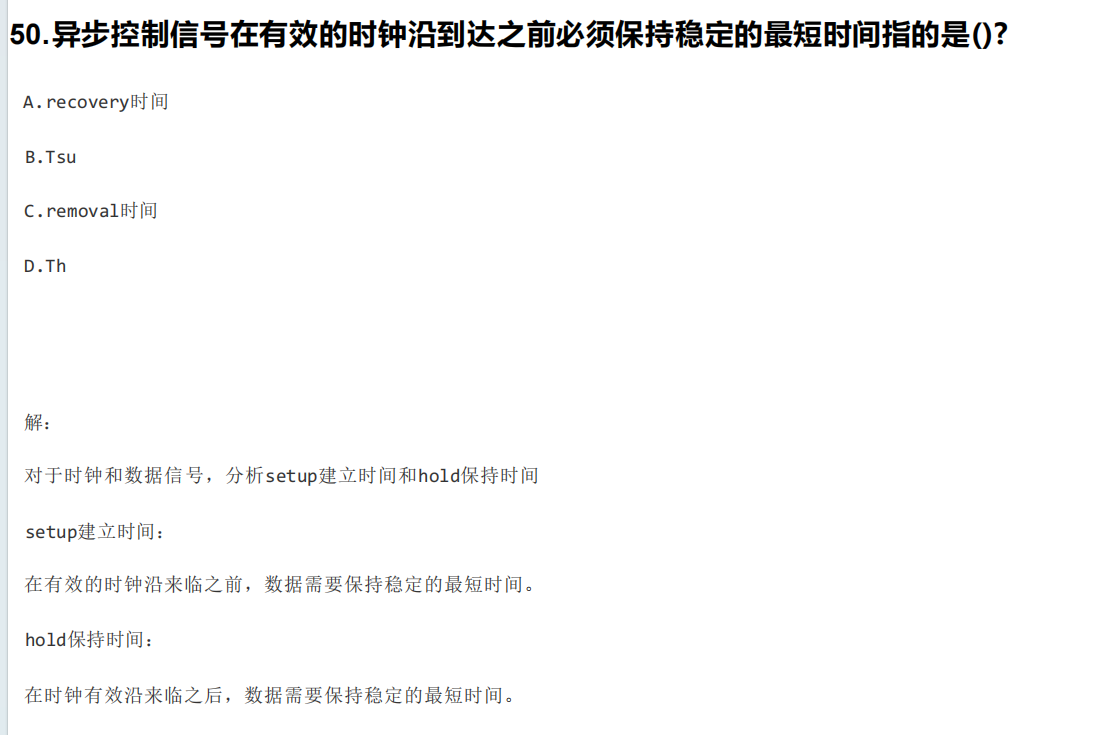

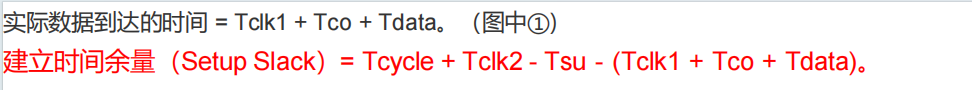

建立时间余量

=数据应该到达的时间-数据实际到达的时间

=Tclk-Tsu -(Tclk2q+T_cdelay)

保持时间余量

=数据路径实际到达时间 - 最早允许的数据保持时间

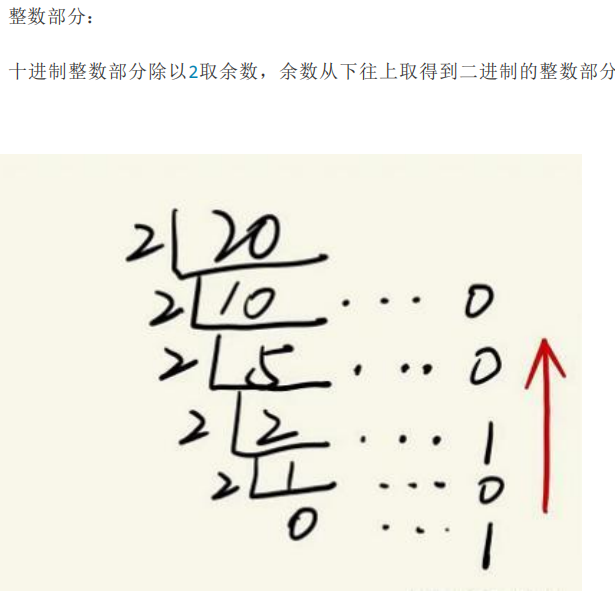

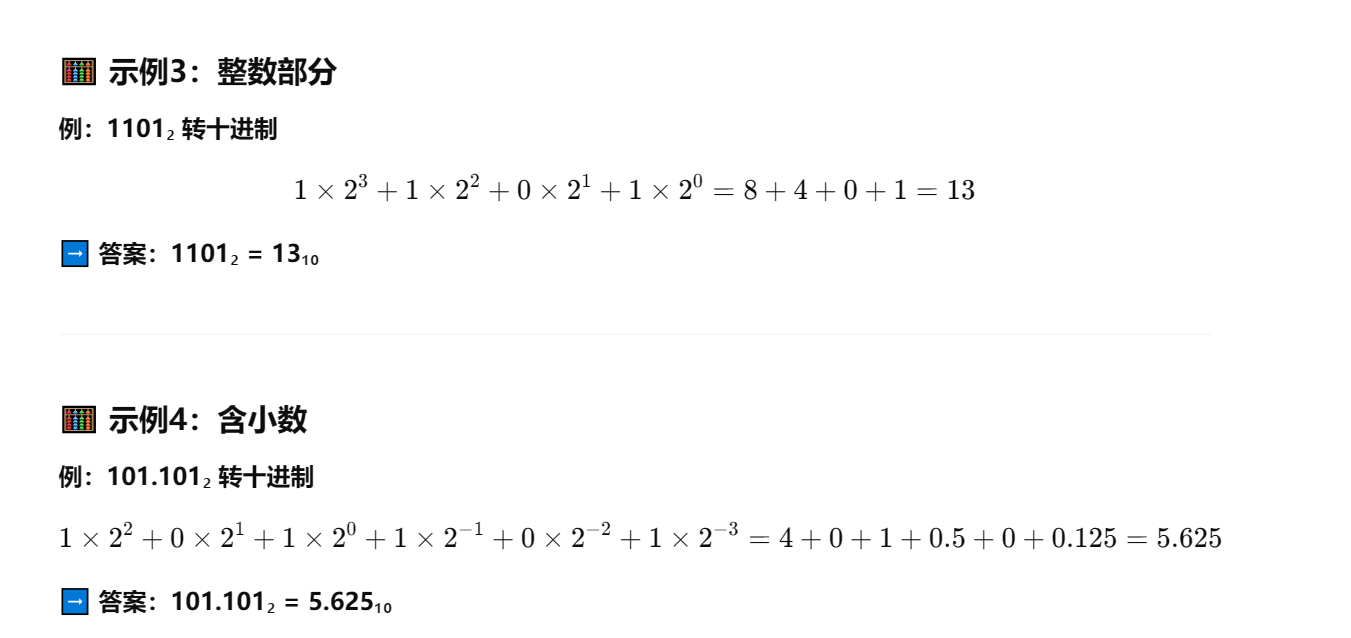

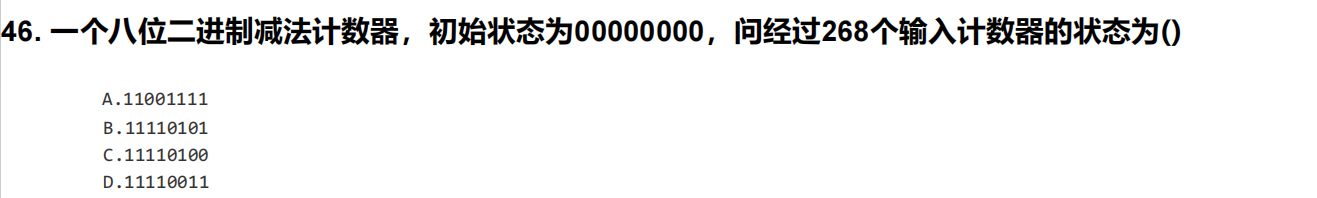

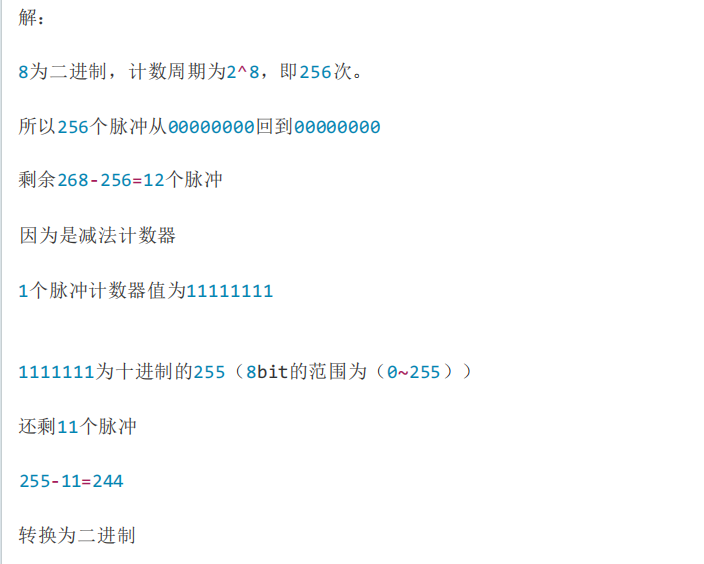

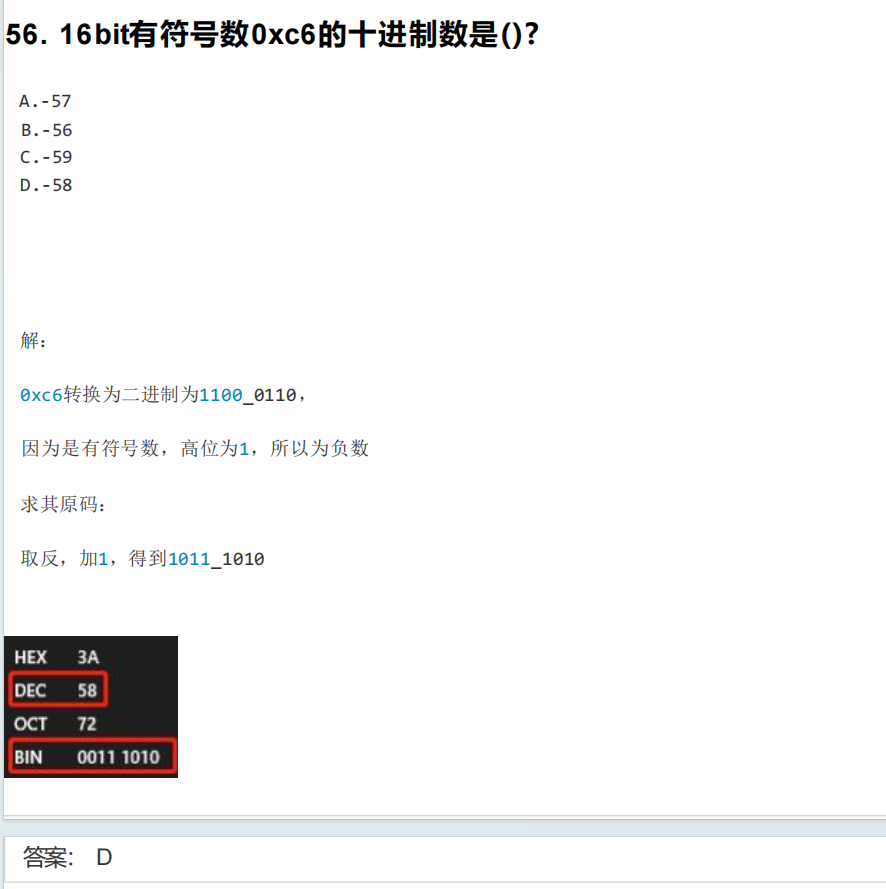

十进制与二进制的转换

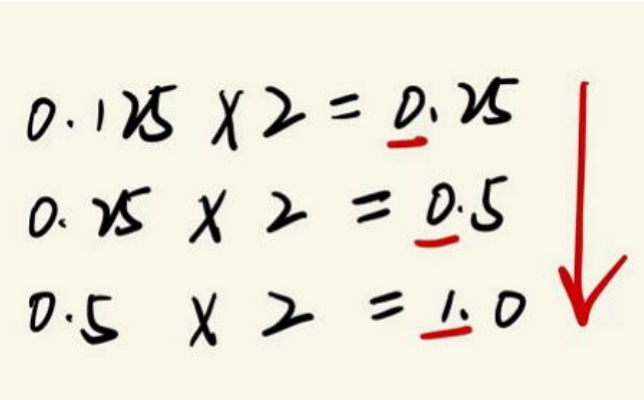

二进制转换为十进制

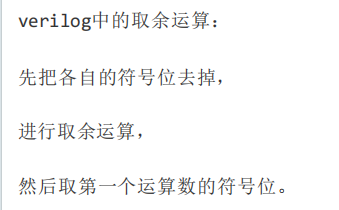

verilog取余运算

缺省值

wire线网型未赋值为z

reg寄存器类型未赋值为x

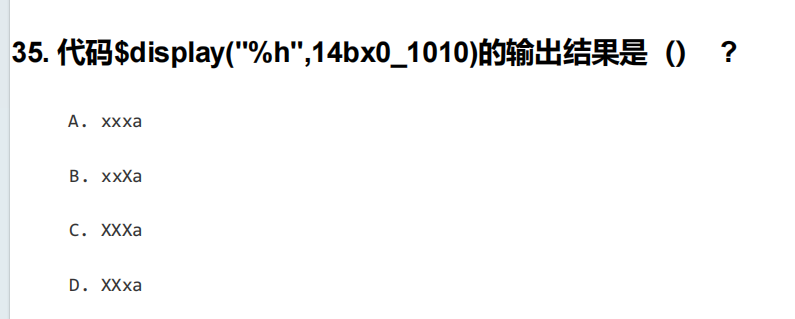

代码输出结果

14'bx0_1010展开为14'bxx_xxxx_xxx0_1010

所以输出结果为xxXa

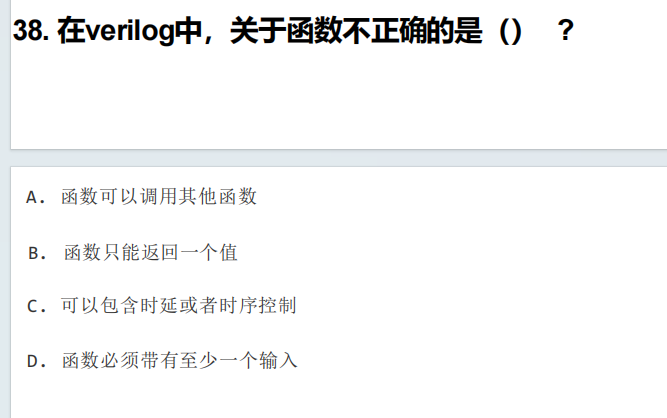

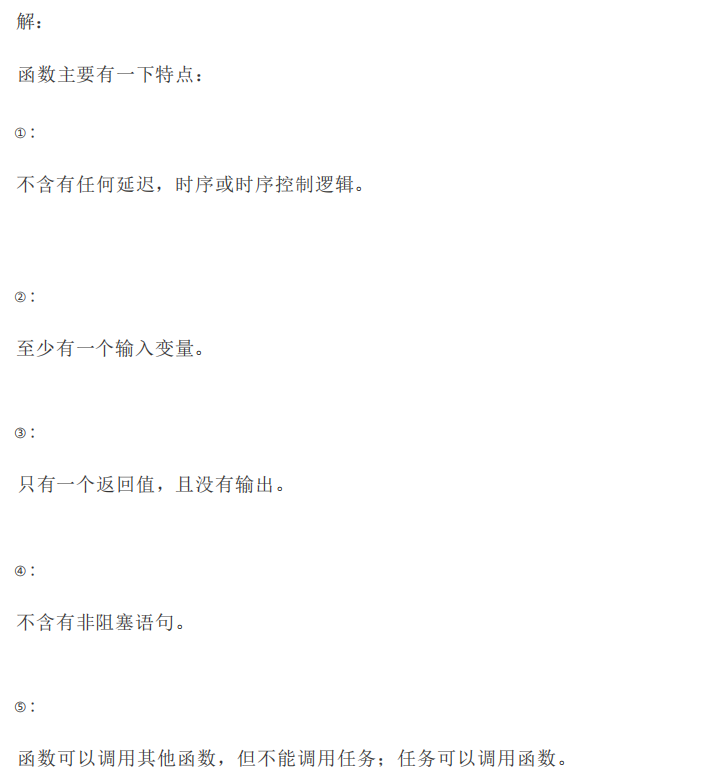

函数

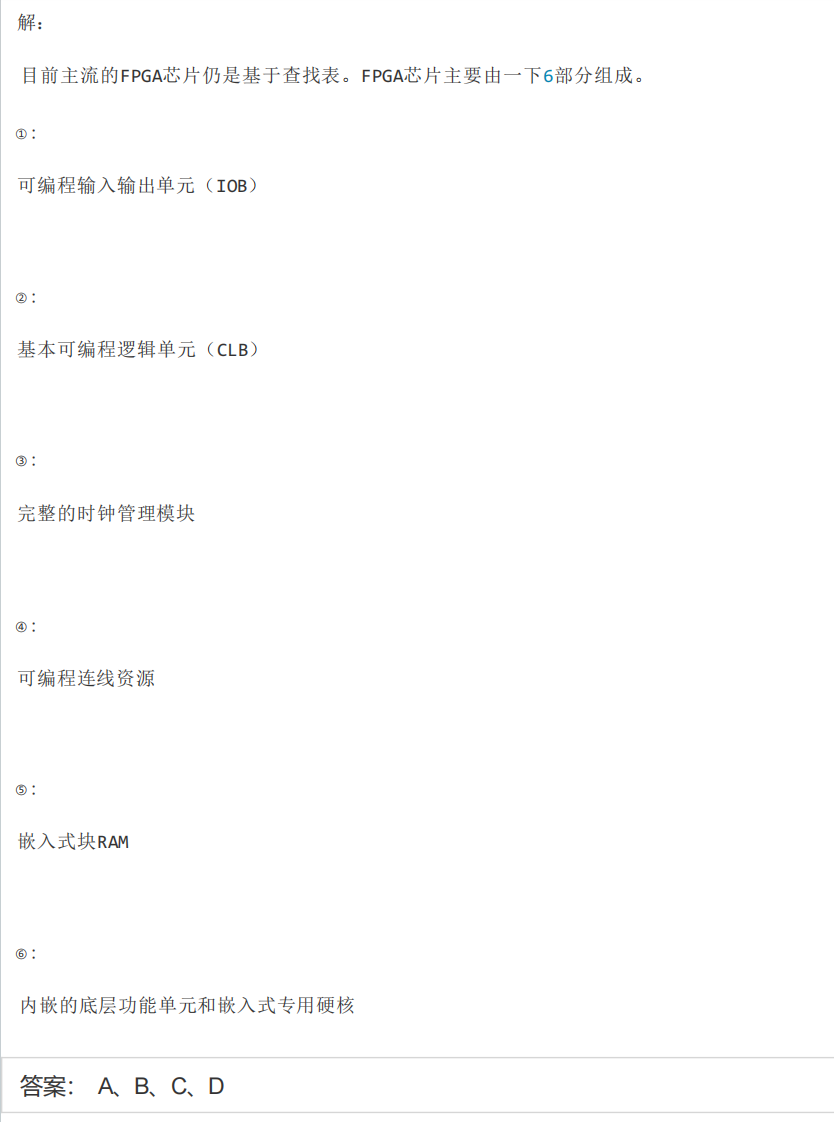

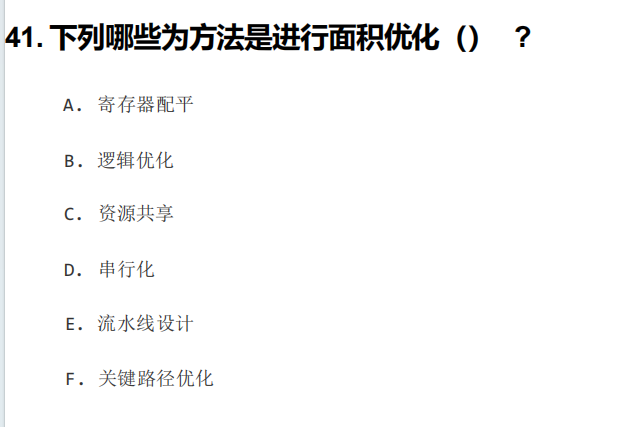

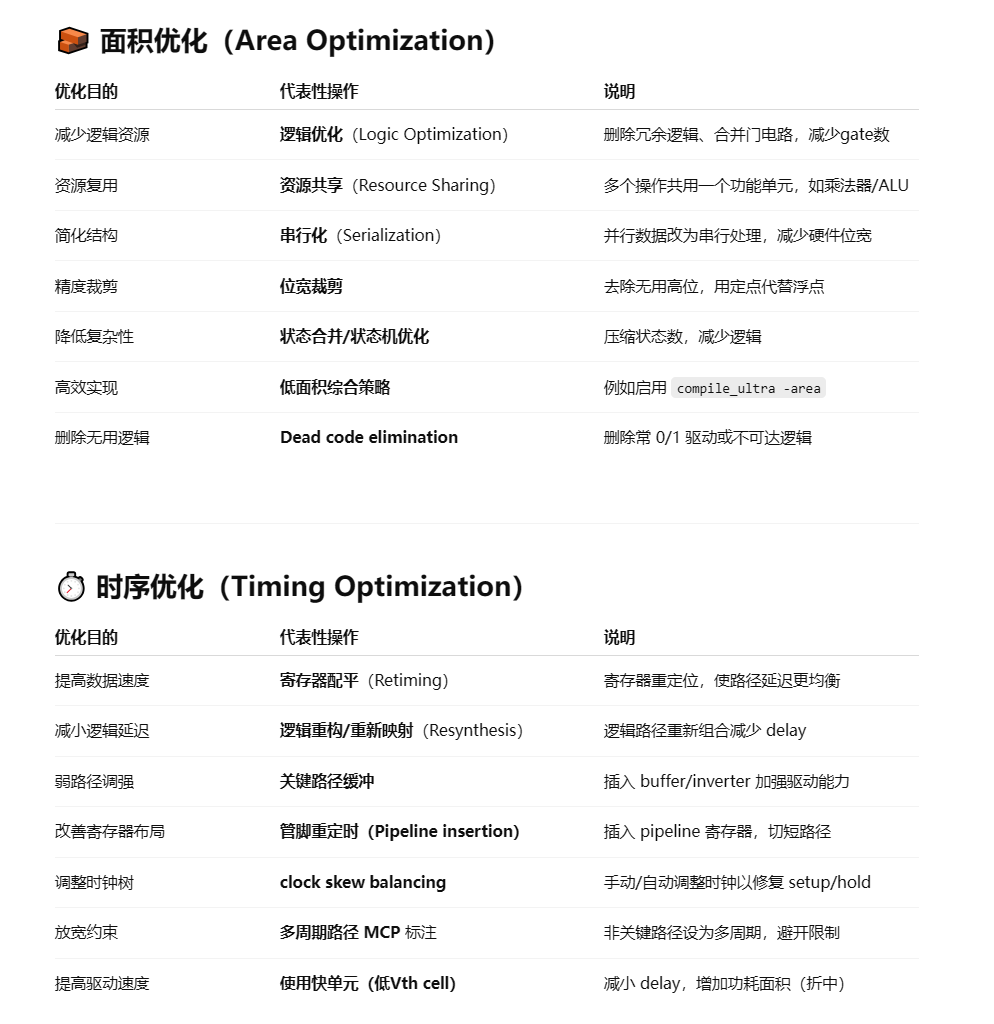

面积优化与时序优化

答案:BCD

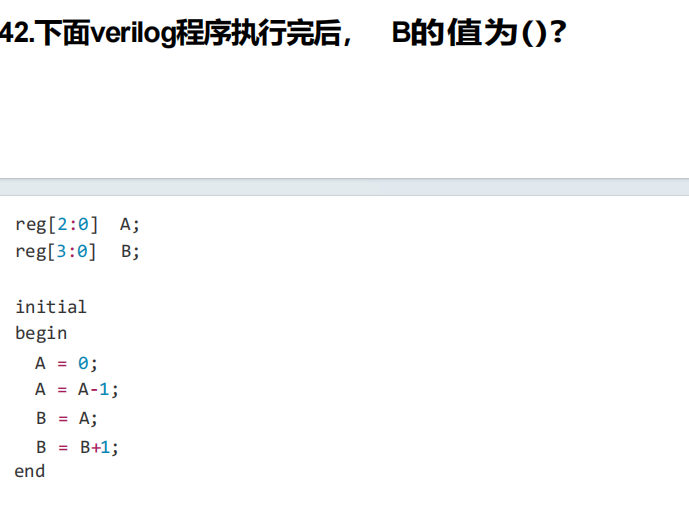

无符号数在verilog中用补码计算

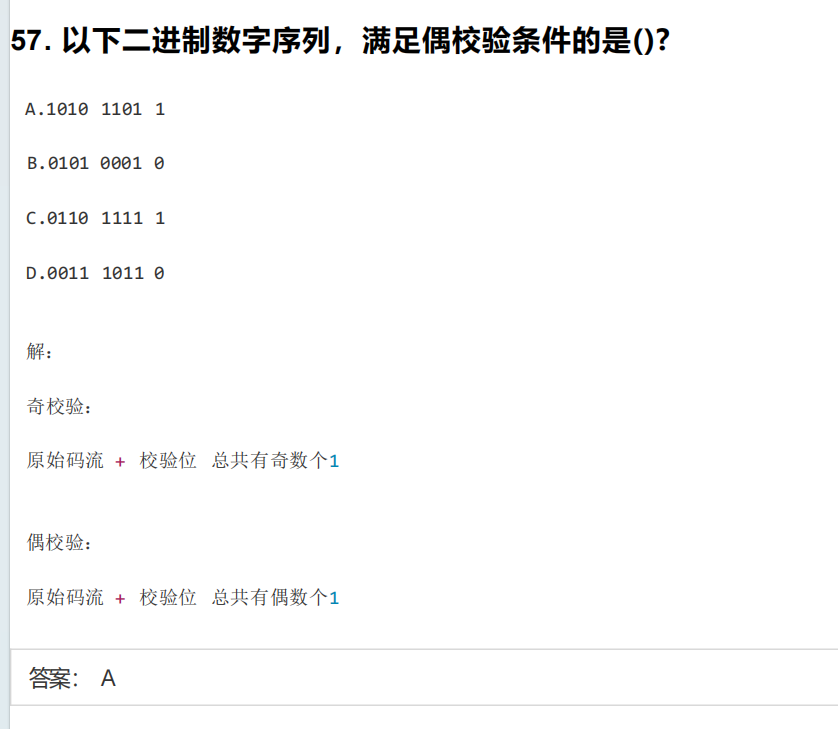

奇校验和偶校验

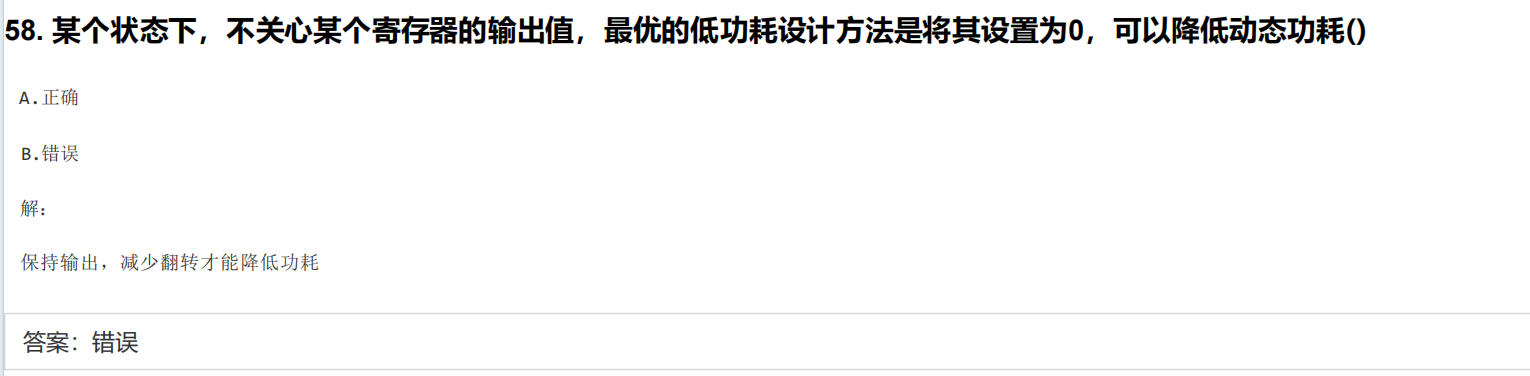

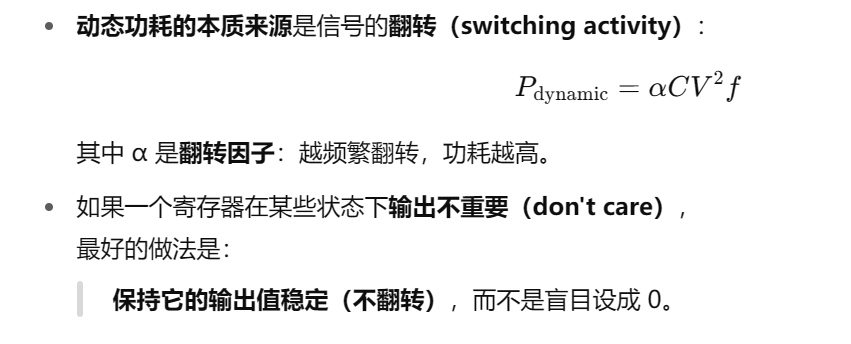

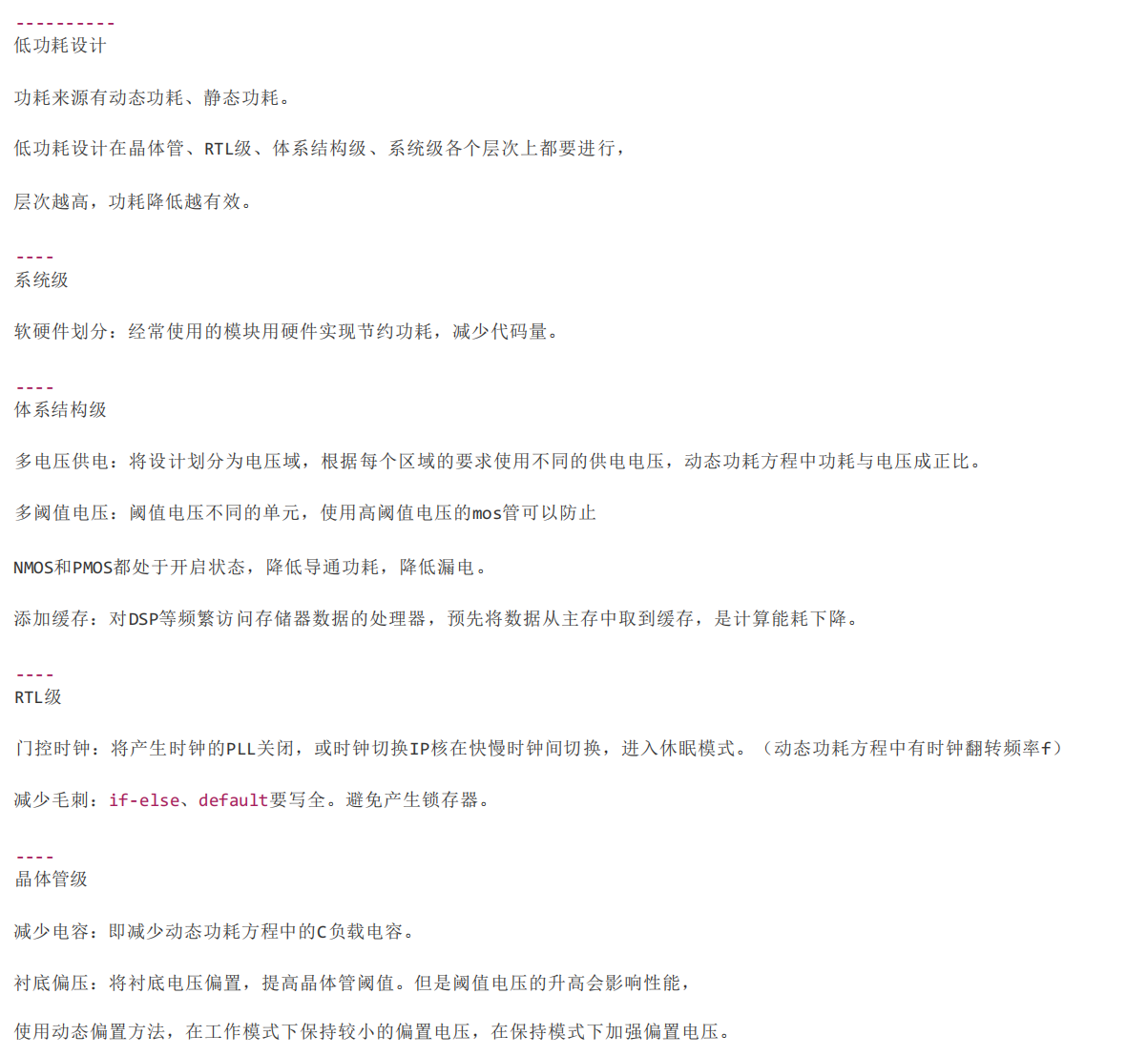

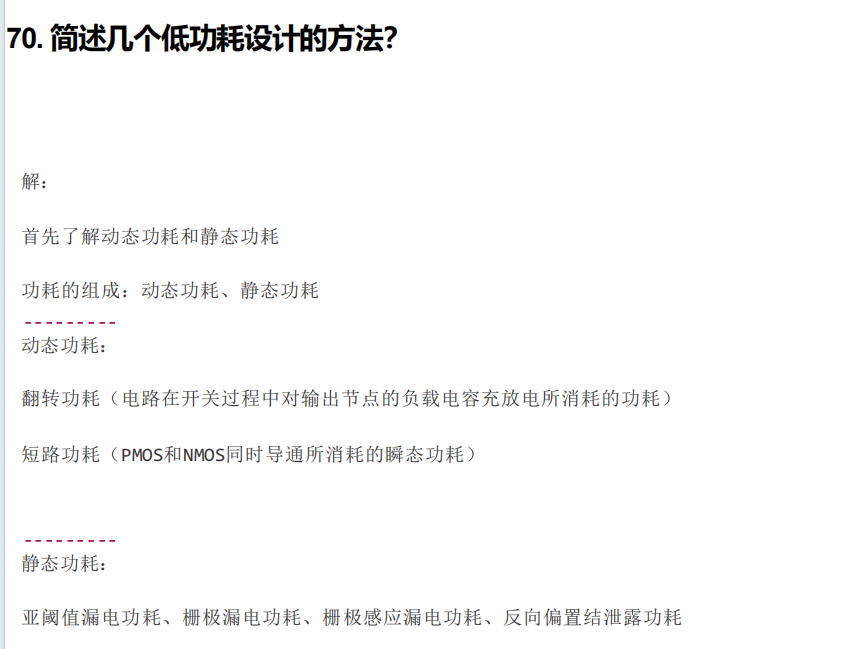

动态功耗和静态功耗

流水线设计

这道题考查的是流水线设计的优点,我们来逐项分析:

✅ 正确答案:B. 综合后电路的时钟频率可以更高

✅ 为什么是 B?

流水线的本质是把一个大逻辑功能拆成若干个小阶段,每个阶段之间用寄存器隔开。

这样做的核心优点是:

🚀 缩短每一级组合逻辑延迟 → 提高时钟频率

公式理解:

-

非流水线系统的周期时间:

Tclk=tlogic-total+tsetup T_{\text{clk}} = t_{\text{logic-total}} + t_{\text{setup}} Tclk=tlogic-total+tsetup

-

流水线系统将逻辑分成多段,新的周期时间是每段最大延迟 + setup:

Tclk=max(tstagei)+tsetup T_{\text{clk}} = \max(t_{\text{stage}i}) + t{\text{setup}} Tclk=max(tstagei)+tsetup

➡️ 因此能把一个原本慢的时钟周期,变为多个快时钟周期 ,时钟频率变高

❌ 为什么其他选项不对?

A. 面积更小 ❌

错误,流水线会引入额外的寄存器 → 面积反而上升

C. 复杂性更低 ❌

错误,设计上更复杂(需考虑数据相关、冒险、控制逻辑等)

D. 功耗更低 ❌

错误,由于增加寄存器+高频率,动态功耗通常更高

✅ 小结:

| 优点 | ✅ 提高时钟频率(性能 ↑) |

| 缺点 | 面积 ↑,功耗 ↑,复杂性 ↑ |

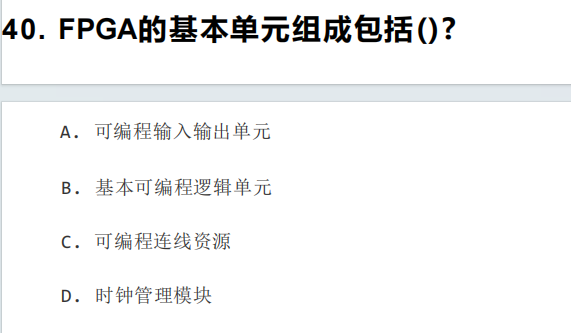

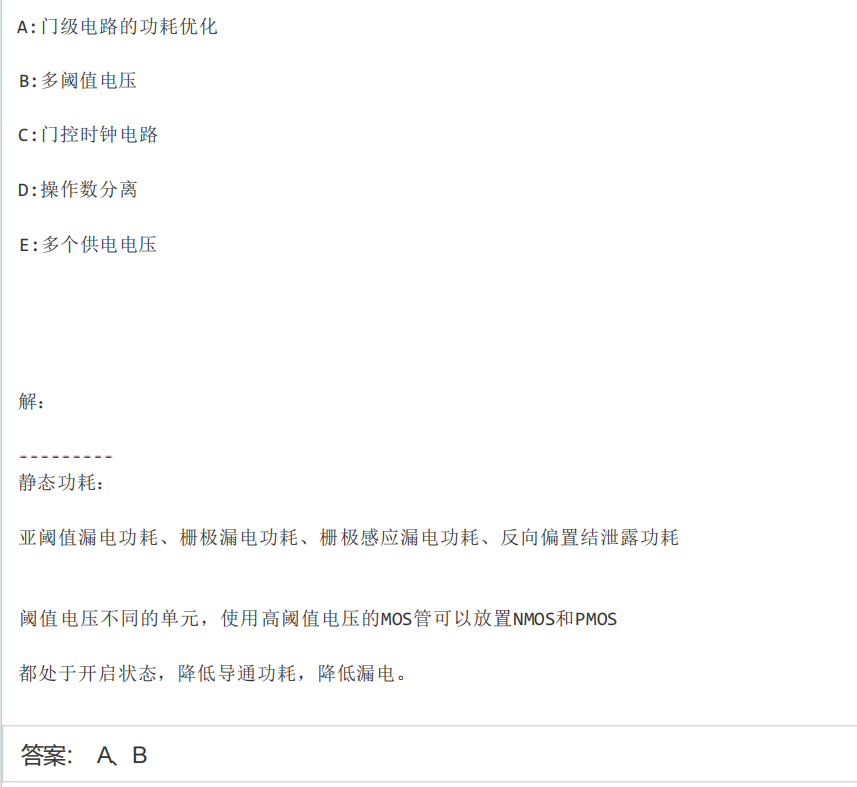

答案:ACD

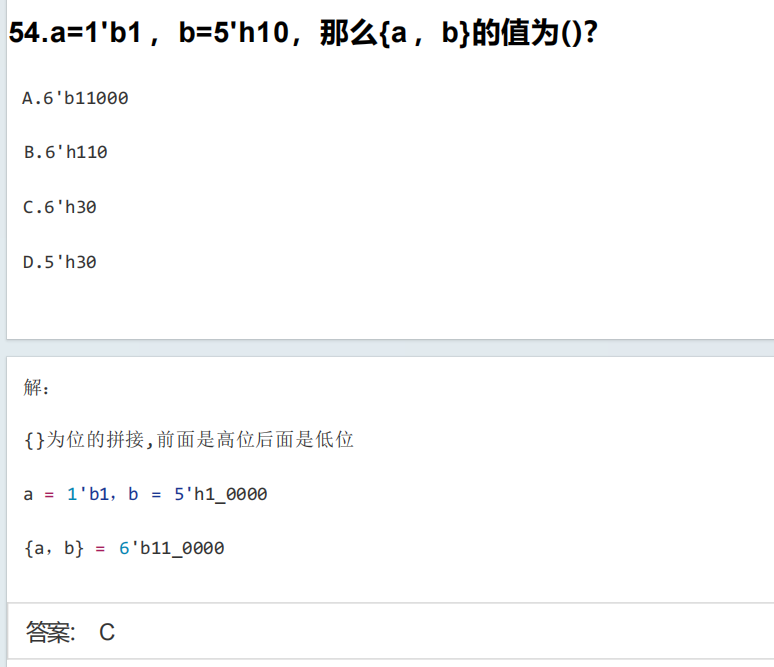

语法

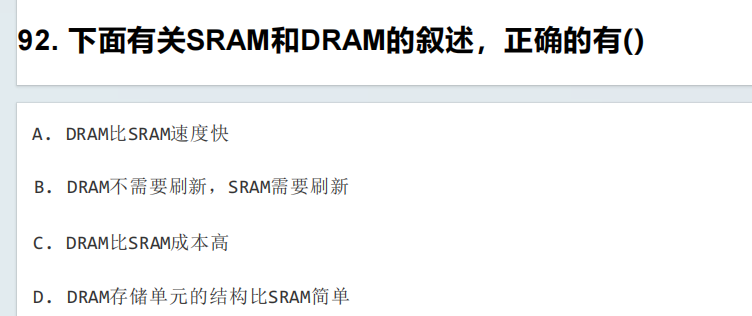

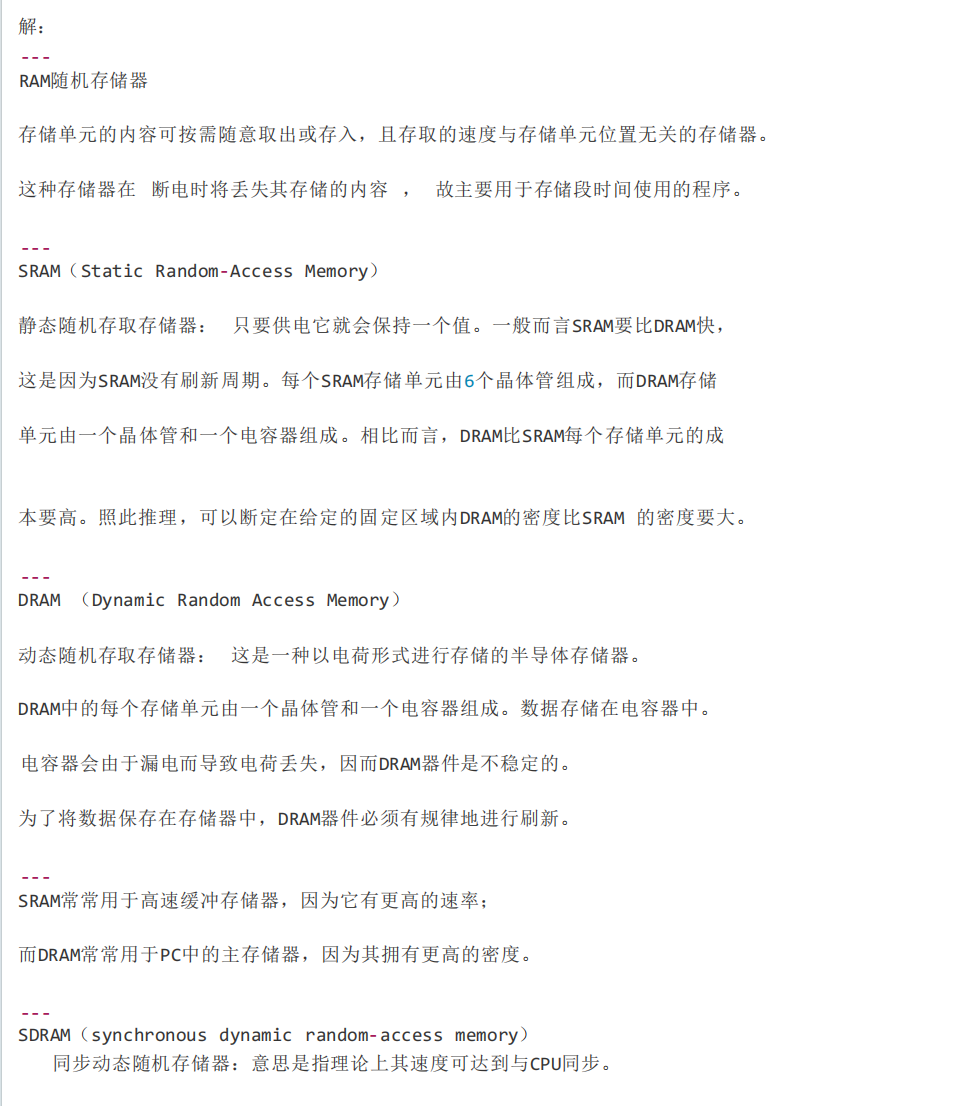

DRAM和SRAM