FPGA的LUT理解

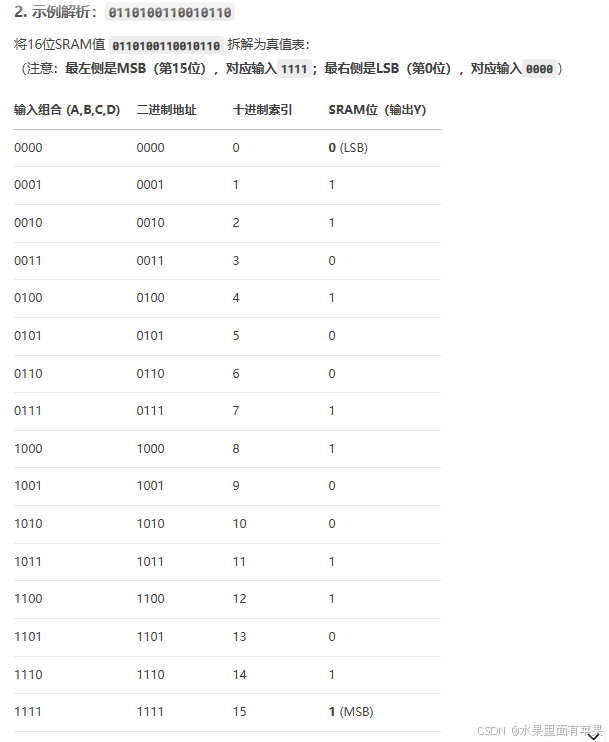

FPGA的4输入LUT中,SRAM存储的16位二进制数(如 0110100110010110)直接对应真值表的输出值。下面通过具体例子详细解释其含义:

1. 4输入LUT

4输入LUT的本质是一个16×1的SRAM,它通过存储真值表的方式实现任意4输入1输出的组合逻辑功能。

2. SRAM存储的真值表映射关系

4个输入(A,B,C,D) 组成16种可能的组合(0000到1111)。

SRAM的16位 按固定顺序存储每种输入组合对应的输出(0或1)。

地址映射规则(以Xilinx FPGA为例):

输入 A,B,C,D 被视为4位二进制数,最低位是D,最高位是A。

例如:A,B,C,D = 0101 → 二进制 0101 = 十进制 5 → 选择SRAM的第5位(从0开始计数)。

3. 实例解析

3. 对应的逻辑函数

观察真值表:输出Y在特定输入组合时为1,其余为0。

实际功能:这个SRAM配置实现的是一个 自定义组合逻辑函数,例如:

当输入满足以下条件时,Y=1:

A,B,C,D = 0001(Y=1)

A,B,C,D = 0010(Y=1)

A,B,C,D = 0100(Y=1)

...(其他Y=1的情况)

4. 为什么这样设计?

灵活性:通过修改SRAM的值,无需改动电路即可改变逻辑功能。

例如:将 0110100110010110 改为 1111000011110000,LUT立即变为另一个函数。

硬件效率:SRAM的读写速度快,适合FPGA的动态配置需求。

标准化:所有4输入组合逻辑均可用同一LUT结构实现,简化FPGA架构设计。

5. 实际FPGA中的应用

综合工具:将Verilog代码转换为真值表并生成SRAM配置位。