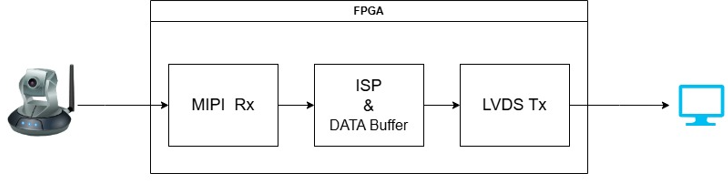

从Kintex-7到Versal:一段让我重新认识时序收敛的FPGA迁移之旅

摘要 :当一段在Kintex-7上稳定运行多年的MIPI Rx代码,迁移到Versal后开始随机出错,我没想到问题竟隐藏在一个看似"安全"的buffer逻辑中。这是一个关于时钟域、亚稳态和跨代FPGA架构差异的深度实战故事。

一、那个看似平静的迁移任务

去年,我们团队决定将一款成熟的视频处理产品从Xilinx Kintex-7平台迁移到新一代的Versal FPGA。升级理由很充分:更高的性能、更低的功耗、更丰富的资源。

"应该很简单,"我在项目启动会上说,"大部分代码是纯RTL,平台无关。"

我们的MIPI CSI-2接收模块在Kintex-7上稳定运行了三年,处理过数百万帧图像,从未出过问题。

受影响模块的主要部分是这样的:

verilog/ 原Kintex-7代码 - 32位转64位数据缓冲器

assign mipi_data_64 = {mipi_data, mipi_data_buf };

always @(posedge rx_sys_clk or posedge rx_sys_rst) begin

if(rx_sys_rst ) begin

mipi_data_vld_64 <= 1'b0;

end else if(mipi_data_vld ) begin

mipi_data_vld_64 <= mipi_data_vld_64 + 1'b1;

end else if(~mipi_data_vld ) begin

mipi_data_vld_64 <= 1'b0;

end

end

always @(posedge rx_sys_clk or posedge rx_sys_rst) begin

if(rx_sys_rst ) begin

mipi_data_buf <= 32'd0;

end else begin

mipi_data_buf <= mipi_data;

end

end

// mipi_data_vld_64 & mipi_data_64 : valid control signal and datat write into RAM 看起来没有问题,不是吗? 同一个时钟域,简单的使能逻辑,我在Kintex-7上验证过无数次。

二、幽灵般的数据错误

整个工程迁移到Versal后, 只需要更新下几个IP。本来以为一上板子测试,基本功能就应该正确,顶多屏幕会有一些闪烁等小问题,需要再调整一下参数。没想到打开电源,显示器上显示的影像不正确,从上到下都是花屏。

更诡异的是:

- 错误一直存在,即使配置sensor输出Colorbar

- 工程单独测试LVDS Tx , 输出正常

我们用嵌入式逻辑分析仪Reveal抓取了出错的时刻:

sensor_data_buf的数据并不完全是上一拍的sensor_data, 某些bit数据发生了改变,导致后续写进RAM的数据错误。verilog// 抓取到的错误波形(简化版)

verilog

// 抓取到的错误波形(简化版)

Time 123.4ms: mipi_data_vld=1, mipi_data=32'hAABBCCDD

Time 123.5ms: mipi_data_vld=1, mipi_data=32'hEEFF0011

// 期望输出: {32'hAABBCCDD, 32'hEEFF0011} = 64'hAABBCCDDEEFF0011

// 实际输出: {32'hEEFF0011, 32'hAABBCCDD} = 64'hEEFF0011AABBCCDDTime 123.4ms:

// mipi_data_64 期望输出: {32'hAABBCCDD, 32'hEEFF0011} = 64'hEEFF0011AABBCCDD

// mipi_data_64 实际输出: {32'hEEFF0011, 32'hAABBCCDD} = 64'hCEF30031AABBCCDD三、理论根源:建立/保持时间窗口的物理现实

经过48小时的调试,我们把范围缩小到那个"简单"的buffer逻辑。问题出现在 mipi_data_buf的生成上。

上面代码意图很明确 :

- 每个时钟周期缓存当前的

mipi_data - 下一周期与新的

mipi_data拼接成64位 - 通过计数器标志每两个有效数据输出一次64位数据

但这里隐藏着三个致命假设 :

mipi_data在时钟边沿是稳定的mipi_data_buf总能采样到正确的值- 数据变化与时钟边沿完美错开

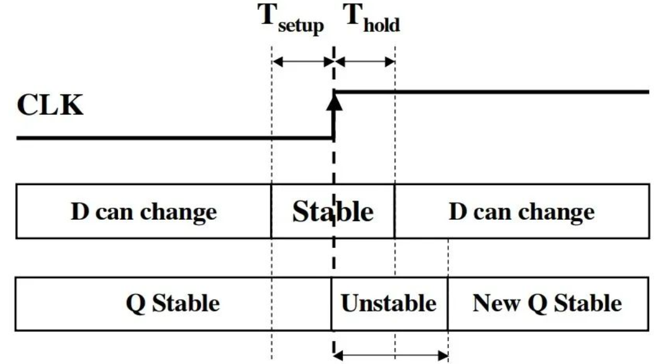

3.1 触发器的采样机制

每个D触发器都有一个 绝对不可侵犯的禁区 ------建立时间(Tsu)和保持时间(Th)窗口:

数学定义 :

- 建立时间 Tsu:时钟边沿前数据必须稳定的最小时间

- 保持时间 Th:时钟边沿后数据必须稳定的最小时间

- 采样窗口 W = Tsu + Th:数据绝对禁止变化的区域

对于Versal FPGA,典型的时序参数:

text

Tsu ≈ 0.2ns @ 400MHz

Th ≈ 0.1ns @ 400MHz

采样窗口 W ≈ 0.3ns3.2 问题的物理本质

当 mipi_data的变化边缘进入这个0.3ns的采样窗口时,触发器可能:

- 正确采样 :变化完全在窗口外

- 亚稳态 :变化在窗口边缘

- 错误采样 :变化穿过整个窗口

在您的代码中,mipi_data_buf <= mipi_data的 危险在于 :

mipi_data可能在任何时刻变化- 触发器在每个时钟边沿都会尝试采样

- 一旦变化与边沿"相遇",灾难就发生了

四、具体错误场景还原

场景1:单次变化跨越采样窗口

结果:

mipi_data_buf可能采样到:

1. 全部旧值(幸运)

2. 全部新值(幸运)

3. 部分旧值+部分新值(灾难!)场景2:与mipi_data_vld计数器的时序竞争

这才是 最隐蔽的问题 :

// 关键时序关系:

always @(posedge rx_sys_clk) begin

mipi_data_buf <= mipi_data; // 时序路径A

if(mipi_data_vld) begin

mipi_data_vld_64 <= ...; // 时序路径B

end

end问题链 :

-

mipi_data_vld在时钟边沿有效 -

mipi_data_vld_64计数器递增,表示"可以输出64位数据" -

但此时

mipi_data_buf可能采样到错误值 -

结果:计数器说"数据有效",但数据是错的

时间轴:

t0: 时钟边沿n

mipi_data_vld = 1

mipi_data = 值A(稳定)t1: 时钟边沿n+1

mipi_data_buf应该=值A

但mipi_data正在变为值B!如果变化在采样窗口内: mipi_data_buf = 亚稳态值Xt2: 输出阶段

mipi_data_64 = {值B, 值X} ← 完全错误!

mipi_data_vld_64 = 1 ← 但标志有效!

五、修复问题的理论框架 -- 同步设计的黄金法则

5.1 数据-控制信号一致性定理

定理 :对于任何使用使能信号的数据处理单元,数据信号和使能信号必须满足:

- 相同的时序参考(时钟域)

- 匹配的路径延迟

- 稳定的采样窗口

数学表达 :

设数据变化时间为 T_data_edge

设使能有效时间为 T_enable_valid

安全条件:

|T_data_edge - T_enable_valid| > max(Tsu, Th) + margin5.2 数据缓冲器的正确范式

把mipi_data_buf生成代码更新为如下后,上版测试功能正常。

always @(posedge rx_sys_clk or posedge rx_sys_rst) begin

if(rx_sys_rst ) begin

mipi_data_buf <= 32'd0;

end else begin

if(mipi_data_vld) begin

mipi_data_buf <= mipi_data;

end

end

end推荐更优方案:使能控制采样

always @(posedge rx_sys_clk or posedge rx_sys_rst) begin

if(rx_sys_rst ) begin

mipi_data_buf <= 32'd0;

end else begin

mipi_data_buf <= mipi_data;

end

end

// 相应的,修改有效标志逻辑

reg data_phase; // 0:低32位, 1:高32位

always @(posedge rx_sys_clk or posedge rx_sys_rst) begin

if(rx_sys_rst) begin

data_phase <= 1'b0;

mipi_data_vld_64 <= 1'b0;

end else if(mipi_data_vld) begin

if(data_phase) begin

// 第二个32位到达,输出64位

mipi_data_64 <= {mipi_data, mipi_data_buf};

mipi_data_vld_64 <= 1'b1;

end else begin

// 第一个32位,仅缓存

mipi_data_vld_64 <= 1'b0;

end

data_phase <= ~data_phase;

end else begin

mipi_data_vld_64 <= 1'b0;

end

end六、深刻教训与设计哲学

6.1 重新认识"同步"

这个案例迫使我们重新思考"同步设计"的真正含义:

同步不仅仅是时钟域相同,更是时序关系的可预测性。

6.2 数据有效性的完整链条

正确的数据流应该形成 闭合的验证环 :

数据产生 → 有效性标记 → 安全传输 → 接收验证 → 使用确认在最初的原始设计中,链条在"安全传输"环节断裂了。

6.3 面向未来的设计原则

- 假设所有信号都是异步的 ,除非能证明同步

- 使能信号必须控制所有相关数据路径

- 关键数据路径需要冗余校验

- 设计必须考虑工艺、电压、温度的变化范围

结语:从漏洞到洞察

这个 mipi_data_buf的采样窗口问题,表面上是一个简单的时序违规,深层却揭示了数字电路设计的核心矛盾:

在追求更高性能(频率)的同时,我们如何保证数据的绝对可靠?

答案不在于更先进的工艺或更快的时钟,而在于 对物理现实的深刻尊重 ------尊重建立时间、尊重保持时间、尊重信号传播的每一个皮秒。

这个bug的价值,不仅在于修复了一个具体问题,更在于它教会我们:

真正的专业,体现在对那些"几乎不可能发生"的边缘情况的敬畏和处理。

每一次这样的调试经历,都是工程师认知体系的一次升级。当我们下次面对看似简单的 data_buf <= data时,我们会本能地问:

"这个采样安全吗?"

"变化窗口在哪里?"

"我需要什么样的保护?"

这,就是从错误中学到的最宝贵的东西。