需要整个50天学习FPGA资料的请联系博主

简介

硬件的功能验证用于验证所设计的电路的功能。但是,真实硬件中的模块具有逻辑元件和它们之间的路径带来的延迟。因此,必须检查电路是否满足延迟说明中指定的模块时序约束。随着电路尺寸变得越来越小且速度越来越快,检查时序约束变得越来越重要了,检查时序的方式之一是进行时序仿真,即在仿真过程中计算与该模块相关的延迟值。与时序仿真不同的另一种验证时序的技术已经出现在设计自动化行业中。最流行的技术是静态时序验证。设计者首先进行纯功能验证,然后用静态时序验证工具单独验证时序。静态验证的主要优点是能以比时序仿真快几个数量级的速度验证时序。静态时序验证是一个独立的研究领域,不做讨论。本章将详细讨论在Verilog模块中如何控制和定义时序和延迟。因此,通过使用时序仿真,设计者可以同时验证Verilog描述的电路的功能和时序。

学习目标

●鉴别Verilog仿真中用到的延迟模型的类型,分布延迟、集总(lumped)延迟和引脚到引脚(路径)的延迟。

●理解如何在仿真过程中用specify块设置路径延迟。

●能解释输入和输出引脚之间的井行连接和全连接。

●理解如何在 specify块中用 specparam 语句定义参数.

●描述状态依赖路径延迟,即条件路径延迟。

◆能解释 rise,fall 和 tum-off 延迟,理解如何设置 min,max 和 typ 的值。

●能够为时序检查定义系统任务,setup、hold 和$width。

◆理解延迟反标.

延迟类型

在Verilog中有三种类型的延迟模型:分布延迟、集总延迟和引脚到引脚(路径)的延迟。、

分布延迟

分布延迟是在每个独立元件的基础上进行定义的。延迟值赋给电路中独立的元件。图显示了模块M中分布在每个逻辑元件上的廷迟。分布延迟可以通过两种方式建模:一种是将延迟值赋给独立的门;另一种是在单独的assign语句中指定延迟值。任意一个门的输入发生变化时,该门的输出在指定的延迟值之后改变。显示出如何在门元件中和数据流描述中说明分布延迟。

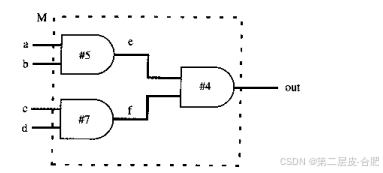

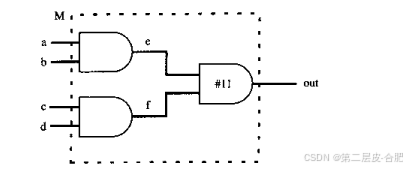

集总延迟

集总延迟是在每个独立模块的基础上定义的。它们可以被看成是模块输出门的单个延迟,而实际上是将所有路径累积的延迟汇总于输出门这一处,因此称为集总廷迟.图1和例 中给出了集总延迟的示例。 是图的改进。本例中,我们计算图中从任意输人到输出的最大延迟,即7+4=11个单位延迟。整个延迟汇总到输出门。当模块M的任意输人发生变化时,经过这个最大延迟之后,输出发生改变。

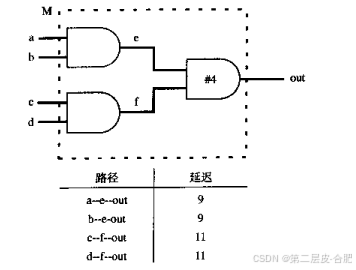

引脚到引脚的延迟

另一种对模块的延迟定义方式是引脚到引脚的时序说明,分别把延迟赋给模块中从每个输入到每个输出之间的所有路径。因此,可以针对每条输人/输出路径分别指定延迟。在图中采用图中的示例并给每条输入/输出路径计算引脚到引脚的延迟。

时序检查

讨论了如何指定路径延迟。指定路径延迟的目的是以比门延迟更高的精度仿真实际数字电路的时序。本节将描述如何建立时序检查,以便查看仿真过程中是否违反了时序约束。

对于时序严格的高速时序电路,如微处理器,时序验证尤其重要。Verilog提供了系统任务来进行时序检查。Verilog有很多用于时序检查的系统任务。我们将探讨3种最通用的时序检查®任务:setup,hold 和$width。所有的时序检查只能用在 specify 块里。为了简化讨论,省略了这些时序检查系统任务的一些可选参数。

setup 和hold 检查

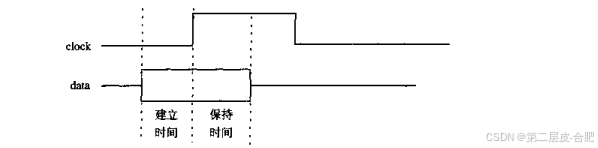

setup和hold任务用来检查设计中时序元件的建立和保持约束。在时序元件(如边沿触发的触发器)中,建立时间是数据必须在有效时钟边沿之前到达的最小时间。保持时间是数据在有效时钟边沿之后保持不变的最小时间。

$width 检查

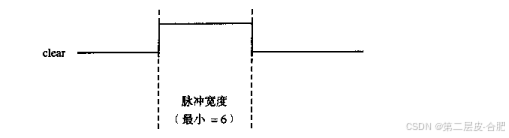

有时有必要检查脉冲宽度。

系统任务$width 用来检查脉冲宽度是否满足最小宽度要求

延迟反标注

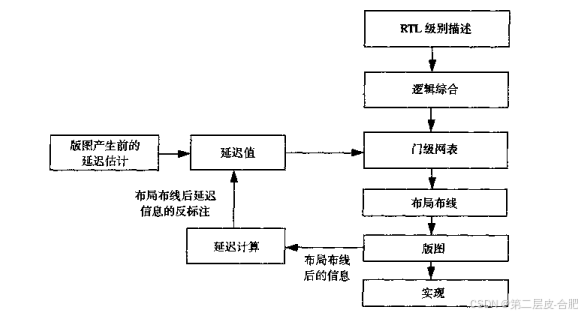

在时序仿真中延迟反标注是重要而庞大的课题。。然而,将给设计者介绍仿真中延迟的反标注概念。该课题的详细论述超出了本书范围,详细内容可参考 IEEE Standard Verilog Hardware Description Language 文档。在流程中使用延迟反标注的步骤如下:

1.设计者写RTL描述,然后进行功能仿真。

2.用逻辑综合工具将RTL描述转换成门级网表.

3.设计者用延迟计算器和IC制造工艺信息获取芯片制作版图前的延迟估计。然后,设计者

进行门级网表的时序仿真或者静态时序验证,使用这些初步的估计值检查门级网表是否

满足时序约束。

- 然后用布局布线工具将门级网表转换成版图。根据版图中的电阻R和电容C信息,计算

制作版图后的延迟值。R和C信息是根据几何形状和 IC 制造工艺提取的。

5.将制作版图后得到的延迟值反标注到门级网表中,以便更精确地修改门级网表的廷迟估

计。再次运行时序仿真或者静态时序验证,以便检查门级网表是否仍然满足时序约束。

6.如果要改变设计来满足时序约束,设计者必须返回RTL级,优化设计的时序,然后重复

从步骤2到步骤5的操作。